MATLAB 関数からの IP コアの生成入門

この例では、MATLAB® HDL ワークフロー アドバイザーを使用して、FPGA ボード上の LED を点滅させるカスタマイズした IP コアを生成する方法を示します。この例では生成された IP コアを ZedBoard ハードウェアに展開しますが、任意の Xilinx® Zynq® プラットフォームまたは MicroBlaze プロセッサを搭載した Xilinx FPGA を使用できます。

はじめに

MATLAB を使用して、アプリケーションの設計、シミュレーション、検証、アルゴリズムを使用した what-if シナリオの実行、パラメーターの最適化を行うことができます。次に、FPGA ボードでのハードウェア実装とソフトウェア実装用にアプリケーション設計を準備し、プログラム可能なロジックで実行する要素と、プロセッサで実行する要素を決定できます。

この例では以下を実行できます。

Zynq ハードウェアとツールを設定します。

ハードウェア実装とソフトウェア実装用に設計を確認します。

HDL Coder を使用して MATLAB アルゴリズムを HDL コードに変換します。

MATLAB HDL ワークフロー アドバイザーを使用して HDL IP コアを生成します。

IP コアを Zynq ハードウェアに展開します。

また、この IP コアを他の設計やプロジェクトで使用して、その機能に基づいて強化および構築することもできます。

前提条件

Xilinx Vivado® をインストールします。サポートされているバージョンのリストについては、HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアを参照してください。

関数

hdlsetuptoolpathを使用して、インストールされたターゲット デバイス向けの合成ツールへのパスを設定します。MATLAB コマンド ウィンドウで次のコマンドを使用します。その際、必ずパスを実際のインストール パスに置き換えてください。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',vivadopath);

ZedBoard を設定します。詳細については、Simulink モデルからの IP コアの生成入門の「Zynq ハードウェアとツールの設定」セクションを参照してください。

この例では、ZedBoard に関数

mlhdlc_ip_core_led_blinkingを実装します。関数のローカル コピーを開いて保存します。

open mlhdlc_ip_core_led_blinking.mMATLAB テスト ベンチのローカル コピーを開いて保存します。

open mlhdlc_ip_core_led_blinking_tb.mハードウェア実装とソフトウェア実装用の設計の確認と分割

MATLAB アルゴリズムから IP コアを生成して展開するには、以下の 3 つのコンポーネントが必要です。

ハードウェアで実行される MATLAB 関数。

MATLAB で関数設計を実行する MATLAB テスト ベンチ。

ハードウェア上の展開済みの MATLAB 関数のプロトタイプを作成する MATLAB スクリプト。MATLAB を使用したプロトタイピングはオプションですが、IP コア検証の追加手段が得られます。

設計を効果的に実装するには、以下を行う必要があります。

プログラム可能なロジックに適したアルゴリズムの部分と、ARM® プロセッサに適した部分を区別する。

プログラム可能なロジック用のアルゴリズムの部分を MATLAB 関数にグループ化する。

ハードウェアとソフトウェアの分割用の境界として MATLAB 関数を使用する。

HDL Coder を使用してこの関数の MATLAB コードをプログラム可能なロジックに実装する。

関数 mlhdlc_ip_core_led_blinking を開いて、どのように分割するかを検討します。

open mlhdlc_ip_core_led_blinking.mこの関数は、FPGA ボード上の LED を点滅させるカウンターをモデル化します。2 つの入力 Blink_frequency および Blink_direction があります。これらの入力により、LED の点滅頻度および方向が決定されます。出力 LED がボード上の LED ハードウェアに接続され、出力 Read_back がカウント値に設定され、プロセッサに読み戻すことができます。

mlhdlc_ip_core_led_blinking_tb テスト ベンチを開いて、関数設計がどのように実行されるのかを調べます。

open mlhdlc_ip_core_led_blinking_tb.mテスト ベンチは、mlhdlc_ip_core_led_blinking 関数に対する入力条件の範囲を示します。

MATLAB HDL Coder プロジェクトの作成

MATLAB コマンド ウィンドウで次のコマンドを入力して、HDL Coder プロジェクトを作成します。

coder -hdlcoder -new blinkingLEDmatlab

MATLAB HDL Coder プロジェクトの作成と入力に関する包括的なチュートリアルについては、Generate HDL Code from MATLAB Algorithmsを参照してください。

あるいは、[アプリ] タブで、[HDL Coder] をクリックします。[HDL コード生成] ペインで以下のようにします。

[MATLAB 関数] をローカルに保存されている MATLAB 関数

mlhdlc_ip_core_led_blinkingに設定します。[MATLAB テスト ベンチ] をローカルに保存されている MATLAB テスト ベンチ

mlhdlc_ip_core_led_blinking_tbに設定します。[MATLAB 関数] セクションで [型の自動定義] をクリックして入力の型を自動的に定義します。

[ワークフロー アドバイザー] をクリックします。

[ワークフロー アドバイザー] を使用して、固定小数点変換を実行します。

下のペインの [変数] タブの [推奨された型] 列で、「

numerictype(0, 24, 0)」と入力することで、変数freqCounterの推奨された型を符号なし 24 ビット整数に設定します。[固定小数点の変換] タスクを右クリックして [このタスクを実行] を選択します。

固定小数点変換の概要については、浮動小数点から固定小数点への変換を参照してください。

コード生成ターゲットの定義

MATLAB HDL ワークフロー アドバイザーを使用して、共有可能および再利用可能な IP コアを生成できます。HDL Coder と Xilinx Vivado IDE の統合により、FPGA 設計への生成された IP コアの組み込みが容易になります。

特定のハードウェア プラットフォーム用の IP コアを生成する方法の概要については、FPGA および SoC ハードウェアをターゲットにする方法の概要を参照してください。

MATLAB HDL ワークフロー アドバイザーを使用して IP コアの生成を実行します。

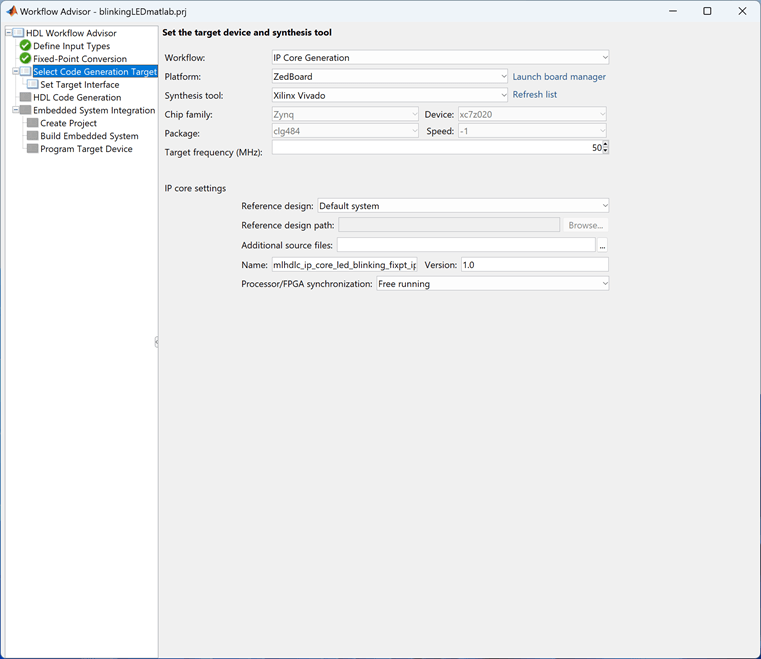

MATLAB HDL ワークフロー アドバイザーで [コード生成ターゲットを選択] をクリックします。

[ワークフロー] を

IP Core Generationに設定します。

プラットフォームの指定

生成された IP コアをリファレンス設計に統合するために、[プラットフォーム] をターゲット プラットフォームに設定します。

Generic Xilinx Platform: これは、汎用 Xilinx IP コアを生成する、ボードに依存しないオプションです。ただし、IP コアを既存の Xilinx Vivado プロジェクトに手動で統合する必要があります。

ボード固有のプラットフォーム: これらのオプションは Xilinx ボードに固有であり、IP コアを事前定義のリファレンス設計に統合します。この統合では、組み込みシステム ツールとして IP インテグレーターを搭載した Xilinx Vivado が使用されます。

この例では、ZedBoard プラットフォームをターゲットにします。以下のパラメーターを設定します。

[プラットフォーム] を

ZedBoardに設定します。[合成ツール] を

Xilinx Vivadoに設定します。[ターゲット周波数 (MHz)] を

50に設定します。[IP コア設定] で [リファレンス設計] を

Default systemに設定します。

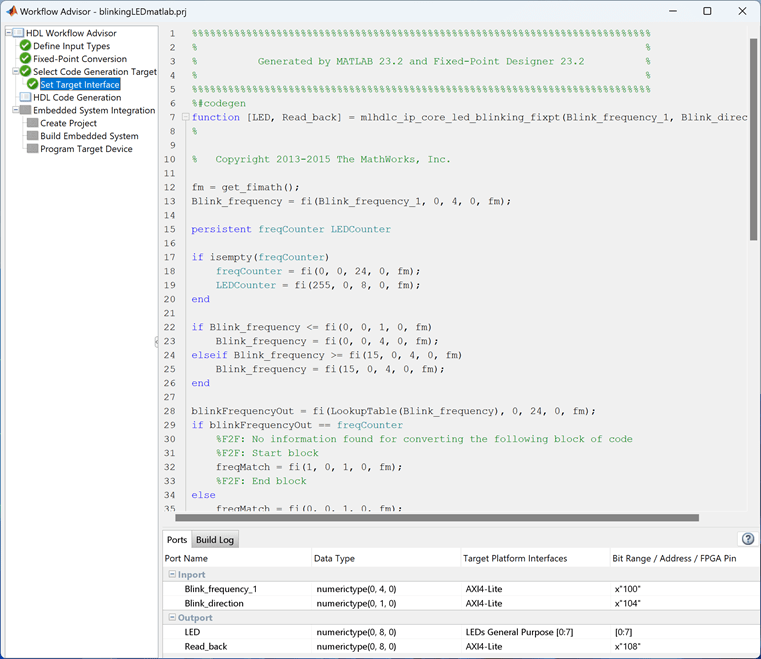

ターゲット インターフェイスの構成

次に、[ターゲット インターフェイスを設定] サブタスクを使用して、MATLAB 設計関数内の各入出力を IP コアのターゲット インターフェイスのいずれかにマッピングします。

この例では、入力 Blink_frequency と Blink_direction を出力 Read_back と共に AXI4-Lite インターフェイスにマッピングします。HDL Coder はそれらに対して AXI でアクセス可能なレジスタを生成します。LED 出力を、ZedBoard の LED ハードウェアに接続された外部インターフェイス LEDs General Purpose [0:7] にマッピングします。

下のペインの [端子] タブの [ターゲット プラットフォーム インターフェイス] 列で、変数

Blink_frequency、Blink_direction、およびRead_backのターゲット プラットフォーム インターフェイスをAXI4-Liteインターフェイスに設定します。下のペインの [端子] タブの [ターゲット プラットフォーム インターフェイス] 列で、変数

LEDのターゲット プラットフォーム インターフェイスをLEDs General Purpose [0:7]外部インターフェイスに設定します。[ターゲット インターフェイスを設定] サブタスクを右クリックし、[選択したタスクまで実行] を選択します。

IP コアおよび IP コア レポートを生成するには、[HDL コード生成] タスクを右クリックして [このタスクを実行] を選択します。

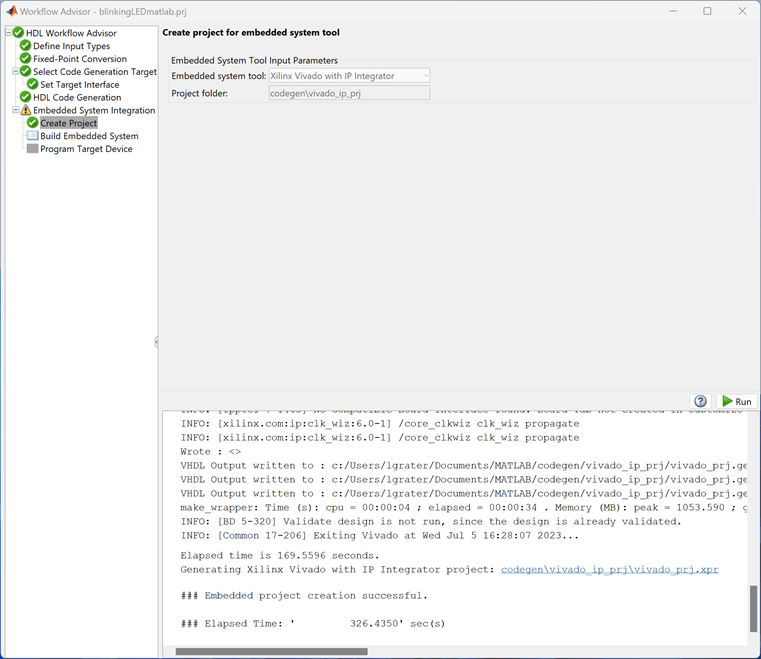

生成された IP コアと Xilinx Vivado 環境の統合

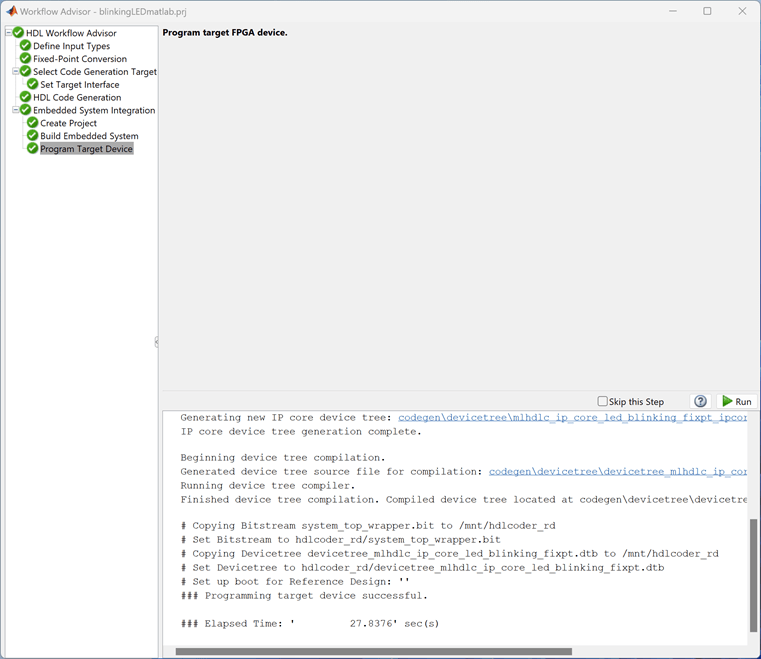

IP コアを生成した後に、MATLAB HDL ワークフロー アドバイザー内で、その IP コアをリファレンス設計と統合してから、ビットストリームを合成して FPGA にダウンロードします。

1. [組み込みシステムの統合] タスクで [プロジェクトを作成] サブタスクを右クリックし、[このタスクを実行] を選択します。IP インテグレーター組み込みシステム ツールを利用して IP コアを事前定義のリファレンス設計に統合する Xilinx Vivado プロジェクトが生成されます。ダイアログ ボックスに、Vivado でプロジェクトを開くためのリンクが含まれています。

2. [ソフトウェア インターフェイスを生成] サブタスクを右クリックして [このタスクを実行] を選択します。このサブタスクにより、インターフェイス スクリプト gs_mlhdlc_ip_core_led_blinking_fixpt_interface.m とセットアップ スクリプト gs_mlhdlc_ip_core_led_blinking_fixpt_setup.m が現在のフォルダーに生成されます。これらのスクリプトは、AXI でアクセス可能なレジスタに書き込むことで、生成されて展開された IP コアを設定し、そのインターフェイスとなります。生成されたハイパーリンクをクリックしてスクリプトを開きます。

メモ: インターフェイス ファイルとセットアップ ファイルは、選択した [プラットフォーム] にプロセッシング システムがある場合にのみ生成されます。[プラットフォーム] にプロセッシング システムがなければ、このサブタスクはスキップできます。

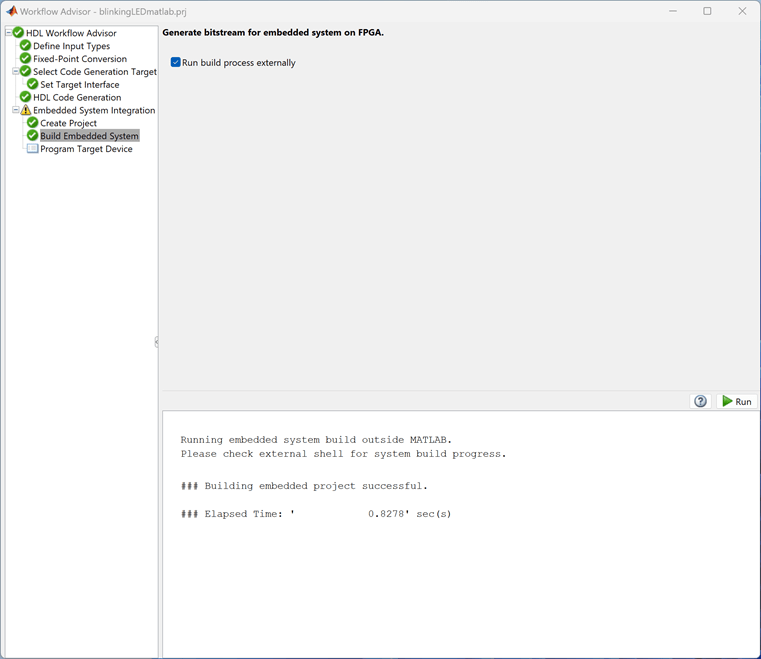

3. [組み込みシステムのビルド] サブタスクで [ビルド プロセスを外部で実行] を選択してから、[実行] をクリックします。Xilinx 合成ツールは MATLAB の外部の別プロセスとして実行されます。合成ツールが完了するまで待機します。

4. ビットストリームの生成後、[ターゲット デバイスをプログラム] サブタスクを右クリックし、[このタスクを実行] を選択して ZedBoard をプログラムします。FPGA ハードウェアをプログラムした後、ZedBoard で LED の点滅が始まります。

ハードウェアでの IP コアのプロトタイピングと検証

生成された IP コアを ZedBoard ハードウェアで検証するには、[ソフトウェア インターフェイスを生成] サブタスクで生成された MATLAB ファイル gs_mlhdlc_ip_core_led_blinking_fixpt_interface.m および gs_mlhdlc_ip_core_led_blinking_fixpt_setup.m を使用します。これらのファイルには、ハードウェアに接続して IP コアを操作する MATLAB コマンドが含まれています。

生成されたインターフェイス ファイル gs_mlhdlc_ip_core_led_blinking_fixpt_interface.m とセットアップ ファイル gs_mlhdlc_ip_core_led_blinking_fixpt_setup.m を開きます。これらのファイルは、HDL Coder プロジェクトが作成されたのと同じディレクトリにあります。

gs_mlhdlc_ip_core_led_blinking_fixpt_interface スクリプトは FPGA ハードウェアへの接続を確立し、gs_mlhdlc_ip_core_led_blinking_fixpt_setup 関数を使用してデータの読み書きができるようにします。スクリプトはそのために、[ターゲット インターフェイスを設定] サブタスクからのマッピングされた端子とインターフェイスを使用して fpga ハードウェア オブジェクトを構成します。

この関数を独自のスクリプトで再利用して、同じ構成を複製できます。たとえば、gs_mlhdlc_ip_core_led_blinking_fixpt_interface.m スクリプトで次の行のコメントを解除し、LED の点滅頻度を変更します。

% writePort(testFPGA, "Blink_frequency_1", 0);

変更したスクリプトを実行し、LED の点滅頻度がハードウェアで変更されるのを確認します。また、gs_mlhdlc_ip_core_led_blinking_fixpt_interface.m スクリプトで次の行のコメントを解除してからスクリプトを実行し、MATLAB ワークスペース内の変数 data_Read_back の変化を確認します。

% data_Read_back = readPort(testFPGA, "Read_back");

ホスト インターフェイス スクリプトの詳細については、FPGA I/O ホスト インターフェイス スクリプトの生成と管理を参照してください。