このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

イーサネットベースの AXI マネージャーを使用した IP コア生成ワークフロー

この例では、HDL Verifier™ Ethernet AXI マネージャー IP を使用して、HDL Coder™ 製品生成レジスタにアクセスします。AXI マネージャーは、MATLAB® から FPGA レジスタへの直接アクセスを提供します。

要件

Intel® Quartus® Prime(サポートされているバージョンはサポートされているEDAツールとハードウェアに記載されています)

Arrow® DECA MAX® 10 FPGA 評価キット

HDL Coder Support Package for Intel FPGA and SoC Devices

HDL Verifier Support Package for Intel FPGA Boards

USB-JTAGケーブル

クロスオーバーイーサネットケーブル

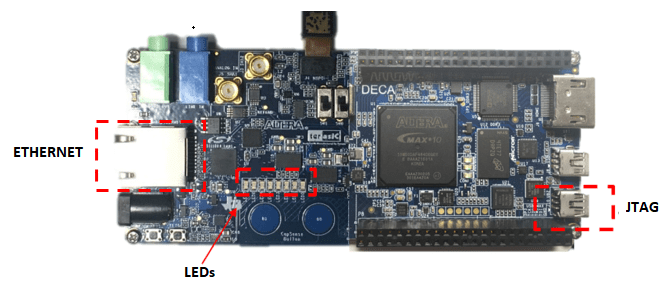

Arrow DECA MAX 10 FPGA 評価キット

この図は、Arrow DECA MAX 10 FPGA 評価キットを示しています。

リファレンスデザインの例

リファレンス デザインである AXI Manager - Ethernet は、読み取りおよび書き込み操作を発行するために MathWorks® IP と MATLAB コマンド ライン インターフェイスを使用します。このデザインを使用するには、HDL Verifier 製品が必要です。このリファレンス デザインの plugin_rd.m を以下に示します。

function hRD = plugin_rd() % Reference design definition

% Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Altera QUARTUS II');

hRD.ReferenceDesignName = 'AXI Manager - Ethernet (requires HDL Verifier)'; hRD.BoardName = 'Arrow DECA MAX 10 FPGA evaluation kit';

% Tool information hRD.SupportedToolVersion = {'17.1','18.1','19.1','20.1'};

%% Add custom design files % add custom Qsys design hRD.addCustomQsysDesign('CustomQsysPrjFile', 'system_soc.qsys'); hRD.CustomConstraints = {'system_soc.sdc','create_project_eth_deca.tcl'}; hRD.CustomFiles = {'phy_to_gmii'}; % Adding other files for custom IP core

% Add ip from support package msg = message('hdlcommon:plugin:IPRepositoryHDLVerifierAlteraNotFound',... '<a href="matlab:matlab.addons.supportpackage.internal.explorer.showSupportPackages({''HDLVALTERA''}, {''tripwire''});">download</a>').getString; hRD.addIPRepository('IPListFunction','hdlverifier.fpga.quartus.iplist','NotExistMessage', msg);

%% Add interfaces % add clock interface hRD.addClockInterface( ... 'ClockConnection', 'altpll_0.c0', ... 'ResetConnection', 'clk_0.clk_reset', ... 'DefaultFrequencyMHz', 50);

% add AXI4 slave interfaces hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', 'udp_axi_manager_0.axi4_udp', ... 'BaseAddress', '0x0000_0000', ... 'InterfaceType', 'AXI4'); % [ 'AXI4-Lite'| 'AXI4' ]

% Specify Embedded Coder Support Package to use for Software Interface hRD.EmbeddedCoderSupportPackage = hdlcoder.EmbeddedCoderSupportPackage.None; % [ None | Zynq | AlteraSoC ]

AXI マネージャー リファレンス デザインに対応する plugin_rd.m ファイルは、plugin_rd.m にあります。

IPコアワークフローの実行

リファレンス デザインは、DECA ボード上の LED を点滅させる HDL IP コアを生成します。次のデモンストレーションで使用されるファイルをこのパスで見つけます。

matlab/toolbox/hdlcoder/supportpackages/altera/+hdlipcore/+board/ArrowDECA

Ethernet AXI マネージャー IP を使用する AXI マネージャー - Ethernet リファレンス デザインの IP コア ワークフローを実行するには、次の手順に従います。このリファレンス デザインを使用すると、DECA ボード上の LED を点滅させる HDL IP コアを生成できます。HDL IP コアを生成するには、次の手順に従います。

1. Intel Quartus ツールパスを設定します。コマンドを実行するときに独自の Intel Quartus インストール パスを使用します。

hdlsetuptoolpath('ToolName','Altera QUARTUS II','ToolPath', ... 'C:\intelFPGA\20.1\quartus\bin64\quartus.exe');

2. MATLAB でこのコマンドを実行して、LED 点滅を実装する Simulink モデルを開きます。

open_system('hdlcoder_led_blinking')

3. led_counter サブシステムを右クリックし、HDL コード を選択してから HDL ワークフロー アドバイザー を選択し、hdlcoder_led_blinking/led_counter サブシステムから HDL ワークフロー アドバイザーを起動します。

4. ステップ 1.1 で、ターゲット ワークフロー として IP Core Generation を選択し、ターゲット プラットフォーム として Arrow DECA MAX 10 FPGA evaluation kit を選択します。[このタスクを実行] をクリックします。

5. ステップ 1.2 で、リファレンス デザイン として AXI Manager - Ethernet (requires HDL Verifier) を選択します。

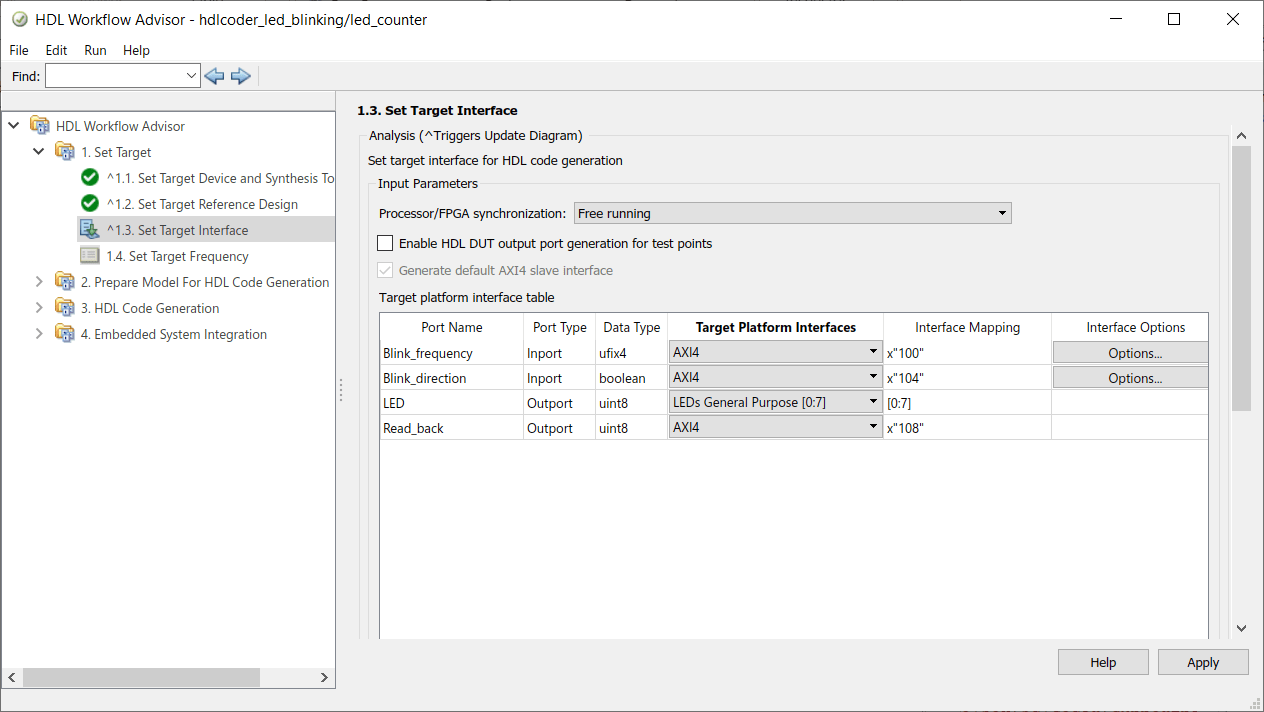

6. ステップ 1.3 では、Blink_frequency、Blink_direction、および Read_back ポートを AXI4 インターフェイスに割り当てます。LED ポートを LEDs General Purpose [0:7] に割り当てます。

7. ワークフローの残りの手順を実行して、ビットストリームを生成し、ターゲット デバイスをプログラムします。

この設計の Ethernet AXI マネージャー IP のデフォルトのターゲット IP アドレスは 192.168.1.2 で、デフォルトの UDP ポート値は 50101 です。ホスト マシンのネットワーク インターフェイス カード (NIC) をそれに応じて構成します。

IPコアレポートからアドレスを決定する

HDL Coder IP コアのベース アドレスは、リファレンス デザイン plugin_rd.m で定義されています。この設計では、ベース アドレスは 0x0000_0000 です。IP コア レポート レジスタ アドレス マッピング テーブルにオフセットが表示されます。

HDL Verifier AXI マネージャー - イーサネット コマンドライン インターフェイス

Intel FPGA ボード用の HDL Verifier サポート パッケージがあり、AXI Manager - Ethernet リファレンス デザインを選択した場合は、MATLAB コマンド ライン インターフェイスを使用して、HDL Coder 製品によって生成された IP コアにアクセスできます。

DDR メモリへの書き込みと読み取りを行うには、次の手順に従います。

1. AXI マネージャー オブジェクトを作成します。

h = aximanager('Intel','interface','PLEthernet','DeviceAddress','192.168.1.2')

2. 書き込みコマンドを発行します。たとえば、DUT を無効にします。

h.writememory('4',0)

3. DUT を再度有効にします。

h.writememory('4',1)

4. 現在のカウンター値を読み取ります。

h.readmemory('108',1)

参考

aximanager | writememory | readmemory