Bus Selector

入力バスから要素を選択する

ライブラリ:

Simulink /

Commonly Used Blocks

Simulink /

Signal Routing

HDL Coder /

Signal Routing

説明

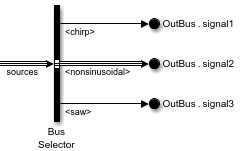

Bus Selector ブロックは、入力バス階層から名前で選択した要素を抽出します。このブロックは、選択した要素を個別に、または新しいバーチャル バスに出力できます。ブロックが、選択した要素を個別に出力した場合、選択した各要素は出力端子に対応します。ブロックが新しいバーチャル バスを出力した場合、ブロックには、選択した各要素が含まれるバーチャル バスの 1 つの出力端子があります。

複数の要素がバス階層内の異なる場所で同じ名前をもつことができますが、各要素は、Bus Selector ブロックで使用される一意の完全修飾名をもちます。たとえば、最上位のバスと入れ子にされたバスが chirp という名前の要素をもつことができます。最上位バスの要素の完全修飾名は chirp です。入れ子にされたバスの要素の完全修飾名は nestedbus.chirp です。ここで、nestedbus は入れ子にされたバスの名前です。

ヒント

サブシステムおよびモデル インターフェイスのバスについては、Bus Selector ブロックをもつ Inport ブロックの代わりに In Bus Element ブロックを使用します。In Bus Element ブロックは次のことを行います。

ブロック線図における線の複雑さと煩雑さを低減する。

インターフェイスに対する段階的な変更を容易にする。

使用ポイントに近いバス要素へのアクセスを許可して、Bus Selector および Goto ブロック構成の使用を回避する。

例

Bus Selector ブロックを使用することで、バスから名前で要素を抽出できます。

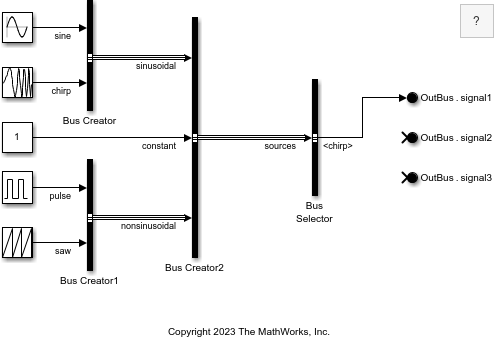

BusElementSelection という名前のモデル例を開いてコンパイルします。モデルをコンパイルするには、Simulink® ツールストリップの [モデル化] タブで、[モデルの更新] または [実行] をクリックします。モデルをコンパイルするとライン スタイルが更新されます。このライン スタイルは、バスを視覚的に識別するのに使用できます。

Bus Creator ブロックはソース信号からバス階層を作成します。

Bus Creatorという名前の Bus Creator ブロックは、sineおよびchirpという名前の信号をsinusoidalという名前のバスにグループ化します。Bus Creator1という名前の Bus Creator ブロックは、pulseおよびsawという名前の信号をnonsinusoidalという名前のバスにグループ化します。Bus Creator2という名前の Bus Creator ブロックは、2 つのバスおよびconstantという名前の信号をsourcesという名前のバスにグループ化します。

Bus Selector ブロックは sources という名前のバスを入力として受け取り、chirp という名前の信号を出力として返します。

この例では、Bus Selector ブロックの出力は Out Bus Element ブロックに接続されます。2 つの Out Bus Element ブロックは未接続のままです。

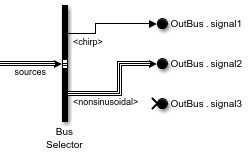

出力端子を Bus Selector ブロックに追加するために、Bus Selector ブロックの出力の端をクリックします。

選択する要素の名前 (たとえば、nonsinusoidal) を入力していきます。

矢印キーを使用して nonsinusoidal という名前の要素を選択します。次に、Enter キーを押します。あるいは、メニューで要素名をクリックします。

新しい端子を Out Bus Element ブロックに接続します。オプションとして、モデルをコンパイルして、選択したバスのバス ライン スタイルを表示します。

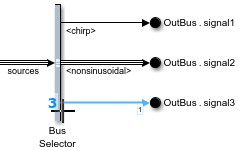

Bus Selector ブロックの新しい出力端子にブロックを接続するには、ブロックの未接続の入力端子を Bus Selector ブロックの出力の端にドラッグします。

たとえば、残りの Out Bus Element ブロックの入力端子を Bus Selector ブロックの出力の端にドラッグします。

選択する要素の名前 (たとえば、saw) を入力していきます。

矢印キーを使用して nonsinusoidal.saw という名前の要素を選択します。次に、Enter キーを押します。あるいは、メニューで要素名をクリックします。

この例では、要素の完全修飾名は nonsinusoidal.saw です。これは、saw という名前の信号は nonsinusoidal という名前の入れ子にされたバス内にあるためです。

この例ではブロック線図で入力バスから要素を選択する方法を示していますが、Bus Selector ブロックをダブルクリックし、開いたダイアログ ボックスで出力要素を選択することもできます。

拡張例

端子

入力

出力

既定では、ブロックは、選択した要素のそれぞれを、対応するバス要素名でラベル付けされた個別の出力端子から出力します。

[バーチャル バスとして出力] パラメーターが選択されていると、ブロックは選択した要素を、バーチャル バスにグループ化された 1 つの端子から出力します。

データ型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | string | Boolean | fixed point | enumerated | bus

複素数のサポート: あり

パラメーター

ブロック パラメーターを対話的に編集するには、プロパティ インスペクターを使用します。Simulink® ツールストリップから、[シミュレーション] タブの [準備] ギャラリーで [プロパティ インスペクター] を選択します。

プロパティ インスペクターでは、既定では垂直方向のレイアウトが使用され、出力要素がバス内の要素のリストの下に示されます。バス内の要素と出力要素を横に並べて表示するには、 をクリックします。

をクリックします。

この パラメーター は読み取り専用です。

バス内の要素のリストには、ブロックに入る要素が示されます。入れ子にされたバスとその要素も含まれます。要素の横にある矢印は、入力要素がバスであることを示します。矢印をクリックすると、そのバスの内容を表示できます。

正規表現を使用して、または使用せずに、名前でバス内の要素をフィルター処理するには、[フィルター] ボックスに検索用語を入力します。検索用語は引用符で囲まないでください。オプションとして、 をクリックして、フィルター処理された結果をフラット リストとして表示します。フラット リストでは、ドット表記を使用してバス階層が反映されます。既定では、フィルター処理された結果は階層ツリーで表示されます。

をクリックして、フィルター処理された結果をフラット リストとして表示します。フラット リストでは、ドット表記を使用してバス階層が反映されます。既定では、フィルター処理された結果は階層ツリーで表示されます。

ブロックに入る要素のソースを選択するには、リスト内の要素を選択します。次に、 をクリックします。または、要素を右クリックします。次に、[ソース ブロックの選択] を選択します。選択されたソース ブロックのパラメーターがプロパティ インスペクターに表示されます。複数の要素のソース ブロックが選択されている場合は、フォーカスがあるソース ブロックのパラメーターがプロパティ インスペクターに表示されます。

をクリックします。または、要素を右クリックします。次に、[ソース ブロックの選択] を選択します。選択されたソース ブロックのパラメーターがプロパティ インスペクターに表示されます。複数の要素のソース ブロックが選択されている場合は、フォーカスがあるソース ブロックのパラメーターがプロパティ インスペクターに表示されます。

ブロックに入る要素のリストを更新するには、 をクリックします。たとえば、ダイアログ ボックスが開いている間に要素名を変更した場合に、このボタンをクリックします。

をクリックします。たとえば、ダイアログ ボックスが開いている間に要素名を変更した場合に、このボタンをクリックします。

ヒント

選択した出力要素の横に緑のチェック マーク アイコンが表示されます。

選択した出力要素の上にマウスをポイントすると、Bus Selector ブロックでその要素が選択された回数が小かっこ内に表示されます。

正規表現では、入力要素がパターンと一致するかどうかに基づいてフィルターが適用されます。たとえば、[フィルター] ボックスに「

t$」と入力すると、要素名が小文字のtで終了するすべての要素が表示されます。詳細については、正規表現を参照してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで取得するには、関数 get_param を使用します。

| パラメーター: | InputSignals |

| 値: | 読み取り専用: cell array of element names |

例: get_param(gcb,'InputSignals')

選択した要素のリストには、ブロックから出る要素が示されます。リストでは、各要素の完全修飾名が使用されます。

Simulink エディターでは、[バーチャル バスとして出力] がオフのとき、端子をブロックに追加して入力バスから要素を選択します。

Bus Selector ブロックの出力の端をクリックします。あるいは、ブロックがバスを受け取り、すべての出力端子が他の端子に接続されている場合は、Bus Selector ブロックの出力の端の近くに新しい線を描画します。

選択する要素を指定します。

プロパティ インスペクターまたは [ブロック パラメーター] ダイアログ ボックスでは、要素を [出力要素] リストに追加して入力バスから要素を選択します。

[バス内の要素] リストで、ブロック出力に追加する 1 つ以上の要素を選択します。

[バス内の要素] リストから複数の要素を選択すると、それらを選択する順序によって [出力要素] リストに追加したときの順序が設定されます。

オプションとして、[出力要素] リストで、下に要素を追加する要素を選択します。要素を選択しなかった場合、要素はリストの末尾に追加されます。

ダイアログ ボックスのレイアウトに応じて、

または

または  をクリックします。または、選択した要素のいずれかを右クリックします。次に、[出力に追加] をクリックします。

をクリックします。または、選択した要素のいずれかを右クリックします。次に、[出力に追加] をクリックします。

出力要素の順序を変更するには、[出力要素] リスト内の要素を別の位置にドラッグします。要素の順序を変更しても、端子との接続は維持されます。

ブロック出力から要素を削除するには、[出力要素] リストから削除する要素を選択します。次に、 をクリックします。または、選択した要素のいずれかを右クリックします。次に、[削除] を選択します。

をクリックします。または、選択した要素のいずれかを右クリックします。次に、[削除] を選択します。

リスト内の要素が入力バスにない場合、要素名は赤色です。選択した要素のリストからその要素を削除するか、指定した名前の要素を含むように入力バスを変更します。入力バスにないすべての出力要素を削除するには、赤色の要素名を右クリックします。次に、[すべての無効な要素の削除] を選択します。

制限

再帰限界値を超えないように、選択する要素の数は Bus Selector ブロックごとに 500 個未満にします。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | OutputSignals |

| 値: | 'signal1,signal2' (既定値) | comma-separated list of element names in quotes |

| データ型: | char | string |

例: set_param(gcb,'OutputSignals','constant,sine')

既定では、ブロックは、選択した要素のそれぞれを、対応するバス要素名でラベル付けされた個別の出力端子から出力します。選択した要素をバーチャル バスにグループ化された 1 つの端子から出力するには、このパラメーターを選択します。

出力を非バーチャル バスに変換するには、Bus Selector ブロックの後に Signal Conversion ブロックを挿入します。Signal Conversion ブロックの [出力] パラメーターを [非バーチャル バス] に設定し、[データ型] を Simulink.Bus オブジェクトに設定します。

[出力要素] リストに 1 つの要素のみが含まれているときにこのパラメーターを選択した場合、その要素はバス内にラップされません。たとえば、要素がバスである場合、出力要素はそのバスです。要素がバスではない場合、出力要素はバスではありません。

依存関係

このパラメーターを使用するには、ブロック出力にメッセージが含まれていてはなりません。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | OutputAsBus |

| 値: | 'off' (既定値) | 'on' |

例: set_param(gcb,'OutputAsBus','on')

ブロックの特性

データ型 |

|

直達 |

|

多次元信号 |

|

可変サイズの信号 |

|

ゼロクロッシング検出 |

|

ヒント

既定では、ダイアログ ボックスが垂直方向のレイアウトで開き、選択した要素がバス内の要素のリストの下に示されます。バス内の要素と選択した出力要素を横に並べて表示するには、 をクリックします。

をクリックします。

拡張機能

実際のデータ型、または機能のサポートは、ブロックの実装に依存します。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

このブロックには 1 つの既定の HDL アーキテクチャがあります。

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| SynthesisAttributes | モデルのブロックとブロック出力信号の合成属性を指定します。生成された HDL コードには、これらの属性が含まれます。詳細については、SynthesisAttributes (HDL Coder)を参照してください。 |

ブロックは、HDL コード生成で次のデータ型をサポートします。

| 入力端子 | 次元 | 固定小数点 | 浮動小数点 | 組み込み整数 | バス | boolean | 複素信号 |

|---|---|---|---|---|---|---|---|

| Port_1 | スカラー ベクトル 行列 (2 次元まで) | あり | half single double | あり | あり | あり | あり |

このブロックは、速度と面積を最適化するために次の HDL 最適化に使用されます。

面積の最適化

速度の最適化

| 最適化 | 説明 |

|---|---|

| 分散型パイプラインの設定の指定 (HDL Coder) | "分散型パイプライン方式"、つまりレジスタのリタイミングとは、設計の既存の遅延を移動して、機能的動作を維持しながらクリティカル パスを低減する速度の最適化です。 |

| 適応パイプライン設定の指定 (HDL Coder) | "適応パイプライン" 最適化では、設計内のブロックにパイプライン レジスタを挿入して、ブロックとレジスタのパターンまたは組み合わせを作成することにより、達成可能なクロック周波数を高め、FPGA ボード上の使用面積を削減できます。 |

ベスト プラクティスについては、バスを使用したモデルの可読性の向上および HDL コードの生成 (HDL Coder)を参照してください。

HDL コード生成でのバスの使用の詳細については、バス (HDL Coder)を参照してください。

PLC コード生成

Simulink® PLC Coder™ を使用して構造化テキスト コードを生成します。

実際のデータ型、または機能のサポートは、ブロックの実装に依存します。

バージョン履歴

R2006a より前に導入R2026a では、R2025b よりも高速に Bus Selector ブロック ダイアログ ボックスを開いたり更新したりできるようになりました。

R2025b では、大規模なバス階層でこのダイアログ ボックスを開くと、Simulink がハングすることがありました。R2026a では、このダイアログ ボックスがより高速で開き、バス階層の読み込み中にビジー状態を示すオーバーレイを表示します。

たとえば、500 レベルの階層と、501 のリーフ要素をもつバス階層があるとします。

% Open new model mdl = "BusBlockPerformance"; new_system(mdl) open_system(mdl) % Create first bus add_block("simulink/Sources/Constant",mdl+"/Constant"); add_block("simulink/Sources/Constant",mdl+"/Constant1"); add_block("simulink/Signal Routing/Bus Creator",mdl+"/Bus Creator"); add_line(mdl,"Constant/1","Bus Creator/1"); add_line(mdl,"Constant1/1","Bus Creator/2"); % Create bus hierarchy prev_bus_blk = "Bus Creator"; for i = 1:499 constant_blk = "Constant"+num2str(i+1); bc_blk = "Bus Creator"+num2str(i); add_block("simulink/Sources/Constant",mdl+"/"+constant_blk); add_block("simulink/Signal Routing/Bus Creator",mdl+"/"+bc_blk); add_line(mdl,constant_blk+"/1",bc_blk+"/1"); add_line(mdl,prev_bus_blk+"/1",bc_blk+"/2"); prev_bus_blk = bc_blk; end % Create and connect Bus Selector block add_block("simulink/Signal Routing/Bus Selector",mdl+"/Bus Selector"); add_line(mdl,prev_bus_blk+"/1","Bus Selector/1");

最上位のバスの Bus Selector ブロック ダイアログ ボックスを開いたり閉じたりするコードは、以前のリリースよりも約 2.3 倍高速になっています。

function timingTestBusSelector open_system("BusBlockPerformance/Bus Selector"); close_system("BusBlockPerformance/Bus Selector"); end

おおよその実行時間は次のとおりです。

R2025b: 1.8 秒

R2026a: 0.79 秒

このコードは、Windows® 11 を使用する AMD EPYC™ 74F3 @ 3.19 GHz テスト システムで、timeit 関数を使用して計測されました。

timeit(@timingTestBusSelector)

[SynthesisAttributes] HDL ブロック プロパティを使用して、ブロックとその出力信号の合成属性を指定します。HDL Coder は、生成される HDL コードにこれらの属性を含めます。

Bus Selector ブロックのパラメーターをプロパティ インスペクターで指定できるようになりました。プロパティ インスペクターまたは [ブロック パラメーター] ダイアログ ボックスで変更を加えると、変更が直ちに適用されます。[適用] ボタンと [OK] ボタンは削除されました。

Bus Selector ブロックには、少なくとも 1 つの出力要素が必要です。出力要素を完全に置き換えるには、入力バスからブロック出力に要素を追加します。その後、元の出力要素を削除します。たとえば、新しい Bus Selector ブロックで、入力バスからブロック出力に要素を追加します。次に、signal1 という名前のプレースホルダー要素を右クリックし、[すべての無効な要素の削除] を選択します。

入力要素のソース ブロックが見つかると、ソース ブロックが強調表示されるのではなく選択されるようになりました。選択されたソース ブロックのパラメーターがプロパティ インスペクターに表示されます。複数の要素のソース ブロックが選択されている場合は、フォーカスがあるソース ブロックのパラメーターがプロパティ インスペクターに表示されます。この変更を反映するために、[ソース ブロックの強調表示] オプション ( ) の名前が [ソース ブロックの選択] に変更されています。

) の名前が [ソース ブロックの選択] に変更されています。

Bus Selector ブロックの [ブロック パラメーター] ダイアログ ボックスでは、要素を右クリックして目的のアクションを選択します。

出力に追加 — 入力バスからブロック出力に要素を追加します。

ソース ブロックの強調表示 — 入力バス内の要素のソース ブロックを強調表示します。

削除 — ブロック出力から要素を削除します。

すべての無効な要素の削除 — 入力バスにないすべての出力要素を削除します。無効な要素の名前は赤色になります。

要素に対して使用可能なアクションを表示するには、要素を右クリックします。選択した複数の要素に対して使用可能なアクションを表示するには、選択に含まれるいずれかの要素を右クリックします。たとえば、無効な要素のみが選択に含まれているとします。右クリックすると 2 つのオプションが表示されます。[削除] と [すべての無効な要素の削除] です。有効な要素が選択に含まれる場合は、表示されるオプションは 1 つになります。[削除] です。

Bus Selector ブロックを操作するときに、アクションの結果がわかりやすくなりました。

[要素の選択] ボタン

が [出力に追加] ボタン

が [出力に追加] ボタン  になりました。

になりました。[選択した要素] リストが [出力要素] リストになりました。

[バーチャル バスとして出力] ボタン

が [バーチャル バスとして出力] チェック ボックスになりました。

が [バーチャル バスとして出力] チェック ボックスになりました。

Bus Selector ブロックのダイアログ ボックスには、追加の機能をもつ効率化された設計が含まれています。

[バス内の要素] リストで、選択した出力要素の横に緑のチェック マーク アイコンが表示されます。

[バス内の要素] リストで、選択した出力要素の上にマウスをポイントすると、Bus Selector ブロックでその要素が選択された回数が小かっこ内に表示されます。

フィルター処理において既定で正規表現がサポートされています。

垂直方向と水平方向のレイアウトを切り替えることができます。

以前の機能は保持されています。

既定では、ダイアログ ボックスが垂直方向のレイアウトで開き、選択した要素がバス内の要素のリストの下に示されます。バス内の要素と選択した出力要素を横に並べて表示するには、 をクリックします。

をクリックします。

水平方向のレイアウトでは、以前の Bus Selector ブロックのダイアログ ボックス設計がより忠実に再現されます。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)