バスを使用したモデルの可読性の向上および HDL コードの生成

これらのガイドラインは、バスの概要、バスを使用して設計をモデル化する方法、HDL コードを生成する方法について示したものです。各ガイドラインに準拠要件のレベルを示す重大度レベルが割り当てられています。詳細については、HDL モデリング ガイドラインの重大度レベルを参照してください。

ガイドライン ID

1.3.3

重大度

情報

説明

バスを使用する場合

モデルの DUT ブロックまたは他のブロックに入力信号や出力信号が多数ある場合は、バスを作成するとモデルの可読性が向上します。バスは、要素と呼ばれる他の信号で構成される合成信号です。バスは、さまざまなデータ型の構造体または同じデータ型のベクトル信号をもつことができます。バスの構成要素の信号または要素は次のとおりです。

double、整数、固定小数点など、信号のデータ型の混在

スカラー要素とベクトル要素の混在

実数値信号と複素数値信号の混在

任意のレベルで入れ子になったその他のバス

多次元信号

HDL Coder のバスのサポート

以下を使用する設計の HDL コードを生成できます。

バスに接続されている DUT サブシステムの端子。

HDL コード生成でサポートされている Simulink® ブロックと Stateflow® ブロック。

HDL Coder™ は、"HDL Coder" ブロック ライブラリのバス対応ブロックのコード生成をサポートします。バス対応ブロックとは、バスを入力として受け入れるブロックとバスを出力として生成できるブロックのことです。Simulink がサポートするバス対応ブロックのリストについては、バス対応ブロックを参照してください。

バスによる HDL コード生成をサポートするブロックについては、信号タイプとデータ型のサポートを参照してください。

バスの作成

バスは、Bus Creatorブロックを使用して作成できます。Bus Creator ブロックは、作成されたバスの各要素名前を付けます。これにより、ソースを検索するときに、要素を名前で参照できます。

バスを使用したモデル化を説明する例については、hdlcoder_bus_nested.slx を開きます。HDL_DUT サブシステムをダブルクリックします。

open_system('hdlcoder_bus_nested') set_param('hdlcoder_bus_nested','SimulationCommand','Update') open_system('hdlcoder_bus_nested/HDL_DUT')

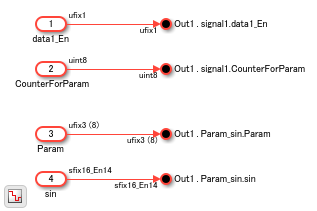

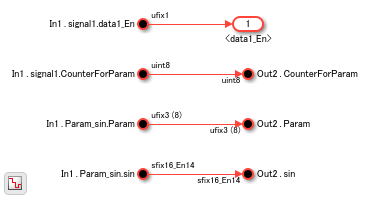

このモデルでは、Bus Creator ブロックは 2 つのバスを作成します。1 つのバスに data1_En 信号と CounterForParam 信号が含まれています。もう一方のバスに Param 信号と sin 信号が含まれています。既定では、バスの各信号はバスに接続された信号の名前を継承します。

バスを入れ子にする

これらの 2 つのバスを結合する別の Bus Creator ブロックが表示されます。Bus Creator ブロックへの 1 つ以上の入力がバスの場合、出力は入れ子にされたバスになります。

入力に名前がない場合は、Bus Creator ブロックがバスの名前を生成します。名前は signaln という形式になります。n は入力信号が接続された端子の番号です。たとえば、2 つ目の Bus Creator ブロックの [ブロック パラメーター] ダイアログ ボックスを開くと、[バス内の要素] が signal1 と Param_sin として表示されます。

バスへの信号値の代入

バス要素の値を変更するには、Bus Assignmentブロックを使用します。バス要素を選択してそれらをバスに再構築する Bus Selector ブロックと Bus Creator ブロックを追加せずに、Bus Assignment ブロックを使用してバス要素値を変更します。

たとえば、モデル hdlcoder_bus_nested_assignment を開きます。

open_system('hdlcoder_bus_nested_assignment') set_param('hdlcoder_bus_nested_assignment','SimulationCommand','Update') open_system('hdlcoder_bus_nested_assignment/HDL_DUT')

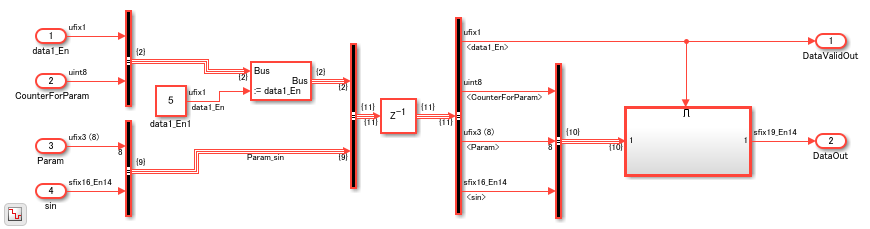

モデルに、値 5 をバス内の data1_En 信号に代入する Bus Assignment ブロックが表示されます。

バス出力の選択

入れ子にされたバスが含まれるバスから信号を抽出するには、Bus Selectorブロックを使用します。既定では、ブロックは指定したバス要素を個別の信号として出力します。信号を別のバスとして出力することもできます。OutputSignals ブロック プロパティを使用して、ブロックが出力する [バス内の要素] を表示できます。このプロパティを使用すると、モデル階層の深いレベルで Bus Selector ブロックに入力される信号を追跡できます。

get_param('hdlcoder_bus_nested/HDL_DUT/Bus Selector5', 'OutputSignals')

ans =

'signal1.data1_En,signal1.CounterForParam,Param_sin.Param,Param_sin.sin'

HDL コードの生成

このモデルの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_bus_nested/HDL_DUT')

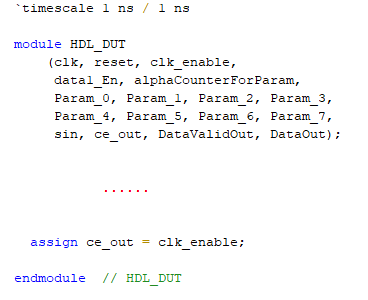

コード ジェネレーターにより、生成されたコードでバスからスカラー信号に展開されることがわかります。たとえば、HDL_DUT サブシステムに対して生成された Verilog ファイルを開くと、入れ子にされた 2 つのバス signal1 と Param_sin を使用する Delay ブロックに対して、バス内の信号ごとに作成された 4 つの always ブロックが表示されます。たとえば、signal1 の一部である data1_En 信号の always ブロックが表示されます。この図に、モジュール定義のバスごとに作成されたスカラー信号を表示します。

サブシステム バス インターフェイスの簡略化

Bus Element ブロックを使用して、サブシステム バス インターフェイスを簡略化できます。In Bus Element ブロックと Out Bus Element ブロックを使用すると、バスをサブシステムに対する入力および出力として簡単かつ柔軟に使用できます。In Bus Element ブロックは Bus Selector ブロックと結合された Inport ブロックと等価です。Out Bus Element ブロックは Bus Creator ブロックと結合された Outport ブロックと等価です。Inport ブロック、Bus Selector ブロック、Bus Creator ブロック、Outport ブロックを使用する既存のモデルをリファクタリングして In Bus Element ブロックと Out Bus Element ブロックを使用するには、Simulink エディターのアクション バーを使用できます。

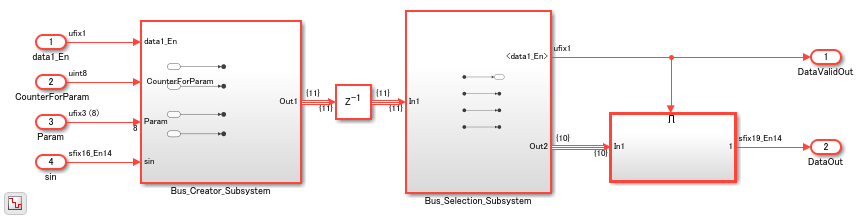

たとえば、モデル hdlcoder_bus_nested_simplified を開きます。このモデルは hdlcoder_bus_nested モデルと機能的に等価ですが、より簡略化されたバージョンです。

open_system('hdlcoder_bus_nested_simplified') set_param('hdlcoder_bus_nested_simplified','SimulationCommand','Update') open_system('hdlcoder_bus_nested_simplified/HDL_DUT')

モデルには Bus Element ブロックを使用してバスの作成とバスの選択を実行する 2 つのサブシステムがあります。Bus_Creator_Subsystem は Outport ブロックを Bus Creator ブロックと結合して Out Bus Element ブロックを作成します。

open_system('hdlcoder_bus_nested_simplified/HDL_DUT/Bus_Creator_Subsystem')

Bus_Selection_Subsystem は Inport ブロックを Bus Selector ブロックと結合して In Bus Element ブロックを作成します。

open_system('hdlcoder_bus_nested_simplified/HDL_DUT/Bus_Selection_Subsystem')

詳細については、バス要素端子を使用したサブシステム インターフェイスとモデル インターフェイスの簡略化を参照してください。

バーチャル バスと非バーチャル バス

Bus Creator ブロックと Bus Selector ブロックを使用して前に作成したモデル hdlcoder_bus_nested のバスはバーチャル バスです。各バス要素はメモリ内に格納されますが、バスは格納されません。バスはグラフを簡略化しますが、機能的な影響はありません。生成された HDL コードに構成要素の信号は表示されますが、バスは表示されません。

モデルのバスと生成された HDL コード間の対応関係をより簡単に追跡するには、非バーチャル バスを使用します。非バーチャル バスは構造体を使用してバスを保持するため、クリーンな HDL コードを生成します。バーチャル バスを非バーチャル バスに変換するには、Bus Creator ブロックのブロック パラメーターで object_name をバス オブジェクトの名前で置き換え、[出力データ型] を Bus: object_name として指定してから [非バーチャル バスとして出力] を選択します。

バーチャル バスの非バーチャル バスへの変換を参照してください。

バス配列

バス配列とは、要素がバスである配列のことです。バス配列内の各要素は、非バーチャルであることが必要であり、さらに同じデータ型でなければなりません。

バス配列によるモデル化の詳細については、バス配列を使用するサブシステムの HDL コードの生成を参照してください。