Signal Conversion

信号の値を変えることなく、信号を新しいタイプの信号に変換

ライブラリ:

Simulink /

Signal Attributes

HDL Coder /

Signal Attributes

Signal Conversion ブロックの代替構成:

Signal Copy | To Virtual Bus | To Nonvirtual Bus

説明

Signal Conversion ブロックは、ある型から別の型に信号を変換します。実行する変換の種類を選択するには、[出力] パラメーターを使用するか、事前構成されたいずれかの Signal Conversion ブロックを使用します。

Signal Copy ブロック

To Virtual Bus ブロック

To Nonvirtual Bus ブロック

例

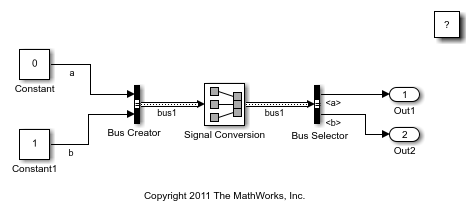

Signal Conversion ブロックを使用して、バスの連続コピーを作成します。

Bus Creator ブロックは、Signal Conversion ブロックの入力となる非バーチャル バスを作成します。Signal Conversion ブロックは、[出力] パラメーターが Signal copy に設定されているため、入力されたバスの別の連続コピーを作成します。

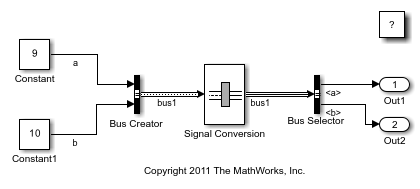

Signal Conversion ブロックを使用して、バーチャル バスを非バーチャル バスに変換します。

Bus Creator ブロックは、Signal Conversion ブロックの入力となるバーチャル バスを作成します。バーチャル バスを非バーチャル バスに変換するには、Signal Conversion ブロックの [出力] パラメーターを Nonvirtual bus に設定し、その [データ型] パラメーターを Simulink.Bus オブジェクトに設定します。指定された Bus オブジェクトは Bus Creator ブロックからのバスのバス階層と一致します。Signal Conversion ブロックからの非バーチャル バス出力は Bus Selector ブロックに対する入力です。

Signal Conversion ブロックを使用して、非バーチャル バスをバーチャル バスに変換します。

Bus Creator ブロックは、Signal Conversion ブロックの入力となる非バーチャル バスを作成します。非バーチャル バスをバーチャル バスに変換するには、Signal Conversion ブロックの [出力] パラメーターを Virtual bus に設定します。Signal Conversion ブロックからのバーチャル バス出力は Bus Selector ブロックに対する入力です。

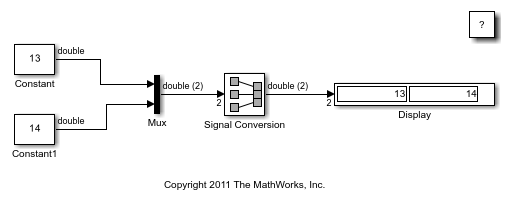

Signal Conversion ブロックを使用して、Mux 信号をベクトルに変換します。

Mux ブロックは、Signal Conversion ブロックの入力となる Mux 信号を作成します。Mux 信号をベクトルに変換するには、Signal Conversion ブロックの [出力] パラメーターを Signal copy に設定します。Signal Conversion ブロックからのベクトル出力は Display ブロックに対する入力です。

端子

入力

入力信号は、このブロックで別の型に変換するスカラー、ベクトル、行列、配列、またはバスです。

データ型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | string | Boolean | fixed point | enumerated | bus | image

出力

出力信号は、指定された型に変換された入力信号です。

データ型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus | image

パラメーター

ブロック パラメーターを対話的に編集するには、プロパティ インスペクターを使用します。Simulink® ツールストリップから、[シミュレーション] タブの [準備] ギャラリーで [プロパティ インスペクター] を選択します。

実行する変換の種類を指定します。

信号のコピー— 入力信号の連続コピーを作成します。Signal Conversion ブロックと Signal Copy ブロックでは、この値が既定値です。バーチャル バス— 非バーチャル バスをバーチャル バスに変換します。To Virtual Bus ブロックでは、この値が既定値です。非バーチャル バス— バーチャル バスを非バーチャル バスに変換します。To Nonvirtual Bus ブロックでは、この値が既定値です。

[信号のコピー] オプションの場合、入力の種類に応じてブロックでのコピーの作成方法が決まります。

たとえば、メモリの不連続領域を占有する要素をもつ Mux 信号をブロックで受け取るとします。この変換では、メモリの連続領域を Mux 信号の要素に割り当てて、タイム ステップごとに、ブロック入力で表される不連続領域の値をブロック出力で表される連続領域にコピーします。出力は、メモリの連続領域を占有する要素をもつベクトルです。

使用する変換の種類はモデル化の目的によって異なります。

| モデル化の目的 | オプション |

|---|---|

muxed (多重化) 信号の生成コードを低減します。 Simulink Coder™ ソフトウェアの例はサブシステムからの再呼び出し可能なコードの生成 (Simulink Coder)を参照してください。 | 信号のコピー |

一定のサンプル時間をもつブロックを Enabled Subsystem の出力端子に接続します。 | 信号のコピー |

非バーチャル バスをバーチャル バスに変換することでメモリを節約します。 | バーチャル バス |

バーチャル バスを非バーチャル バスを必要とするモデリング構造に渡します。 | 非バーチャル バス |

バスの配列のコピーを作成します。 このブロックでバスの配列を非バーチャル バスまたはバーチャル バスに変換することはできません。バスの配列からバスを抽出するには、Selector ブロックを使用します。 | 信号のコピー |

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | ConversionOutput |

| 値: | 'Signal copy' (既定値) | 'Virtual bus' | 'Nonvirtual bus' |

例: set_param(gcb,'ConversionOutput','Virtual bus')

このブロックで生成する非バーチャル バスの出力データ型を指定します。

Inherit: auto— 上流のブロックからデータ型を継承します。たとえば、上流の Bus Creator ブロックからSimulink.Busオブジェクト データ型を継承します。Bus: <object name>または<data type expression>— 入力バスの階層と一致するSimulink.Busオブジェクトを指定します。上流の Bus Creator ブロックでバス オブジェクトを指定している場合、同じバス オブジェクトを指定します。

データ属性の設定には [データ型アシスタント] が役立ちます。[データ型アシスタント] を使用するには、 をクリックします。詳細については、データ型アシスタントを利用したデータ型の指定を参照してください。

をクリックします。詳細については、データ型アシスタントを利用したデータ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[出力] を [非バーチャル バス] に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | OutDataTypeStr |

| 値: | 'Inherit: auto' (既定値) | 'Bus: <object name>' | '<data type expression>' |

例: set_param(gcb,'OutDataTypeStr','Bus: myBusObj')

入力信号の要素がメモリの連続領域を占領する場合、既定では、最適化として、このブロックがコンパイルされたモデルから排除されます。詳細については、Block reductionを参照してください。

このブロックがコンパイルされたモデルから排除されないようにするには、このパラメーターを選択します。

このパラメーターの変更は、モデルの次回コンパイル時に有効になります。

依存関係

このパラメーターを有効にするには、[出力] を [信号のコピー] に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | OverrideOpt |

| 値: | 'off' (既定値) | 'on' |

例: set_param(gcb,'OverrideOpt','on')

ブロックの特性

データ型 |

|

直達 |

|

多次元信号 |

|

可変サイズの信号 |

|

ゼロクロッシング検出 |

|

代替構成

Signal Copy ブロックは Signal Conversion ブロックと名前のみ異なります。

ライブラリ:

Simulink /

Quick Insert /

Signal Attributes

To Virtual Bus ブロックでは [出力] が [バーチャル バス] に設定されます。

ライブラリ:

Simulink /

Quick Insert /

Signal Attributes

To Nonvirtual Bus ブロックでは [出力] が [非バーチャル バス] に設定されます。

ライブラリ:

Simulink /

Quick Insert /

Signal Attributes

拡張機能

C/C++ コード生成

Simulink® Coder™ を使用して C および C++ コードを生成します。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

このブロックにはパススルー実装があります。

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| SynthesisAttributes | モデルのブロックとブロック出力信号の合成属性を指定します。生成された HDL コードには、これらの属性が含まれます。詳細については、SynthesisAttributes (HDL Coder)を参照してください。 |

このブロックは、複素信号のコード生成をサポートしています。

PLC コード生成

Simulink® PLC Coder™ を使用して構造化テキスト コードを生成します。

固定小数点の変換

Fixed-Point Designer™ を使用して固定小数点システムの設計とシミュレーションを行います。

バージョン履歴

R2006a より前に導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)