このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Divide

一方の入力を他方の入力で除算

ライブラリ:

Simulink /

Math Operations

HDL Coder /

HDL Floating Point Operations

HDL Coder /

Math Operations

説明

Divide ブロックは、第 1 入力を第 2 入力で除算した結果を出力します。入力は、2 つともスカラー、スカラーと非スカラー、あるいは同じ次元の 2 つの非スカラーになることがあります。すべての端子が同じ single または double のデータ型である場合、このブロックは、除算端子での複素数入力値のみをサポートします。

Divide ブロックは、機能的に Product ブロックです。このブロックは、あらかじめ設定された 2 つのブロック パラメーターの値をもちます。

乗算:

要素単位(.*)入力数:

*/

これらのパラメーターのいずれかに既定でない値を設定すると、Divide ブロックを機能的に等価な Product ブロックまたは Product of Elements ブロックに変更できます。

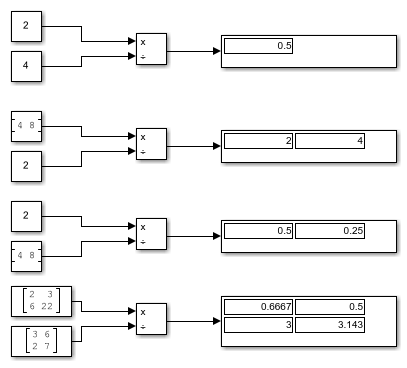

例

端子

入力

他の入力に乗算する入力信号。

依存関係

1 つ以上の [X] 端子を有効にするには、[入力の数] パラメーターに対して 1 つ以上の * 文字を指定し、[乗算] パラメーターを [要素単位(.*)] に設定します。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

除算または逆演算の入力信号。

依存関係

1 つ以上の [÷] 端子を有効にするには、[入力の数] パラメーターに対して 1 つ以上の / 文字を指定し、[乗算] パラメーターを [要素単位(.*)] に設定します。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

乗算または除算する 1 番目の入力。スカラー、ベクトル、行列または N 次元配列として指定します。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

乗算または除算する N 番目の入力。スカラー、ベクトル、行列または N 次元配列として指定します。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

他の入力に乗算する入力信号。

依存関係

1 つ以上の [*] 端子を有効にするには、[入力の数] パラメーターに対して 1 つ以上の * 文字を指定し、[乗算] パラメーターを [行列 (*)] に設定します。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

除算または逆演算の入力信号。

依存関係

1 つ以上の [Inv] 端子を有効にするには、[入力の数] パラメーターに対して 1 つ以上の / 文字を指定し、[乗算] パラメーターを [行列 (*)] に設定します。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

出力

入力を乗算、除算、または逆数を求めることで計算される出力。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

パラメーター

メイン

ブロックの 2 つのプロパティを制御します。

ブロックの入力端子の数

各入力が出力されるときに乗算されるかまたは除算されるか

指定に関する詳細は次の通りです。

1、*、または/このブロックは 1 つの入力端子をもっています。要素単位モードでは、ブロックは Product of Elements ブロックで記述されたとおりに入力を処理します。行列モードでは、パラメーター値が

1または*の場合、ブロックは入力値を出力します。値が/である場合、入力は正方行列 (縮退した場合としてスカラーを含む) でなければなりません。ブロックは逆行列を出力します。詳細については、要素単位モードおよび行列モードを参照してください。整数値 > 1

ブロックがもつ入力数は整数値で指定されます。[乗算] パラメーターで指定される要素単位モードまたは行列モードによって、入力は互いに乗算されます。詳細については、要素単位モードおよび行列モードを参照してください。

2 つ以上の

*と/から成る単純文字列ブロックは文字ベクトルの長さで与えられる入力数をもちます。

*に相当する各入力は、乗算され、出力されます。/に対応する各入力は除算され、出力されます。演算は、[乗算] パラメーターで指定されるように、要素単位モードまたは行列モードで行われます。詳細については、要素単位モードおよび行列モードを参照してください。

プログラムでの使用

ブロック パラメーター: Inputs |

| 型: 文字ベクトル |

値: '2' | '*' | '**' | '*/' | '*/*' | ... |

既定の設定: '*/' |

ブロックが [要素単位(.*)] または [行列 (*)] の乗算を実行するかどうかを指定します。

プログラムでの使用

ブロック パラメーター: Multiplication |

| 型: 文字ベクトル |

値: 'Element-wise(.*)' | 'Matrix(*)' |

既定の設定: 'Element-wise(.*)' |

指定した次元に沿って関数を適用する方法を指定します。

すべての次元— すべての次元のすべての入力値について関数を適用します。指定した次元— 指定した次元のすべての入力値について関数を適用します。

たとえば、次のモデルでは、[乗算] を [要素単位(.*)] に設定し、[適用範囲] を [すべての次元] に設定しています。ブロックは、すべての次元のすべての値の積を返します。

![2D matrix with Constant block value [1 2 3;7 6 4] as input to Product block configured for all dimensions](prod_alldim.png)

依存関係

このパラメーターを有効にするには、[入力の数] を * に、[乗算] を [要素単位(.*)] に設定します。

プログラムでの使用

ブロック パラメーター: CollapseMode |

| 型: 文字ベクトル |

値: 'All dimensions' | 'Specified dimension' |

既定の設定: 'All dimensions' |

乗算する次元を正の整数として指定します。たとえば、2 次元行列では、1 の場合は各列に関数が適用され、2 の場合は各行に関数が適用されます。

たとえば、次のモデルでは、[乗算] を [要素単位(.*)] に設定し、[適用範囲] を [指定した次元] に設定し、[次元] を 2 に設定しています。ブロックは、各行のすべての値の積を返します。

![2D matrix with Constant block value [1 2 3;7 6 4] as input to Product block configured for dimension 2](prod_2dim.png)

依存関係

このパラメーターは次の場合に有効になります。

[入力の数] を

*に設定[乗算] を

[要素単位(.*)]に設定[適用範囲] を

[指定した次元]に設定

プログラムでの使用

ブロック パラメーター: CollapseDim |

| 型: 文字ベクトル |

値: '1' | '2' | ... |

既定の設定: '1' |

サンプルの時間間隔を指定します。サンプル時間を継承するには、このパラメーターを -1 に設定します。詳細については、サンプル時間の指定を参照してください。

依存関係

このパラメーターは、-1 以外の値に設定した場合にのみ表示されます。詳細は、サンプル時間が推奨されないブロックを参照してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | SampleTime |

| 値: | "-1" (既定値) | scalar or vector in quotes |

信号属性

すべての入力信号が同じデータ型をもたなければならないかどうかを指定します。このパラメーターを有効にすると、入力信号のデータ型が異なる場合はシミュレーション中にエラーが発生します。

プログラムでの使用

ブロック パラメーター: InputSameDT |

| 型: 文字ベクトル |

値: 'off' | 'on' |

既定: 'off' |

ソフトウェアでチェックする出力範囲の下限値。

最小値を使用して以下が行われます。

一部のブロックに対するパラメーター範囲のチェック (ブロック パラメーターの最小値と最大値の指定を参照)

シミュレーション範囲のチェック (信号範囲の指定およびシミュレーション範囲のチェックの有効化を参照)

固定小数点データ型の自動スケーリング

モデルから生成するコードの最適化。この最適化により、アルゴリズム コードが削除され、SIL やエクスターナル モードなどの一部のシミュレーション モードの結果に影響を与えることがあります。詳細については、Optimize using the specified minimum and maximum values (Embedded Coder)を参照してください。

ヒント

[出力の最小値] により、実際の出力信号が飽和する (またはクリップされる) ことはありません。代わりに、Saturation ブロックを使用してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | OutMin |

| 値: | '[]' (既定値) | scalar in quotes |

ソフトウェアでチェックする出力範囲の上限値。

最大値を使用して以下が行われます。

一部のブロックに対するパラメーター範囲のチェック (ブロック パラメーターの最小値と最大値の指定を参照)

シミュレーション範囲のチェック (信号範囲の指定およびシミュレーション範囲のチェックの有効化を参照)

固定小数点データ型の自動スケーリング

モデルから生成するコードの最適化。この最適化により、アルゴリズム コードが削除され、SIL やエクスターナル モードなどの一部のシミュレーション モードの結果に影響を与えることがあります。詳細については、Optimize using the specified minimum and maximum values (Embedded Coder)を参照してください。

ヒント

[出力の最大値] により、実際の出力信号が飽和する (またはクリップされる) ことはありません。代わりに、Saturation ブロックを使用してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | OutMax |

| 値: | '[]' (既定値) | scalar in quotes |

出力のデータ型を選択します。型は継承されるか、直接指定されるか、Simulink.NumericType などのデータ型オブジェクトとして表現されます。詳細については、信号のデータ型の制御を参照してください。

継承オプションを選択すると、ブロックは次のように動作します。

継承: 内部ルールによる継承— Simulink® は、組み込みターゲット ハードウェアのプロパティを考慮しつつ、数値の精度、パフォーマンス、および生成コードのサイズのバランスが取れるように、データ型を選択します。組み込みターゲット ハードウェアの設定を変更すると、内部ルールにより選択されるデータ型が変更される可能性があります。たとえば、ブロックがint8型の入力にint16のゲインを乗算し、ターゲット ハードウェア タイプとして[ASIC/FPGA]が指定されている場合、出力データ型はsfix24です。ターゲット ハードウェアとして[Unspecified (assume 32-bit Generic)](汎用 32 ビット マイクロプロセッサ) が指定された場合、出力データ型はint32です。ターゲット マイクロプロセッサによって指定される語長では出力範囲に対応できない場合、Simulink は診断ビューアーにエラーを表示します。コードの効率と数値の精度が、ソフトウェアにより同時に最適化されるとは限りません。内部ルールが、数値精度またはパフォーマンスに対する要求を満たさない場合は、以下のいずれかを行ってください。

出力データ型を明示的に指定する。

単に

[継承: 入力と同じ]を選択します。fixdt(1,32,16)のように既定のデータ型を明示的に指定し、固定小数点ツールを使用してモデルにデータ型を推奨する。詳細については、fxptdlg(Fixed-Point Designer) を参照してください。独自の継承ルールを指定するには、

[継承: 逆伝播による継承]を使用し、Data Type Propagation ブロックを使用します。このブロックの使い方の例については、Signal Attributes ライブラリの Data Type Propagation Examples ブロックを参照してください。

継承: 逆伝播による継承— 駆動ブロックのデータ型を使用します。継承: 1 番目の入力と同じ— 1 番目の入力信号のデータ型を使用します。

依存関係

入力が単精度より小さい浮動小数点データ型の場合、[継承: 内部ルールによる継承] 出力データ型は単精度より小さい浮動小数点の出力型を継承するコンフィギュレーション パラメーターの設定によって変わります。データ型の符合化に必要なビット数が単精度データ型の符合化に必要な 32 ビットより少ない場合、データ型は単精度より小さくなります。たとえば、half と int16 は単精度より小さくなります。

プログラムでの使用

ブロック パラメーター: OutDataTypeStr |

| 型: 文字ベクトル |

値: 'Inherit: Inherit via internal rule | 'Inherit: Same as first input' | 'Inherit: Inherit via back propagation' | 'double' | 'single' | 'int8' | 'uint8' | 'int16' | 'uint16' | 'int32' | 'uint32' | 'int64' | 'uint64' | 'fixdt(1,16)' | 'fixdt(1,16,0)' | 'fixdt(1,16,2^0,0)' | '<data type expression>' |

既定の設定: 'Inherit: Inherit via internal rule' |

固定小数点ツールが、ブロックに指定した [出力] データ型をオーバーライドしないようにするには、このパラメーターを選択します。詳細については、[出力データ型の設定をロックする] の使用 (Fixed-Point Designer)を参照してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | LockScale |

| 値: | 'off' (既定値) | 'on' |

固定小数点演算の丸めモードを選択します。以下を選択できます。

正方向正の無限大方向に正負の値を丸めます。MATLAB® 関数

ceilと等価です。最も近い偶数方向最も近い表現可能な値に数値を丸めます。同順位が発生した場合は、最も近い偶数の整数に丸めます。Fixed-Point Designer™ 関数

convergentと等価です。負方向負の無限大方向に正負の値を丸めます。MATLAB 関数

floorと等価です。最も近い正の整数方向最も近い表現可能な値に数値を丸めます。同順位が発生した場合は、正の無限大方向に丸めます。Fixed-Point Designer 関数

nearestと等価です。最も近い整数方向最も近い表現可能な値に数値を丸めます。同順位が発生した場合は、正の数値を正の無限大方向、負の数値を負の無限大方向に丸めます。Fixed-Point Designer 関数

roundと等価です。最も簡潔負方向の丸めとゼロ方向の丸めのいずれかを選択し、できるだけ効率の高い丸めコードを生成します。この丸めモードは、[ハードウェア実行] ペインの次のコンフィギュレーション パラメーターの影響を受けます。

[符号付き整数の除算の丸め] パラメーターが

[ゼロ方向]または[未定義]に設定されている場合、[最も簡潔]はゼロ方向と解釈されます。[符号付き整数の除算の丸め] パラメーターが

[負方向]に設定されている場合、[最も簡潔]はfloorと解釈されます。

ゼロ方向ゼロ方向に数値を丸めます。MATLAB 関数

fixと等価です。

詳細については、丸めモード (Fixed-Point Designer)を参照してください。

ブロック パラメーターは常に最近傍の表現可能な値に丸められます。ブロックパラメーターの丸めを直接制御するには、MATLAB の丸め関数を使用する式をマスク フィールドに入力します。

プログラムでの使用

ブロック パラメーター: RndMeth |

| 型: 文字ベクトル |

値: 'Ceiling' | 'Convergent' | 'Floor' | 'Nearest' | 'Round' | 'Simplest' | 'Zero' |

既定の設定: 'Floor' |

オーバーフローで飽和するかラップするかを指定します。

on— オーバーフローは、データ型が表現できる最小値または最大値のいずれかに飽和します。off— オーバーフローは、データ型によって表現される適切な値にラップされます。

たとえば、符号付き 8 ビット整数 int8 で表現できる最大値は 127 です。この最大値を超えるブロックの演算結果により 8 ビット整数のオーバーフローが発生します。

このパラメーターがオンになっていると、ブロック出力は 127 で飽和します。同様に、ブロック出力は最小出力値である -128 で飽和します。

このパラメーターをオフにすると、オーバーフローを引き起こした値は

int8として解釈され、意図しない結果が引き起こされる可能性があります。たとえば、int8として表されるブロック結果 130 (バイナリで 1000 0010) は -126 です。

ヒント

モデルでオーバーフローが発生する可能性があり、生成コードに飽和保護を明示的に組み込む必要があるときには、このパラメーターをオンにすることを検討してください。

生成コードの効率を最適化する場合には、このパラメーターをオフにすることを検討してください。このパラメーターをオフにすると、ブロックが範囲外の信号を処理する方法を指定しすぎないようにする点でも役立ちます。詳細については、信号範囲のエラーのトラブルシューティングを参照してください。

このパラメーターをオンにすると、飽和は出力や結果だけでなく、このブロックの内部演算すべてに適用されます。

通常、オーバーフローが可能ではない場合は、コード生成プロセスで検出されます。この場合、コード ジェネレーターでは飽和コードは生成されません。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | SaturateOnIntegerOverflow |

| 値: | 'off' (既定値) | 'on' |

指定するデータのカテゴリを選択します。

継承— データ型の規則の継承。Inheritを選択すると、右側から 2 番目のメニュー/テキスト ボックスが有効になり、そこで継承モードを選択できます。組み込み— 組み込みデータ型を指定します。Built inを選択すると、右側から 2 番目のメニュー/テキスト ボックスが有効になり、そこで組み込みデータ型を選択できます。固定小数点— 固定小数点データ型。[固定小数点]を選択すると、固定小数点データ型を指定するために使用できる追加のパラメーターが有効になります。式— 評価結果がデータ型となる式。[式]を選択すると、右側から 2 番目のメニュー/テキスト ボックスが有効になります。そこに式を入力することができます。

詳細については、データ型アシスタントを利用したデータ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[データ型アシスタントを表示] ボタンをクリックします。

この信号のデータ型オーバーライド モードを選択します。

[継承]を選択すると、Simulink はコンテキストからデータ型オーバーライド設定を継承します。コンテキストとはブロックのことで、信号を使用している Simulink のSimulink.Signalオブジェクトまたは Stateflow® チャートです。[オフ]を選択すると、Simulink はコンテキストのデータ型オーバーライド設定を無視し、信号に対して指定された固定小数点データ型を使用します。

詳細については、Simulink ドキュメンテーションのデータ型アシスタントを利用したデータ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[モード] を [組み込み] または [固定小数点] に設定します。

ヒント

個々のデータ型に対してデータ型オーバーライドをオフにする機能により、データ型オーバーライドを適用する際に、モデル内のデータ型をさらに効果的に制御できます。たとえば、このオプションを使用すると、データ型オーバーライド設定にかかわらず、データ型が下流ブロックの要件を満たすことを確認できます。

固定小数点データが符号付きであるか符号なしであるかを指定します。符号付きデータでは正の値と負の値を表現できますが、符号なしデータでは正の値のみを表現できます。

[符号付き]。符号付き固定小数点データを指定します。[符号なし]。符号なし固定小数点データを指定します。

詳細については、データ型アシスタントを利用したデータ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[モード] を [Fixed point] に設定します。

量子化された整数をもつ語のビット サイズを指定します。詳細については、固定小数点データ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[モード] を [固定小数点] に設定します。

固定小数点データ型の小数部の長さを正または負の整数として指定します。詳細については、固定小数点データ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[スケーリング] を [2 進小数点] に設定します。

オーバーフローを避け、量子化誤差を最小限に抑えるための固定小数点データのスケーリング方法を指定します。詳細については、固定小数点データ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[モード] を [固定小数点] に設定します。

固定小数点データ型の傾きを指定します。詳細については、固定小数点データ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[スケーリング] を [傾きとバイアス] に設定します。

固定小数点データ型のバイアスを任意の実数として指定します。詳細については、固定小数点データ型の指定を参照してください。

依存関係

このパラメーターを有効にするには、[スケーリング] を [傾きとバイアス] に設定します。

ブロックの特性

データ型 |

|

直達 |

|

多次元信号 |

|

可変サイズの信号 |

|

ゼロクロッシング検出 |

|

拡張機能

次の条件によって、シミュレーションと生成コード間で異なる結果が生じる可能性があります。

Divide ブロック入力に

NaNまたはinf値が含まれるDivide ブロックが実行中に

NaNまたはinfを生成する

この違いは、非有限の値である NaN または inf により発生します。その場合、モデル コンフィギュレーションを検証して NaN や inf が生じる条件を排除してください。

Simulink Coder™ ビルド プロセスは、効率的な逆行列演算と除算のコードを提供します。次の表で、各種の利点およびそれぞれの利点が利用可能なタイミングについて説明します。

| 利点 | 小規模の行列 (2 行 2 列 ~ 5 行 5 列) | 中規模の行列 (6 行 6 列 ~ 20 行 20 列) | 大規模の行列 (20 行 20 列超) |

|---|---|---|---|

| より高速なコード実行時間 (R2011a 以前のリリースに対する比較) | あり | なし | あり |

| ROM/RAM 使用量抑制 (R2011a 以前のリリースに対する比較) | 実数値の場合は「あり」 | 実数値の場合は「あり」 | 実数値の場合は「あり」 |

| 変数の再利用 | あり | あり | あり |

| デッド コード除去 | あり | あり | あり |

| 定数畳み込み | あり | あり | あり |

| 式の畳み込み | あり | あり | あり |

| MATLAB Coder の結果との整合性 | あり | あり | あり |

3 つ以上の異なる次元の入力があるブロックの場合、コードには中間結果の一時変数を格納するバッファーが別途含まれている場合があります。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

HDL に最適化された除算演算を実行するには、Product ブロックを Divide ブロックに逆数モードで接続します。

Divide ブロックは [入力の数] が */ に設定された Product ブロックと同じです。

| アーキテクチャ | 説明 |

|---|---|

ShiftAdd (既定) | 複数のシフト演算と加算演算を実行して商を計算する非回復型除算アルゴリズムを使用して、除算演算を実行します。 |

逆数モード

[入力の数] が / に設定される場合、Divide ブロックは逆数モードになります。

| アーキテクチャ | 説明 |

|---|---|

ShiftAdd (既定) | 複数のシフト演算と加算演算を実行して逆数を計算する非回復型除算アルゴリズムを使用して、逆数の演算を実行します。 |

| 一般 | |

|---|---|

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| LatencyStrategy | このプロパティを有効にするには、HDL アーキテクチャを [LatencyStrategy] を |

| CustomLatency | このプロパティを有効にするには、HDL アーキテクチャを |

| IterationsPerPipeline | [LatencyStrategy] を 詳細については、Divide (HDL Coder)を参照してください。 |

| ネイティブ浮動小数点 | |

|---|---|

| HandleDenormals | HDL Coder で追加のロジックを挿入して設計で非正規数を処理するかどうかを指定します。非正規数とは、その大きさが仮数の先頭にゼロを付けずに表現できる最小の浮動小数点数より小さい数値のことです。既定の設定は |

| MantissaMultiplyStrategy | コード生成中に仮数乗算演算を実装する方法を指定します。さまざまな設定を使用することで、ターゲット FPGA デバイスでの DSP の使用方法を制御できます。既定の設定は |

| DivisionAlgorithm | Radix-2 または Radix-4 のどちらのアルゴリズムを使用して浮動小数点の除算を実行するのかを指定します。Radix-2 モードでは、レイテンシと周波数の間にトレードオフがあります。Radix-4 モードでは、レイテンシとリソース使用率の間にトレードオフがあります。詳細については、DivisionAlgorithm (HDL Coder)を参照してください。 |

このブロックには、生成されたコードで追加のレイテンシを導入するマルチサイクル実装があります。追加されたレイテンシを確認するには、生成されたモデルまたは検証モデルを表示します。生成されたモデルと検証モデル (HDL Coder)を参照してください。

ネイティブ浮動小数点のレイテンシ

| 演算子 | 浮動小数点型 | レイテンシ手法 | レイテンシ (サイクル単位) | カスタム レイテンシのサポート |

|---|---|---|---|---|

| 除算 | double | 最小値 | 31 | あり |

| 最大値 | 61 | |||

| single | 最小値 | 17 | ||

| 最大値 | 32 | |||

| half | 最小値 | 10 | ||

| 最大値 | 19 | |||

| 逆数 | double | 最小値 | 6 | あり |

| 最大値 | 9 | |||

| single | 最小値 | 6 | ||

| 最大値 | 8 | |||

| half | 最小値 | 4 | ||

| 最大値 | 7 |

固定小数点のレイテンシ

| 演算子 | 追加のレイテンシのサイクル | レイテンシ手法のサポート | カスタム レイテンシのサポート |

|---|---|---|---|

| 除算 | 入出力の語長および小数部の長さによって異なります。詳細については、 | あり | あり |

| 逆数 | 入出力の語長および小数部の長さによって異なります。詳細については、 | あり | あり |

HDL コード生成では、[ShiftAdd] の divide (*/) 演算と reciprocal (/) 演算に対して異なる出力データ型がサポートされます。ブロックに対して次の出力データ型を使用できます。

継承: 内部ルールによる継承継承: MSB を保持継承: スケーリングの一致継承: 逆伝播による継承継承: 1 番目の入力と同じ整数型 (uint8,int8,uint16,int16,uint32,int32,uint64,int64)固定小数点データ型Floating-point types

ブロックに対して次の整数丸めモードを使用できます。

| ブロック | 整数丸めモード |

|---|---|

Divide |

|

逆数 |

|

メモ

生成された HDL コードをターゲット ハードウェアに展開するには、[コンフィギュレーション パラメーター] ダイアログ ボックスの [ハードウェア実行] ペインで [符号付き整数の除算の丸め] パラメーターが [ゼロ] または [負方向] に設定されていることを確認します。

このブロックは複素信号を使用する除算のコード生成をサポートしません。

以下の HDL Coder の最適化を使用して、速度、面積、I/O を最適化できます。

面積の最適化

[ShiftAdd] アーキテクチャを使用する Divide ブロックと Reciprocal ブロックに対して、共有またはストリーミングの最適化を適用できます。

| ブロック (入力) | リソース共有 | ストリーミング |

|---|---|---|

| Divide (/* または */) | あり | あり |

| Reciprocal (/) | あり | なし |

これらのブロックで共有最適化を使用する場合は、ブロックを必ず Atomic サブシステム内に含め、[既定のパラメーター動作] コンフィギュレーション パラメーターを [インライン] に設定してください。

速度の最適化

| 最適化 | 説明 |

|---|---|

| 分散型パイプラインの設定の指定 (HDL Coder) | "分散型パイプライン方式"、つまりレジスタのリタイミングとは、設計の既存の遅延を移動して、機能的動作を維持しながらクリティカル パスを低減する速度の最適化です。 Divide ブロックと Reciprocal ブロックの場合、HDL Coder はブロックの内部ではなく周囲にパイプライン レジスタを分散します。 |

| クロックレート パイプライン (HDL Coder) | "クロックレート パイプライン" は、他の速度と面積の最適化でクロック レートでのレイテンシを導入できるようにする HDL Coder の最適化フレームワークです。 |

| クリティカル パスの推定 (HDL Coder) | クリティカル パスの可能性が最も高いパスを設計内で簡単に特定するには、"クリティカル パスの推定" を使用します。クリティカル パスの推定は、クリティカル パスを検出する反復的プロセスを高速化します。クリティカル パスの推定で特徴付けられるブロックについては、特徴付けられるブロック (HDL Coder)を参照してください。 |

I/O の最適化

| 最適化 | 説明 |

|---|---|

| フレームからサンプルへの変換 (HDL Coder) | 設計で必要な I/O を最適化するには、フレームからサンプルへの変換を使用します。この最適化は、フレームベースのベクトルまたは行列の入力を HDL コード生成用により小さいサイズのサンプルまたはピクセルに変換して、ストリームベースのハードウェアをターゲットにし、大規模な入出力信号の処理に必要な FPGA I/O を削減します。 |

ブロックの使用のベスト プラクティスについては、次を参照してください。

行列とベクトルの設計に関する考慮事項 (HDL Coder)

FPGA ターゲットの効率的な乗算演算と除算演算のモデル化 (HDL Coder)

Guidelines for Using Rounding and Saturation Settings for Fixed-Point Data Types (HDL Coder)

逆数モードで Divide ブロックを使用する場合、次の制限が適用されます。

固定小数点タイプを使用する場合、入力と出力はスカラーでなければなりません。ベクトル入力を使用するには、浮動小数点型の入力と出力を使用します。

ブロックで [整数オーバーフローで飽和] オプションを選択する必要があります。

PLC コード生成

Simulink® PLC Coder™ を使用して構造化テキスト コードを生成します。

固定小数点の変換

Fixed-Point Designer™ を使用して固定小数点システムの設計とシミュレーションを行います。

バージョン履歴

R2006a より前に導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)