Dot Product

2 つのベクトルのドット積を生成

ライブラリ:

Simulink /

Math Operations

HDL Coder /

Math Operations

説明

Dot Product ブロックは入力ベクトルのドット積を生成します。スカラー出力 y は、次の MATLAB® 演算に等しくなります。

y = sum(conj(u1) .* u2 )

ここで、u1 と u2 は入力ベクトルを表します。入力はベクトル、列ベクトル (1列の行列)、または、スカラーになることがあります。入力が共にベクトルまたは列ベクトルの場合、それらは同じ長さでなければなりません。u1 と u2 が共に列ベクトルである場合、ブロックは MATLAB 式 u1'*u2 と等価な出力をします。

入力ベクトルの要素は、実数または複素数値の信号です。出力の信号タイプ (複素数または実数) は、入力の信号タイプに依存します。

| 入力 1 | 入力 2 | 出力 |

|---|---|---|

| 実数 | real | real |

| real | complex | complex |

| 複素数 | 実数 | complex |

| complex | complex | 複素数 |

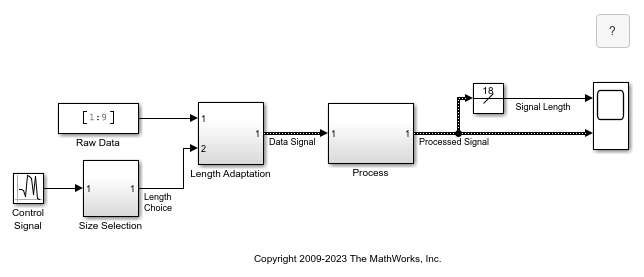

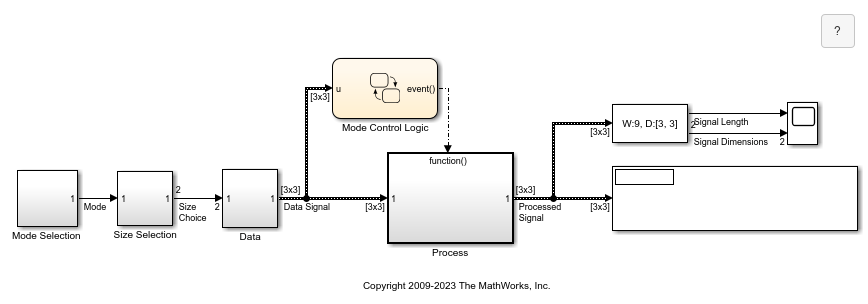

例

端子

入力

ドット積計算に対する 1 番目のオペランドを表す信号。

データ型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

ドット積計算に対する 2 番目のオペランドを表す信号。

データ型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

出力

2 つの入力信号のドット積計算から得られる出力信号。

データ型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

パラメーター

すべての入力が異なるデータ型をもつようにするには、このチェック ボックスをオフにします。

プログラムでの使用

ブロック パラメーター: InputSameDT |

| 型: 文字ベクトル |

値: 'on' | 'off' |

既定の設定: 'on' |

ソフトウェアでチェックする出力範囲の下限値。

最小値を使用して以下が行われます。

一部のブロックに対するパラメーター範囲のチェック (ブロック パラメーターの最小値と最大値の指定を参照)

シミュレーション範囲のチェック (信号範囲の指定およびシミュレーション範囲のチェックの有効化を参照)

固定小数点データ型の自動スケーリング

モデルから生成するコードの最適化。この最適化により、アルゴリズム コードが削除され、SIL やエクスターナル モードなどの一部のシミュレーション モードの結果に影響を与えることがあります。詳細については、Optimize using the specified minimum and maximum values (Embedded Coder)を参照してください。

ヒント

[出力の最小値] により、実際の出力信号が飽和する (またはクリップされる) ことはありません。代わりに、Saturation ブロックを使用してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | OutMin |

| 値: | '[]' (既定値) | scalar in quotes |

Simulink® が有限で実数の double のスカラー値としてチェックする出力範囲の上限値を指定します。

メモ

このブロックのデータ型としてバス オブジェクトを指定した場合、ブロックのバス データの最大値を設定しないでください。Simulink はこの設定を無視します。代わりに、データ型として指定したバス オブジェクトのバス要素の最大値を設定します。バス要素の [最大値] パラメーターの詳細については、Simulink.BusElement を参照してください。

Simulink は、最大値を使って以下を行います。

一部のブロックに対するパラメーター範囲のチェック (ブロック パラメーターの最小値と最大値の指定を参照)

シミュレーション範囲のチェック (信号範囲の指定およびシミュレーション範囲のチェックの有効化を参照)

固定小数点データ型の自動スケーリング

モデルから生成するコードの最適化。この最適化により、アルゴリズム コードが削除され、SIL やエクスターナル モードなどの一部のシミュレーション モードの結果に影響を与えることがあります。詳細については、Optimize using the specified minimum and maximum values (Embedded Coder)を参照してください。

メモ

[出力の最大値] により、実際の出力信号が飽和する (またはクリップされる) ことはありません。代わりに、Saturation ブロックを使用してください。

プログラムでの使用

ブロック パラメーター: OutMax |

| 型: 文字ベクトル |

| 値: スカラー |

既定の設定: '[ ]' |

出力のデータ型を選択します。型は継承されるか、直接指定されるか、Simulink.NumericType などのデータ型オブジェクトとして表現されます。詳細については、信号のデータ型の制御を参照してください。

継承オプションを選択すると、ブロックは次のように動作します。

継承: 内部ルールによる継承— Simulink は、組み込みターゲット ハードウェアのプロパティを考慮しつつ、数値の精度、パフォーマンス、および生成コードのサイズのバランスが取れるように、データ型を選択します。組み込みターゲット ハードウェアの設定を変更すると、内部ルールにより選択されるデータ型が変更される可能性があります。たとえば、ブロックがint8型の入力にint16のゲインを乗算し、ターゲット ハードウェア タイプとして[ASIC/FPGA]が指定されている場合、出力データ型はsfix24です。ターゲット ハードウェアとして[Unspecified (assume 32-bit Generic)](汎用 32 ビット マイクロプロセッサ) が指定された場合、出力データ型はint32です。ターゲット マイクロプロセッサによって指定される語長では出力範囲に対応できない場合、Simulink は診断ビューアーにエラーを表示します。コードの効率と数値の精度が、ソフトウェアにより同時に最適化されるとは限りません。内部ルールが、数値精度またはパフォーマンスに対する要求を満たさない場合は、以下のいずれかを行ってください。

出力データ型を明示的に指定する。

単に

[継承: 入力と同じ]を選択します。fixdt(1,32,16)のように既定のデータ型を明示的に指定し、固定小数点ツールを使用してモデルにデータ型を推奨する。詳細については、fxptdlg(Fixed-Point Designer) を参照してください。独自の継承ルールを指定するには、

[継承: 逆伝播による継承]を使用し、Data Type Propagation ブロックを使用します。このブロックの使い方の例については、Signal Attributes ライブラリの Data Type Propagation Examples ブロックを参照してください。

メモ

入力が単精度よりも小さい浮動小数点データ型の場合、

[継承: 内部ルールによる継承]は単精度より小さい浮動小数点の出力型を継承するコンフィギュレーション パラメーターの設定によって変わります。データ型の符合化に必要なビット数が単精度データ型の符合化に必要な 32 ビットより少ない場合、データ型は単精度より小さくなります。たとえば、halfとint16は単精度より小さくなります。継承: 逆伝播による継承— 駆動ブロックのデータ型を使用します。継承: 1 番目の入力と同じ— 1 番目の入力信号のデータ型を使用します。

プログラムでの使用

ブロック パラメーター: OutDataTypeStr |

| 型: 文字ベクトル |

値: 'Inherit: Inherit via internal rule | 'Inherit: Same as first input' | 'Inherit: Inherit via back propagation' | 'double' | 'single' | 'half' | 'int8' | 'uint8' | 'int16' | 'uint16' | 'int32' | 'uint32' | 'int64' | 'uint64' | 'fixdt(1,16)' | 'fixdt(1,16,0)' | 'fixdt(1,16,2^0,0)' | '<data type expression>' |

既定の設定: 'Inherit: Inherit via internal rule' |

固定小数点ツールや固定小数点アドバイザーによる変更を避けるために、このブロックの出力データ型の設定をロックします。詳細については、[出力データ型の設定をロックする] の使用 (Fixed-Point Designer)を参照してください。

プログラムでの使用

ブロック パラメーター: LockScale |

| 型: 文字ベクトル |

値: 'off' | 'on' |

既定の設定: 'off' |

固定小数点演算の丸めモードを指定します。詳細については、丸めモード (Fixed-Point Designer)を参照してください。

ブロック パラメーターは常に最近傍の表現可能な値に丸められます。ブロックパラメーターの丸めを直接制御するには、MATLAB の丸め関数を使用する式をマスク フィールドに入力します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RndMeth |

| 値: | 'Floor' (既定値) | 'Ceiling' | 'Convergent' | 'Nearest' | 'Round' | 'Simplest' | 'Zero' |

オーバーフローで飽和するかラップするかを指定します。

on— オーバーフローは、データ型が表現できる最小値または最大値のいずれかに飽和します。off— オーバーフローは、データ型によって表現される適切な値にラップされます。

たとえば、符号付き 8 ビット整数 int8 で表現できる最大値は 127 です。この最大値を超えるブロックの演算結果により 8 ビット整数のオーバーフローが発生します。

このパラメーターがオンになっていると、ブロック出力は 127 で飽和します。同様に、ブロック出力は最小出力値である -128 で飽和します。

このパラメーターをオフにすると、オーバーフローを引き起こした値は

int8として解釈され、意図しない結果が引き起こされる可能性があります。たとえば、int8として表されるブロック結果 130 (バイナリで 1000 0010) は -126 です。

ヒント

モデルでオーバーフローが発生する可能性があり、生成コードに飽和保護を明示的に組み込む必要があるときには、このパラメーターをオンにすることを検討してください。

生成コードの効率を最適化する場合には、このパラメーターをオフにすることを検討してください。このパラメーターをオフにすると、ブロックが範囲外の信号を処理する方法を指定しすぎないようにする点でも役立ちます。詳細については、信号範囲のエラーのトラブルシューティングを参照してください。

このパラメーターをオンにすると、飽和は出力や結果だけでなく、このブロックの内部演算すべてに適用されます。

通常、オーバーフローが可能ではない場合は、コード生成プロセスで検出されます。この場合、コード ジェネレーターでは飽和コードは生成されません。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | SaturateOnIntegerOverflow |

| 値: | 'off' (既定値) | 'on' |

ブロックの特性

データ型 |

|

直達 |

|

多次元信号 |

|

可変サイズの信号 |

|

ゼロクロッシング検出 |

|

詳細

Simulink Coverage™ ライセンスがある場合、[整数オーバーフローで飽和] (Simulink Coverage) パラメーターを選択すると、Dot Product ブロックは整数オーバーフローで飽和カバレッジの対象になります。詳細については、整数オーバーフローで飽和カバレッジ (Simulink Coverage)を参照してください。

拡張機能

C/C++ コード生成

Simulink® Coder™ を使用して C および C++ コードを生成します。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

| アーキテクチャ | 説明 |

|---|---|

線形 (既定値) | 積の和を計算する加算器の線形チェーンを生成します。 |

ツリー | 積の和を計算する加算器のツリー構造を生成します。 |

| 一般 | |

|---|---|

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| SynthesisAttributes | モデルのブロックとブロック出力信号の合成属性を指定します。生成された HDL コードには、これらの属性が含まれます。詳細については、SynthesisAttributes (HDL Coder)を参照してください。 |

| ネイティブ浮動小数点 | |

|---|---|

| HandleDenormals | HDL Coder で追加のロジックを挿入して設計で非正規数を処理するかどうかを指定します。非正規数とは、その大きさが仮数の先頭にゼロを付けずに表現できる最小の浮動小数点数より小さい数値のことです。既定の設定は |

| LatencyStrategy | 浮動小数点演算子について、設計内のブロックを |

| MantissaMultiplyStrategy | コード生成中に仮数乗算演算を実装する方法を指定します。さまざまな設定を使用することで、ターゲット FPGA デバイスでの DSP の使用方法を制御できます。既定の設定は |

PLC コード生成

Simulink® PLC Coder™ を使用して構造化テキスト コードを生成します。

固定小数点の変換

Fixed-Point Designer™ を使用して固定小数点システムの設計とシミュレーションを行います。

バージョン履歴

R2006a より前に導入[SynthesisAttributes] HDL ブロック プロパティを使用して、ブロックとその出力信号の合成属性を指定します。HDL Coder は、生成される HDL コードにこれらの属性を含めます。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)