このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

SystemVerilogアサーションと機能カバレッジを生成する

SystemVerilog DPI コンポーネント生成と Universal Verification Methodology (UVM) テストベンチ生成ワークフローを使用すると、生成された SystemVerilog で Simulink® 検証モデルを再利用できます。Assertion (Simulink) や Check Dynamic Lower Bound (Simulink) などの Simulink モデル検証ブロックと verify (Simulink Test) ステートメントの呼び出しにより、生成された SystemVerilog にエラー チェックと機能カバレッジ ポイントが作成されます。

Simulink アサーションまたは verify 呼び出しが失敗すると、デフォルトで SystemVerilog エラーが生成されます。どちらかが成功すると、PASS 結果をログに記録する SystemVerilog カバー ポイントが生成されます。アサーションと verify ステートメントの動作は、SystemVerilog コマンドライン引数と HDL Verifier アサーション ブロックを使用してカスタマイズできます。カスタマイズの詳細については、アサーションのカスタマイズ を参照してください。

Simulink Testベンチモデルを作成する

Simulink で、テスト対象デバイス (DUT) のモデルを作成し、そのモデルのテスト ベンチを作成します。次のように、Simulink / モデル検証ライブラリのアサーション ブロックと、Simulink Test ライブラリの verify ステートメントを含むブロックを組み合わせて使用できます。

verify(Simulink Test) 声明Model Verification (Simulink) ライブラリからのブロック

HDL Verifier™ Assertion ブロック

Simulink Test シーケンスを作成する

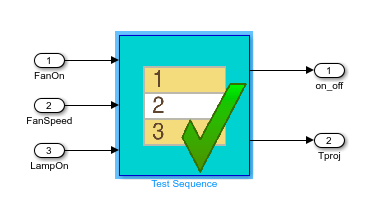

テスト ベンチ モデルに、次のブロックを 1 つ以上追加して、verify ステートメントを含めます。

Test Assessment (Simulink Test)

Test Sequence (Simulink Test)

Chart (Stateflow)

テスト ステップを作成および編集するには、Test Sequence エディター (Simulink Test) を使用します。テスト シーケンスでは、テスト ステップと評価の定義 (Simulink Test) で説明されているように、verify ステートメントを使用してシミュレーションを評価します。

verify ステートメントと Test Sequence ブロックは、Simulink での一時的なチェックを表します。SystemVerilog DPI コンポーネントを生成すると、生成された C コード内に時相ロジックが配置されます。SystemVerilog ラッパーには、検証条件に違反したときにトリガーされる即時アサーションが含まれています。

Simulink モデル検証ブロックを含める

Simulink / Model Verification (Simulink) ライブラリからこれらのアサーション ブロックを含めることもできます。

Assertion (Simulink)

Check Dynamic Gap (Simulink)

Check Dynamic Range (Simulink)

Check Static Gap (Simulink)

Check Static Range (Simulink)

Check Dynamic Lower Bound (Simulink)

Check Dynamic Upper Bound (Simulink)

Check Input Resolution (Simulink)

Check Static Lower Bound (Simulink)

Check Static Upper Bound (Simulink)

Check Discrete Gradient (Simulink)

さらに、HDL Verifier Assertion ブロックを組み込んでカスタマイズ可能なアサーションを作成することもできます。HDL Verifier Assertion ブロックを使用する例については、Simulink からネイティブ SystemVerilog アサーションを生成する を参照してください。

SystemVerilog では、すべてのモデル検証ブロックと verify ステートメントがアサーションとカバレッジ ポイントにマッピングされます。カバレッジ目標を調整したり、特定のアサーションをフィルタリングしたり、各検証ステートメントの詳細情報を表示したりできます。

モデル内で複数の verify ステートメントとアサーション ブロックを使用できます。

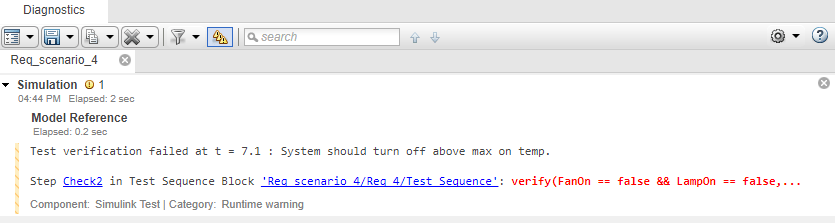

Simulink で設計をシミュレートする場合、アサーションまたは verify 評価が失敗するとシミュレーションで警告が表示されます。

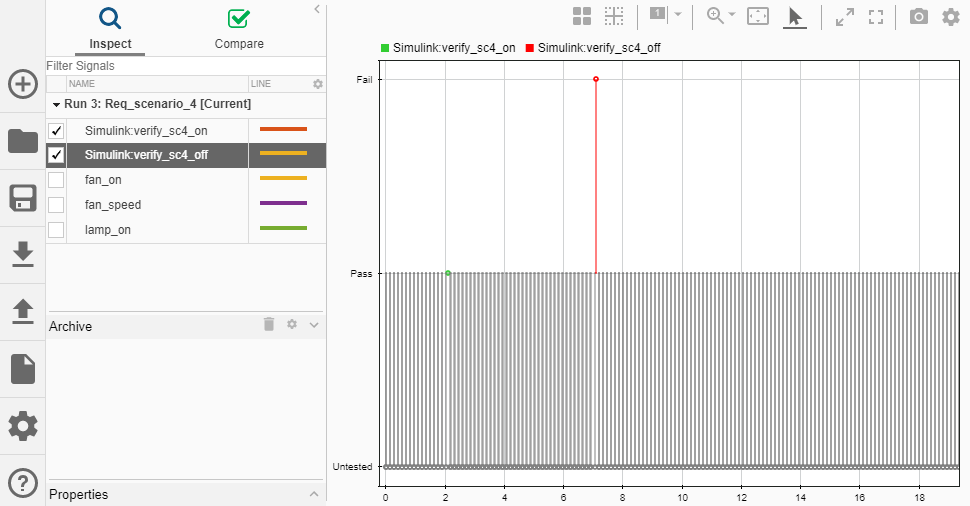

Simulation Data Inspector (Simulink) を使用してシミュレーション結果を表示および検査できます。MATLAB® コマンド プロンプトでこのコードを入力して、Simulation Data Inspector を開きます。

Simulink.sdi.view

時間の経過に伴う信号を表示するには、Simulation Data Inspector の左側のペインで信号を選択します。

アサーションのカスタマイズ

SystemVerilog 即時アサーションは、次の 2 つの方法でカスタマイズできます。

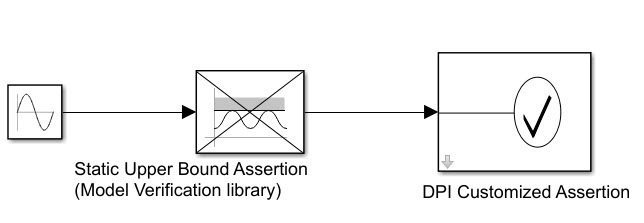

HDL Verifier Assertion ブロックを含め、生成された SystemVerilog 即時アサーションをカスタマイズします。アサーションが失敗したときにカスタム メッセージを設定し、アサーションが失敗したときに警告、エラー、またはカスタム コマンドのいずれかを選択できます。HDL Verifier Assertion ブロックを使用する例については、Simulink からネイティブ SystemVerilog アサーションを生成する を参照してください。結果はこの図のようになります。

モデル検証ライブラリからのアサーションをカスタマイズするには、次の手順に従って、ブロック出力をカスタマイズ可能な HDL Verifier Assertion ブロックに接続します。

Simulink / モデル検証ライブラリからブロックをモデルに追加します。

ブロック マスクを開き、次のパラメータを設定します (この図に示すように)。

冗長なアサーション出力を防ぐために、Enable assertion パラメータをクリアします。

アサーションをキャプチャするブール出力信号を作成するには、Output assertion signal パラメータを選択します。

HDL Verifier / For Use with DPI-C SystemVerilog ライブラリから Assertion ブロックを追加し、モデル検証ブロックの出力信号を Assertion ブロックの入力ポートに接続します。

アサーション生成ワークフロー の例の手順に従って、Assertion ブロックをカスタマイズします。

結果はこの図のようになります。

UVM または SystemVerilog DPI コンポーネントを生成する

コード生成用のモデルを構成する

[構成パラメータ] ダイアログ ボックスの左側のペインで、Code Generation を選択します。Target Selection の場合は、System Target File を systemverilog_dpi_grt.tlc に設定するか、Embedded Coder® を使用する場合は systemverilog_dpi_ert.tlc に設定します。

左側のペインでSystemVerilog DPIを選択します。SystemVerilog Ports で、データ タイプと接続設定を設定します。[OK] をクリックします。

UVM または SystemVerilog DPI コンポーネントを生成する

メモ

UVM または DPI コンポーネントを生成するには、アサーションまたはテスト ブロックが Simulink サブシステム内にある必要があります。

Simulink で、テスト シーケンスを含むサブシステム ブロックを右クリックし、C/C++ Code 、 Build This Subsystem を選択します。開いたダイアログボックスでBuildをクリックします。

あるいは、MATLAB コマンドラインを使用して DPI コンポーネントを生成することもできます。システムを構築するには、slbuild (Simulink) 関数を使用します。たとえば、「My_verify_tst」という名前のサブシステムを構築するには、MATLAB コマンド ラインにこのコードを入力します。

slbuild('My_verify_tst');uvmbuild 関数を使用して UVM テストベンチを生成することもできます。テスト モデルに verify ステートメントが含まれている場合、それらは UVM 環境内のアサーションにマップされ、カバレッジ データが収集されます。

生成されたコンポーネントでHDLシミュレーションを実行する

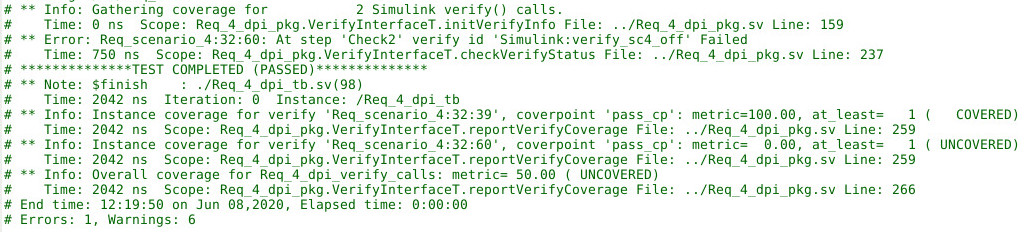

現在のフォルダーを、HDL シミュレータ インストールのコード生成フォルダーの下にある dpi_tb フォルダーに変更します。HDL シミュレーターを起動し、生成されたスクリプトを実行してシミュレーションを開始します。シミュレーション出力は Simulink 出力と一致しています。

シミュレーションが完了すると、アサーションごとにカバレッジ情報が表示されます。デフォルトでは、アサーションは少なくとも 1 回評価された場合にカバーされていると見なされます。

HDL シミュレーションの実行に関する追加情報については、生成されたコンポーネントをSimulinkデータに対して検証する を参照してください。

フィルターアサーションとカバレッジレポート

生成された各エラーまたは警告には、その発生元を識別する一意の名前が表示されます。その番号は、そのブロックの一意の Simulink 識別子 (SID) です。たとえば、このログは、SID Req_scenario_4:32:60 のブロックによって生成されたエラーを示しています。

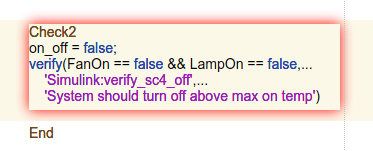

# ** Error: Req_scenario_4:32:60: At step 'Check2' verify id 'Simulink:verify_sc4_off' Failed

テスト シーケンスには、verify 評価を利用するステップが複数ある場合や、シミュレーションからの警告を記録する DPI コンポーネントが複数ある場合があります。テスト モデルでは、コマンド ラインで関連する SID をプラス引数として指定し、SID を -1 と等しくすることで、特定の verify チェックに対して生成された出力をフィルター処理できます。たとえば、SID Req_scenario_4:32:60 のすべての出力と機能カバレッジをオフにするには、HDL コマンド ラインで次のコードを入力します。

vsim -c -sv_lib ../Req_4 work.Req_4_dpi_tb +Req_scenario_4:32:60=-1

機能カバレッジ目標を調整する

SystemVerilog シミュレーション中に機能カバレッジを収集するには、アサーション ブロックと verify ステートメントを使用できます。uvmbuild または slbuild (Simulink) 関数を使用して SystemVerilog を生成した後、各アサーションのカバレッジ目標を定義します。SystemVerilog シミュレーションが完了したら、生成されたログ ファイルで結果を表示するか、サードパーティ ツールを使用して結果を抽出します。デフォルトのカバレッジ目標は、アサーションまたは verify 呼び出しの実行が少なくとも 1 回成功することです。

特定のアサーションの機能カバレッジ目標を増やすには、コマンド ラインで関連する SID をプラス引数として指定し、SID をカバレッジ目標に一致させます。たとえば、SID Req_scenario_4:32:60 を持つ verify ステートメントのカバレッジ目標を、デフォルトの 1 回の合格チェックから 2 回の合格チェックに増やすには、HDL コマンド ラインで次のコードを入力します。

vsim -c -sv_lib ../Req_4 work.Req_4_dpi_tb +Req_scenario_4:32:60=2

詳細モード

デフォルトでは、生成された DPI コンポーネントは、機能カバレッジ ポイントが評価されて失敗したときにエラーを出力します。機能カバレッジ ポイントによって生成された追加の出力を表示するには、HDL シミュレーション コマンド ラインで引数 +VERBOSE_VERIFY を入力します。この引数は、次の追加情報を追加します。

UNTESTED– 機能カバレッジポイントが評価されなかった場合PASSED– 機能カバレッジポイントが評価され、テストが合格したとき

たとえば、ModelSim® を使用する場合は、コマンド ラインにこのコードを入力します。

vsim -c -sv_lib ../Req_4 work.Req_4_dpi_tb +VERBOSE_VERIFY

生成された SystemVerilog エラーを Simulink ソースにトレースする

生成されたテスト シーケンスを使用して SystemVerilog シミュレーションを実行すると、ログ ファイルに警告とエラーが表示されます。特定の警告またはエラー出力の発生元となったブロックを識別するには、hilite_system (Simulink) 関数を使用します。

たとえば、SID Req_scenario_4:32:60 の警告を生成したブロックを強調表示するには、MATLAB コマンド ラインにこのコードを入力します。

hilite_system('Req_scenario_4:32:60');この図は、警告を作成した検証ステートメントとテスト シーケンス ブロックを強調表示しています。

参考

ブロック

- Test Sequence (Simulink Test) | Test Assessment (Simulink Test) | Chart (Stateflow) | Assertion (Simulink) | Check Dynamic Gap (Simulink) | Check Dynamic Range (Simulink) | Check Static Gap (Simulink) | Check Static Range (Simulink) | Check Dynamic Lower Bound (Simulink) | Check Dynamic Upper Bound (Simulink) | Check Input Resolution (Simulink) | Check Static Lower Bound (Simulink) | Check Static Upper Bound (Simulink) | Check Discrete Gradient (Simulink)

MATLAB 言語構文

- verify (Simulink Test)