このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

uvmbuild

Simulink モデルから UVM テストベンチを生成する

アドオンが必要: この機能には ASIC Testbench for HDL Verifier アドオンが必要です。

説明

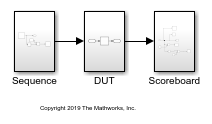

uvmbuild( は、ユニバーサル検証方法論 (UVM) テスト ベンチとテスト対象の動作設計 (DUT) を含む SystemVerilog トップ モジュールを生成します。UVM テスト ベンチには、シーケンス、スコアボード、モニター、およびドライバーが含まれています。dut,sequence,scoreboard)uvmbuild 関数は以下をマップします:

Simulink® DUT サブシステムを生成された SystemVerilog DPI 動作 DUT に

Simulink シーケンス サブシステムを UVM シーケンス ブロックに接続

Simulink スコアボード サブシステムを UVM スコアボードに

uvmbuild(___, は、前の構文の入力引数に加えて、1 つ以上の名前と値のペアの引数を使用してオプションを指定します。たとえば、Name,Value)'Driver','mySLTopModule/myDriver' は、'mySLTopModule/myDriver' として指定された Simulink サブシステムから UVM ドライバーを生成します。