このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

verify

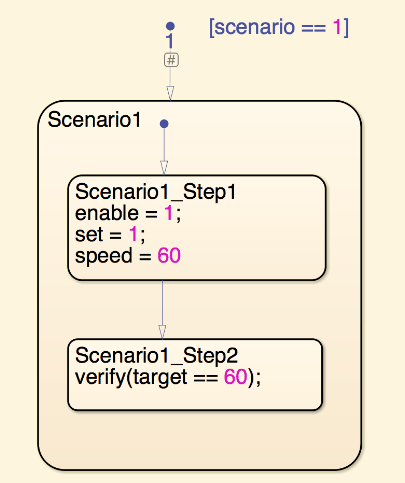

論理式を評価して結果を記録

説明

verify( は、スカラーの論理式 expression)expression を true または false として評価します。

verify( は、スカラーの論理式が失敗した場合に、指定されたエラー メッセージを返します。テスト マネージャーでテストを実行している場合、シミュレーション ログにエラー メッセージが表示されます。テスト マネージャーの外部でテストを実行している場合、診断ビューアーにメッセージが表示されます。expression,errorMessage)errorMessage は文字配列として指定します。sprintf を使用して書式を設定できます。Stateflow® チャートの string または文字配列では、sprintf による書式設定は使用できません。

メモ

リアルタイム環境では、verify ステートメントの失敗時に警告は生成されません。テスト マネージャーでリアルタイム テスト ケースを実行している場合は、[verify ステートメント] セクションにテスト ケース結果の失敗が表示されます。getVerifyRuns を使用して verify の実行に関する情報にアクセスすることもできます。

高速リスタート シミュレーション モードでテスト反復を実行している場合、診断ビューアー、テスト マネージャーの [ログ] セクション、テスト レポートに verify ステートメントからの情報、エラー、警告は出力されません。

verify( は、expression,identifier,errorMessage)identifier をテスト結果のラベルとして使用します。テスト マネージャーでテストを実行している場合、信号ラベルのテスト結果として identifier が使用されます。テスト マネージャーの外部でテストを実行している場合は、シミュレーション データ インスペクターや診断ビューアー (失敗時) にラベルが表示されます。identifier は、コロンで区切られた少なくとも 2 つの MATLAB® 識別子をもつ文字配列として指定します。

例

制限

verifyステートメントは以下では使用できません。連続時間更新を使用する Test Sequence ブロック。Test Sequence ブロックのデータは、ソルバーのステップ時間などの要因に依存することがあります。連続時間更新の場合、ブロックのデータと

verifyステートメントが更新されるタイミングに差が生じ、verifyステートメントの結果が予期しない結果になる可能性があります。モデルで連続時間を使用している場合に Test Sequence ブロックまたは Test Assessment ブロックでverifyステートメントを使用する際は、離散ブロックのサンプル時間を明示的に設定することを検討してください。Moore チャート、Mealy チャート、離散イベント チャート、または連続チャート

C をアクション言語として使用するチャート

チャート内のバインド アクション

チャート内の遷移アクションまたは条件アクション

チャート内の MATLAB 関数、グラフィカル関数、または真理値表

MATLAB Function ブロックまたは Truth Table ブロック

ラピッド アクセラレータ モードのシミュレーション

Simulink® Real-Time™ および HDL Verifier™ 以外のコード生成ターゲット

スタンドアロンの Stateflow チャート

verifyステートメントは出力を生成しないため、When分解構造のwhenの直後にverifyを条件として使用することはできません。When分解構造ステップのアクションとしてはverifyステートメントを使用できます。when 構造を使用したモデルのシミュレーションの検証を参照してください。並列テスト実行を使用してテストを実行し、テストで

verifyステートメントを使用している場合、テスト マネージャーで [モデル内で強調表示] ボタンは使用できません。

ヒント

verifyステートメントは、Test Sequence ブロック、Test Assessment ブロック、および Stateflow チャートで使用できます。チャートを使用するには Stateflow のライセンスが必要です。チャートでも、Test Sequence ブロックと同じ場所および実行モードで、同じコード生成ターゲットに対してverifyステートメントがサポートされます。verifyステートメントはテスト ケースの有無に関係なく使用できます。モデルにテスト ケースが含まれていない場合、シミュレーション データ インスペクターに結果が表示されます。モデルにテスト ケースが含まれている場合、テスト マネージャーに結果が表示されます。単一のタイム ステップで複数の式を検証するには、同じテスト ステップで

verifyステートメントを定義するか、サブステップを追加して各サブステップにverifyステートメントを追加します。テスト ステップの管理を参照してください。verifyステートメントで浮動小数点データを比較するときは、浮動小数点数に関する精度の制限を考慮してください。浮動小数点データを使用する必要がある場合は、検証の許容誤差を定義します。たとえば、verify(x == 5)の代わりに、0.001 の許容誤差内でxを検証します。詳細については、浮動小数点数を参照してください。verify(abs(x-5) < 0.001)

ターゲット ハードウェアでモデルをシミュレートするときのデータ転送を減らすには、テストされた

verifyステートメントの結果のみをログに記録し、テスト マネージャーとシミュレーション データ インスペクターにpassとfailの結果のみを表示するように選択できます。verifyのpassとfailの結果のみをログに記録するには、[テスト] タブまたは [ハーネス] タブの [テスト ケース] セクションで [Suppress Untested Results] をクリックします。あるいは、set_paramを使用してlogOnlyTestedVerifyResultsパラメーターを'on'に設定できます。たとえば、モデルmyModelについて、verify ステートメントのtestedの結果のみをログに記録するには次のようにします。このオプションを選択すると、モデル内のすべての Test Sequence ブロックまたは Chart ブロックに設定が適用されます。HDL Verifier を使用している場合、設定は適用されません。set_param(myModel,'logOnlyTestedVerifyResults','on')