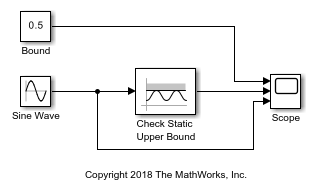

Check Static Upper Bound

信号が静的上限より小さい (またはオプションで等しい) かどうかのチェック

ライブラリ:

Simulink /

Model Verification

HDL Coder /

Model Verification

説明

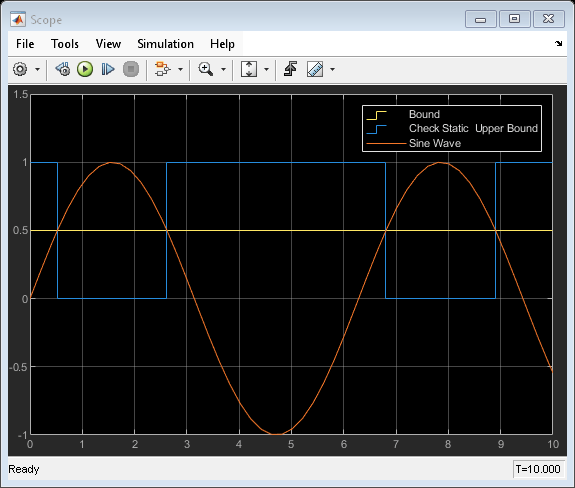

Check Static Upper Bound ブロックは、入力信号が各タイム ステップで指定された下限より小さい (またはオプションで等しい) かどうかをチェックし、比較後にアサーションを実行します。[上限] パラメーターは上限を定義します。入力信号が上限より小さい場合、アサーションは true (1) であり、ブロックは処理を行いません。そうでない場合、既定の設定ではブロックはシミュレーションを停止してエラー メッセージを返します。

入力信号および範囲はスカラー、ベクトル、または行列になります。入力および範囲は同じデータ型でなければなりません。ブロックは、信号によって異なる方法で入力の値を範囲と比較します。

スカラーをベクトルまたは行列と比較する場合、ブロックはスカラーを非スカラー入力信号または範囲の各要素と比較します。

ベクトル信号または行列信号をベクトルまたは行列の上限と比較する場合、ブロックは入力信号を範囲と要素単位で比較します。

入力信号および範囲が両方ともベクトルまたは行列であるモデルの場合、入力信号および範囲は次元が同じでなければなりません。

例

端子

入力

出力

パラメーター

ブロックの特性

データ型 |

|

直達 |

|

多次元信号 |

|

可変サイズの信号 |

|

ゼロクロッシング検出 |

|

拡張機能

バージョン履歴

R2006a より前に導入