このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA インザループ

実際のハードウェアで設計をテスト

シミュレータとボード間に FPGA インザループ リンクを作成すると、次のことが可能になります。

HDL 実装を Simulink® または MATLAB® のアルゴリズムに対して直接検証します。

Simulink または MATLAB からのデータとテストシナリオを FPGA 上の HDL デザインに適用します。

既存の HDL コードを Simulink または MATLAB で開発中のモデルと統合します。

FPGA インザループ (FIL) シミュレーションを使用する前に、ボードのサポート パッケージをダウンロードする必要があります。FPGAボードサポートパッケージをダウンロードを参照してください。あるいは、FIL シミュレーションで使用するカスタム ボード定義ファイルを手動で作成することもできます。FPGA ボードのカスタマイズを参照してください。

ボード サポート パッケージをダウンロードしたら、シミュレーション ワークフローを選択します。FPGAインザループシミュレーションワークフローを参照してください。FIL シミュレーションの仕組みについては、FPGAインザループ シミュレーション を参照してください。

アプリ

| HDL Verifier | HDL検証アーティファクトを生成し、Simulinkサブシステムから検証ワークフローに従います。 |

| FPGA インザループ ウィザード | 既存の HDL ファイルから FPGA インザループ (FIL) ブロックまたは System object を生成します。 |

| ロジック アナライザー | 遷移と状態を経時的に可視化、測定、解析します |

オブジェクト

hdlverifier.FILSimulation | MATLAB による FIL シミュレーション |

hdlverifier.FILFreeRunning | Free-running FIL simulation with MATLAB (R2024b 以降) |

関数

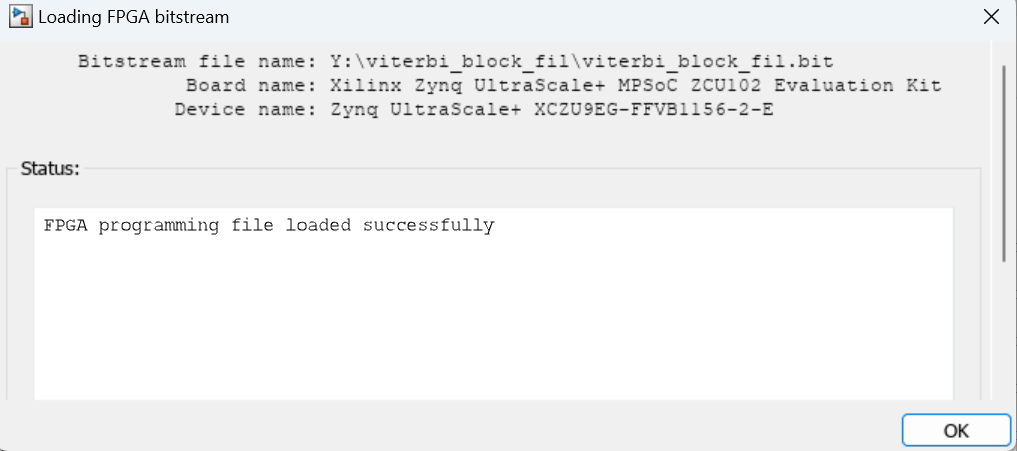

filProgramFPGA | プログラミングファイルをFPGAにロードする |

programFPGA | FILSimulation または FILFreeRunning システム オブジェクトに関連付けられたプログラミング ファイルを FPGA にロードします。 |

writePort | Send data to DUT ports (R2024b 以降) |

readPort | Receive data from DUT ports (R2024b 以降) |

ブロック

| FIL Simulation | Simulink の FPGA ハードウェア上で HDL コードをシミュレートする |

トピック

概要

- FPGAインザループシミュレーションワークフロー

ブロックまたは System object™ の生成を選択し、FIL ウィザードを使用するか HDL ワークフロー アドバイザーを使用するかを決定します。 - FPGAインザループ シミュレーション

FPGA インザループ (FIL) シミュレーションでは、Simulink または MATLAB ソフトウェアを使用して、既存の HDL コードの設計を実際のハードウェアでテストする機能が提供されます。

FILの要件と準備

- FILインターフェース生成のためのDUTの準備

ブロックおよび System object の FIL シミュレーションに関する DUT ガイドライン。 - FPGAボードサポートパッケージをダウンロード

FPGA ボード サポート パッケージには、FPGA インザループ (FIL) シミュレーション、FPGA data capture、または AXI manager でサポートされているすべてのボードの定義ファイルが含まれています。 - FPGA設計ソフトウェアツールのセットアップ

MATLAB パスを AMD®、 Microchip、および Intel® ソフトウェアに設定します。 - ガイド付きハードウェアセットアップ

FPGA インザループ、AXI マネージャー、または FPGA データ キャプチャで使用するためにハードウェアを構成するための自動サポート パッケージ セットアップ プロセスの手順について説明します。 - 手動ハードウェア設定

FIL 用のハードウェアとハードウェア ツールを準備するために必要な手順について説明します。 - ロジックアナライザを構成する

ロジック アナライザーで設定を調整します。

レガシーコードからFILインターフェースを生成する

- FILウィザードによるブロック生成

既存の HDL ソース ファイルから FPGA インザループ ブロックを生成し、FPGA 実装を Simulink シミュレーションに含めます。 - FIL ウィザードによるシステムオブジェクトの生成

既存の HDL ソース ファイルから FPGA インザループ System object を生成し、FPGA 実装を MATLAB シミュレーションに含めます。 - FPGA インザループを使用した PID コントローラーの HDL 実装の検証

この例では、HDL Verifier™ を使用して FPGA インザループ(FIL) アプリケーションを設定する方法を示します。

フリーランニングFIL

- What Is Free-Running FPGA-in-the-Loop?

Introduction and requirements for free-running FIL. - Execute Free-Running FPGA-in-the-Loop

Generate a free-running FPGA-in-the-Loop System object, then include the FPGA implementation in a MATLAB simulation. - Execute Free-Running FPGA-in-the-Loop Using HDL Workflow Advisor

Generate a free-running FPGA-in-the-Loop System object by using the HDL Workflow Advisor, then include the FPGA implementation in a MATLAB simulation.

MATLAB コードから FIL システム オブジェクトを生成する (HDL Coder ライセンスが必要)

- MATLAB 向け HDL ワークフロー アドバイザーによる FIL シミュレーション

HDL ワークフロー アドバイザーを使用して、FPGA インザループ System object とテスト ベンチを生成します。

Simulink モデルから FIL ブロックを生成する (HDL Coder ライセンスが必要)

- HDL ワークフロー アドバイザーを使用したテスト ベンチの生成とコード カバレッジの有効化 (HDL Coder)

HDL ワークフロー アドバイザーを使用して生成された HDL コード用にテスト ベンチとコード カバレッジを生成します。 - Simulink 向け HDL ワークフロー アドバイザーによる FIL シミュレーション

HDL ワークフロー アドバイザーを使用して FPGA インザループ モデルを生成します。

トラブルシューティング

一般的なエラー メッセージと問題の修正。