このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

コシミュレーションと FPGA インザループによるビデオ アルゴリズムの検証と高速化

この例では、コシミュレーションを使用してビデオ処理アルゴリズムを検証し、FPGA インザループ (FIL) を使用してこのプロセスを高速化する方法を示します。このプロセスでは、RGB ビデオ入力を 24 フレーム/秒 (FPS) でシャープ化する単純なシステムを分析します。FIR フィルターを使用して RGB ビデオ フィードを強化します。次に、設計を検証するために、HDL Verifier™ Toolbox に用意されているシミュレータベースおよびハードウェアベースの検証機能を活用します。

要件と前提条件

FPGA 設計ソフトウェア (Xilinx® Vivado® 設計スイートまたは Intel® Quartus® Prime 設計ソフトウェア)。

サポートされている FPGA 開発ボードおよびアクセサリの 1 つ。サポートされているハードウェアの詳細については、FPGA検証でサポートされているFPGAデバイス を参照してください。

イーサネットを使用した接続の場合:ホスト コンピュータにインストールされたギガビット イーサネット アダプタ、ギガビット イーサネット クロスオーバー ケーブル。

JTAGを使用した接続の場合:Intel FPGA ボード用の USB Blaster I または II ケーブルとドライバー。Xilinx FPGA ボード用の JTAG ケーブルとドライバー。

PCI Express®を使用した接続の場合:ホスト コンピュータの PCI Express スロットにインストールされた FPGA ボード。

Xilinx の Vivado シミュレーター。

MATLAB® および FPGA 設計ソフトウェアは、コンピューターにローカルにインストールすることも、ネットワークにアクセス可能なデバイスにインストールすることもできます。ネットワークからソフトウェアを使用する場合は、FPGA 開発ボードにプライベート ネットワークを提供するために、コンピューターに 2 番目のネットワーク アダプターをインストールする必要があります。ネットワーク アダプターのインストール方法については、コンピューターのハードウェアおよびネットワーク ガイドを参照してください。

コシミュレーションまたは FIL を使用する前に、FPGA 設計ソフトウェアにアクセスするためのシステム環境が適切に設定されていることを確認してください。hdlsetuptoolpath (HDL Coder)

Simulink モデルを開いて実行する

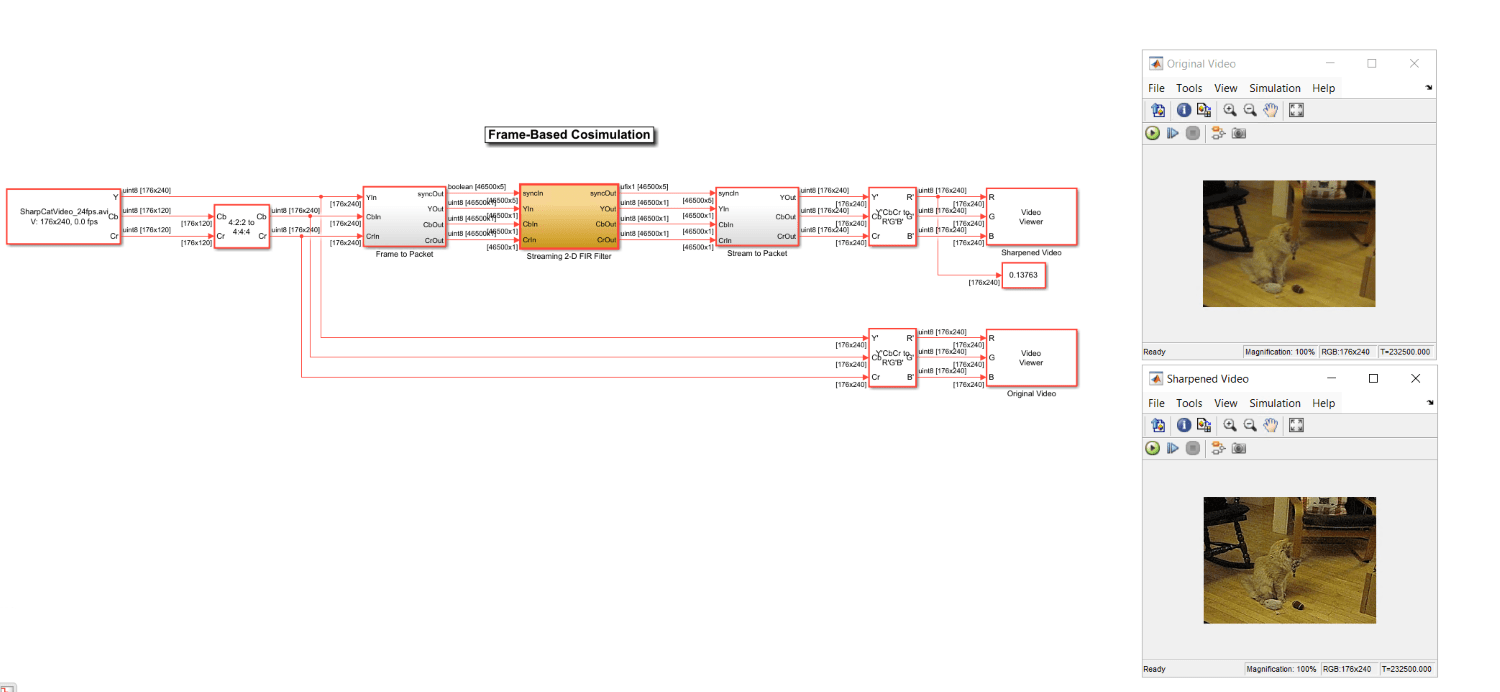

sim_videosharp モデルを開き、シミュレーションを実行します。

処理するデータ量が多いため、シミュレーションはスムーズではありません。フレームレートは1.70 FPSです。パフォーマンスはホストマシンによって異なる場合があります。この例では、後ほど FIL を使用してシミュレーション速度を向上させます。

HDL コードの生成

Streaming 2-D FIR Filter サブシステムの HDL コードを生成するには、次の手順に従います。

a.DUT というラベルの付いたブロックを右クリックします。

b.コンテキスト メニューで HDL コード > サブシステムの HDL の生成 を選択します。

あるいは、MATLAB で次のコマンドを入力して HDL コードを生成することもできます。

makehdl('sim_videosharp/Streaming 2-D FIR Filter ')

videosharp_hdlsrc フォルダーにある事前に生成された HDL ファイルを使用することもできます。

FPGA設計ソフトウェアのセットアップ

Xilinx FPGAボードの場合は、

hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', 'C:\Xilinx\Vivado\2022.1\bin');

この例では、Xilinx Vivado 実行可能ファイルが C:\Xilinx\Vivado\2022.1\bin にあることを前提としています。必要に応じて実際のインストール場所に置き換えてください。

Intelボードの場合は、

hdlsetuptoolpath('ToolName','Altera Quartus II','ToolPath','C:\Intel\quartus\22.4\bin64');

この例では、Intel Quartus Prime 実行可能ファイルが C:\Intel\quartus\22.4\bin64 にあることを前提としています。必要に応じて実際のインストール場所に置き換えてください。

コシミュレーションを使用したアルゴリズムの検証

この例では、コシミュレーションの準備が整った Framed_cosim_videosharp.slx モデルが提供されます。テスト対象の設計 (DUT) をこの生成されたコシミュレーション ブロックに置き換えます。

コシミュレーション ブロックを生成するには、コシミュレーション ウィザード ツールを使用します。コシミュレーション ブロックを生成し、この生成されたブロックで DUT を置き換える手順については、Simulink HDL コシミュレーション入門 を参照してください。

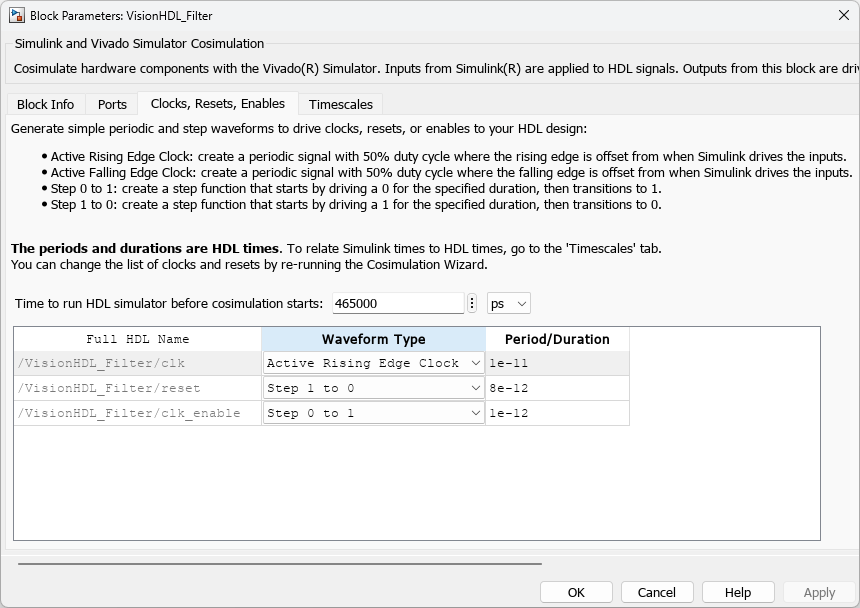

この例では、Framed_cosim_videosharp.slx モデルを開きます。コシミュレーションの開始時間設定を確認するには、Streaming 2-D FIR FIlter /VisionHDL_Filter サブシステム ブロックをダブルクリックし、[クロック、リセット、および有効化] タブに移動します。

ダイアログ ボックスを閉じてモデルを実行します。

コシミュレーション ブロックによってビデオが鮮明になり、HDL ファイルがアルゴリズムと同じように動作することが検証されます。

FILでプロセスを加速

FIL ブロックを生成するには、docid:hdlv_ref#bvkr_b1-1 FPGA インザループウィザード ツールを使用します。FIL ブロックを生成するには、FILウィザードによるブロック生成 の例の手順 1 から 8 に従います。この例の最上位 HDL モジュールは Streaming 2-D FIR Filter.v であることに注意してください。

これらの手順を完了すると、新しいモデルに Streaming_2_D_FIR_Filter という名前の FIL ブロックが生成されます。Simulink モデルを完成させて FIL シミュレーションを実行するには、次の手順に従います。

FIL 用のオープンで完全な Simulink モデル

a.FIL_videosharp.slx モデルを開きます。

b.以前に生成した FIL ブロックを、Streaming 2-D FIR Filter/HDL DUT サブシステムの代わりに FIL_videosharp.slx モデルにコピーします (「これを FIL ブロックに置き換えます」と表示されます)。

FIL ブロックを構成する

a.FIL_videosharp.slx モデルの FIL ブロックをダブルクリックして、ブロック マスクを開きます。

b.[ロード]をクリックします。

c. ブロックマスクを閉じるには、OK をクリックします。

FIL シミュレーションを実行する

シミュレーションを実行し、パフォーマンスの向上を確認します。

フレーム レートは約 10.30 FPS であり、sim_videosharp と比較してほぼ 6 倍増加していることがわかります。パフォーマンスはインターフェースとハードウェア ボードによって異なります。この例では、イーサネット インターフェイスと Xilinx Kintex®-7 FPGA KC705 評価キットを使用します。

まとめ

この例では、RGB ビデオ入力を処理して品質を向上させる Simulink モデルを開発します。コシミュレーション ブロックを組み込むことで設計が検証され、FIL ブロックを組み込むことでプロセスが加速されます。フレーム レートは約 6 倍に増加し、これは大容量データを扱うビデオ処理アルゴリズムにとって大きな改善となります。このパフォーマンスは、使用するインターフェースとハードウェア ボードによって異なります。