このページは機械翻訳を使用して翻訳されました。元の英語を参照するには、ここをクリックします。

Simulink HDL コシミュレーション入門

Simulink ® 環境でコシミュレーション Wizard を使用して HDL Verifier ™ アプリケーションをセットアップします。

コシミュレーションウィザードは、コシミュレーションブロック、System object ™、または MATLAB ® スクリプトの生成プロセスをガイドするグラフィカル ユーザー インターフェイス (GUI) です。

この例では、Simulink と HDL シミュレータを使用して、Verilog® で記述されたレイズド コサイン フィルターの設計を検証します。レイズドコサイン フィルタは、デジタル通信システムのパルス整形フィルタとしてよく使用されます。変調パルスの入力に対して符号間干渉 (ISI) は発生しません。

このレイズド コサイン フィルタの機能を検証するために、Simulink テストベンチが提供されています。このテストベンチは、テスト対象の HDL 設計 (DUT) への入力を生成し、入力と出力の両方の波形をプロットします。

コシミュレーションウィザードは、このレイズド コサイン フィルターの提供された Verilog ファイルを入力として受け取ります。また、各ステップでコシミュレーションを設定するために必要なユーザー入力も収集します。例の最後に、コシミュレーションウィザードは、Simulink モデル内の HDL 設計を表す Simulink ブロック、HDL 設計をコンパイルする MATLAB スクリプト、およびコシミュレーション用の HDL シミュレータを起動する MATLAB スクリプトを生成します。シミュレーション中に、この HDL フィルターの入力波形と出力波形を Simulink で確認できます。

コシミュレーション ウィザードは、AMD® Vivado®、Siemens® ModelSim™ または Questa™、Cadence® Xcelium™、および Synopsys® VCS® HDL シミュレータをサポートしています。

要件と前提条件

この例では、レジスタ転送レベル (RTL) 設計を検証するために、Simulink とこれらの HDL シミュレーターのいずれかが必要です。

AMDのVivadoシミュレータ

シーメンスのModelSimまたはQuesta

Cadence の Xcelium

Synopsys の VCS

コシミュレーションウィザードを起動

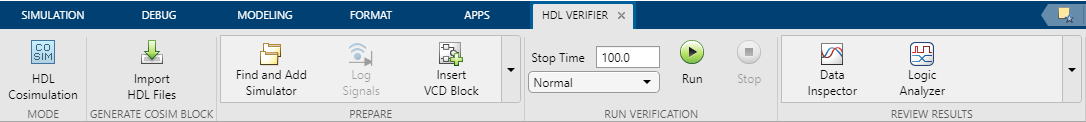

モデルからコシミュレーション Wizard を起動するには、Simulink ツールストリップの Apps タブを選択し、HDL Verifier をクリックします。このアクション、HDL Verifier タブが Simulink ツールストリップに追加されます。次に、モードセクションで、HDLコシミュレーションを選択します。Cosim ブロックの生成 セクションで HDL ファイルのインポート をクリックします。

コシミュレーション ウィザードでHDL Cosimulation ブロックを構成する

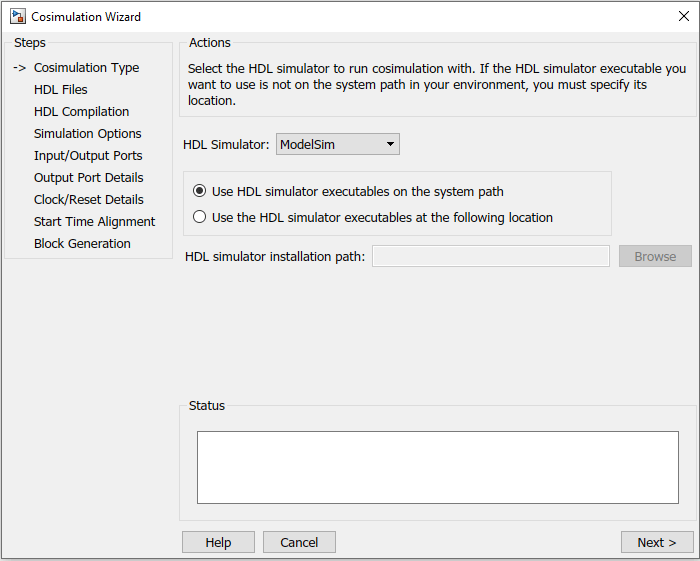

「コシミュレーションタイプ」ページで、次の手順を実行します。

1.a)。ModelSim または Questa を使用している場合は、HDL シミュレータ オプションを ModelSim のままにしておきます。

b)。Xcelium を使用している場合は、HDL シミュレータ オプションを Xcelium に変更します。

c)。Vivado シミュレータを使用している場合は、HDL シミュレータ オプションを Vivado Simulator に変更します。

d)。VCS を使用している場合は、HDL シミュレータ オプションを VCS に変更します。

2. HDL シミュレータ実行ファイルがシステム パス上に表示される場合は、デフォルト オプション システム パス上の HDL シミュレータ実行ファイルを使用する オプションのままにします。これらの実行可能ファイルがパス上に表示されない場合は、参照 ボタンをクリックして、これらの実行可能ファイルの場所を指定します。VCS の場合は、VCS インストール パス (VCS_HOME) を指定します。

次へ をクリックして、HDL ファイル ページに進みます。

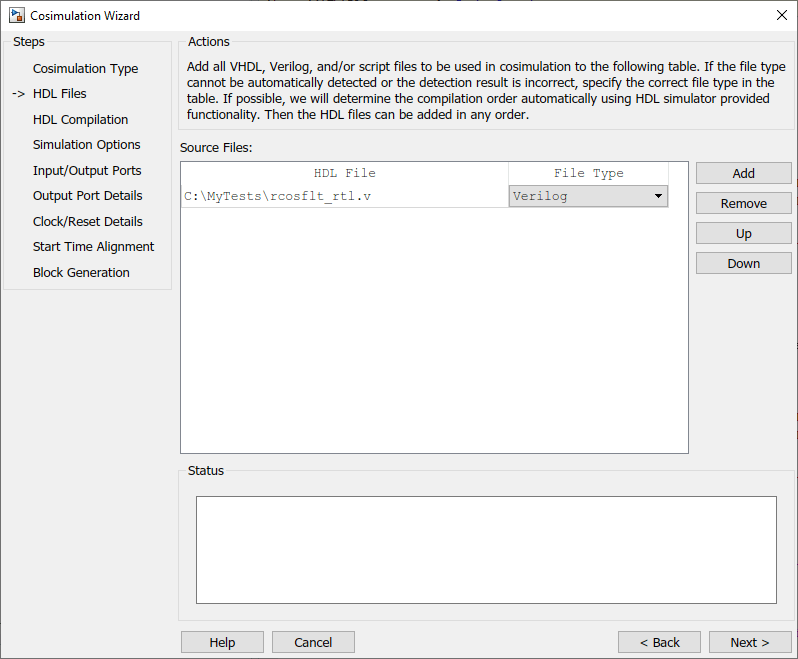

HDL ファイル ページで、次の手順を実行します。

ModelSim、Xcelium、または Vivado シミュレーター

追加 をクリックし、Verilog の場合は

rcostflt_rtl.v、VHDL の場合はrcosflt_rtl.vhdを選択します。ファイル リスト内のファイルを確認し、ファイルの種類が期待どおりに識別されていることを確認します。

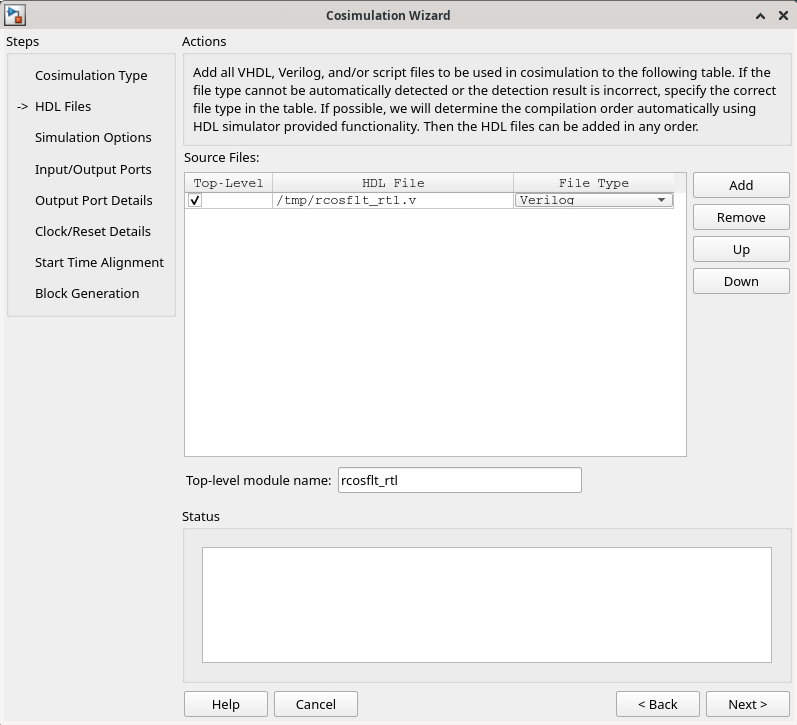

VCS

追加 をクリックし、Verilog の場合は

rcostflt_rtl.v、VHDL の場合はrcosflt_rtl.vhdを選択します。ファイル リスト内のファイルを確認し、ファイルの種類が期待どおりに識別されていることを確認します。

トップレベルモジュールとして

rcostflt_rtl.vを選択します。

ModelSim、Xcelium、または Vivado シミュレータの場合は、次へ をクリックして HDL コンパイル ページに進みます。VCS の場合は、次へ をクリックして、シミュレーション オプション ページに進みます。

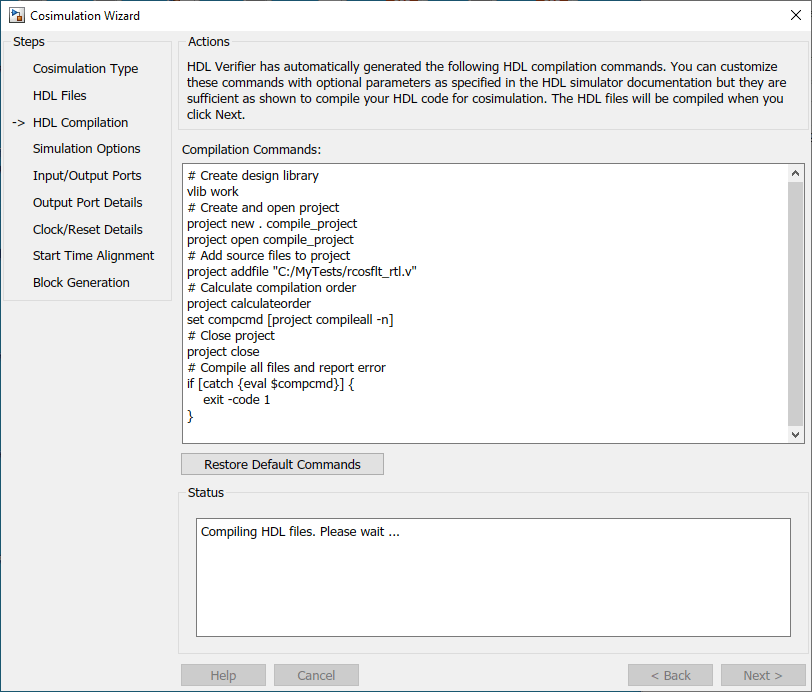

HDL コンパイル ページで、コシミュレーションウィザードは、コンパイル コマンド ウィンドウにデフォルトのコマンドを一覧表示します。このチュートリアルではこれらのコマンドを変更する必要はありません。

独自のコードを使用してコシミュレーション Wizard を実行する場合、このウィンドウでコンパイル コマンドを追加または変更できます。

次の図は、ModelSim のコンパイル コマンドを示しています。

VCS

VCS の場合、コンパイルとシミュレーションが 1 つのステップに結合されます。このステップでは、VHDL または Verilog のコンパイル オプション、詳細化オプション、またはシミュレーション オプションを指定します。

次の図は、VCS のコンパイルおよびシミュレーション コマンドを示しています。

[Next] をクリックします。MATLAB コンソールにコンパイル ログが表示されます。コンパイル中にエラーが発生した場合、そのエラーがステータス領域に表示されます。

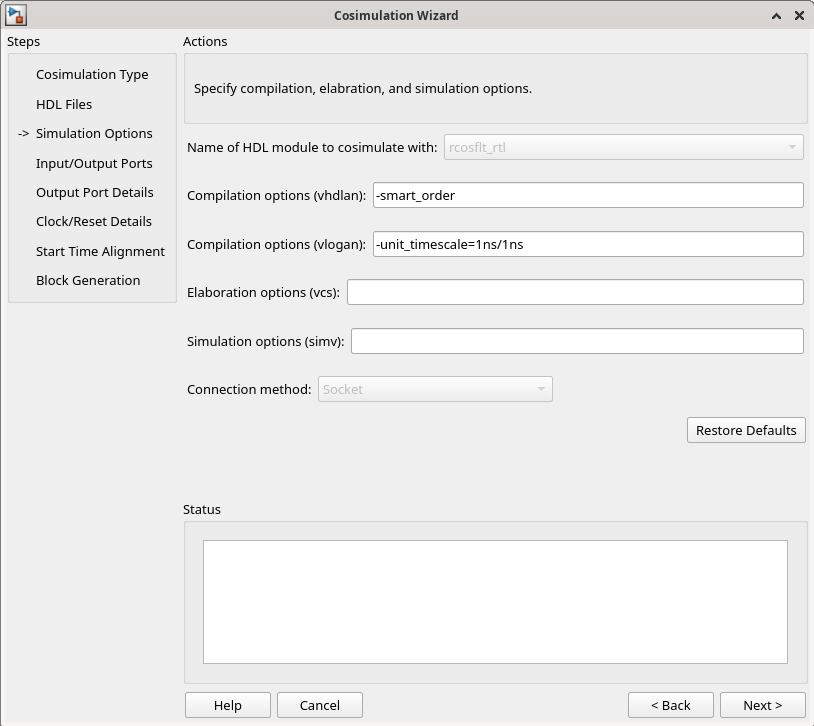

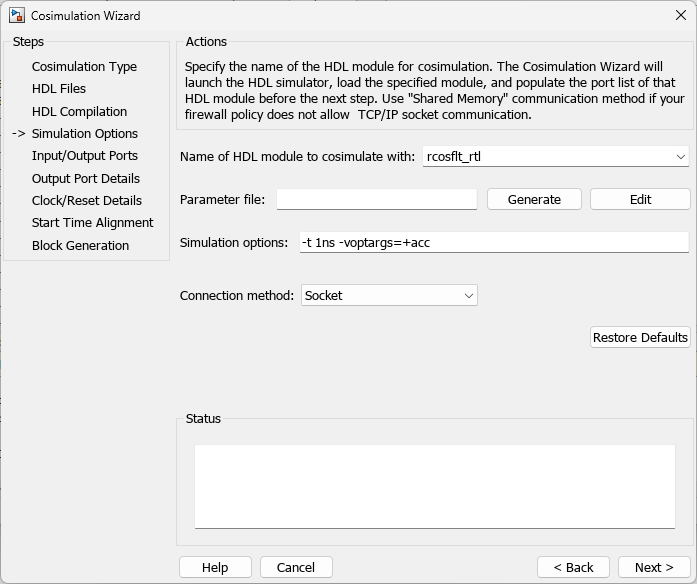

シミュレーション オプション ペインで、次の手順を実行します。

ModelSim または Xcelium

コシミュレーションの HDL モジュール/エンティティの名前を指定します。ドロップダウンリストから

rcosflt_rtlを選択します。このモジュールは、コシミュレーションに使用する Verilog/VHDL モジュールです。ドロップダウン リストにrcosflt_rtlが表示されない場合は、ファイル名を手動で入力できます。接続方法では、ファイアウォール ポリシーで TCP/IP ソケット通信が許可されていない場合は、

Shared Memoryを選択します。

パラメーターファイル セクションを空白のままにすると、ウィザードはデフォルト値を含むパラメーターファイルを作成します。ファイルを編集して、デフォルトのパラメーター値を上書きできます。

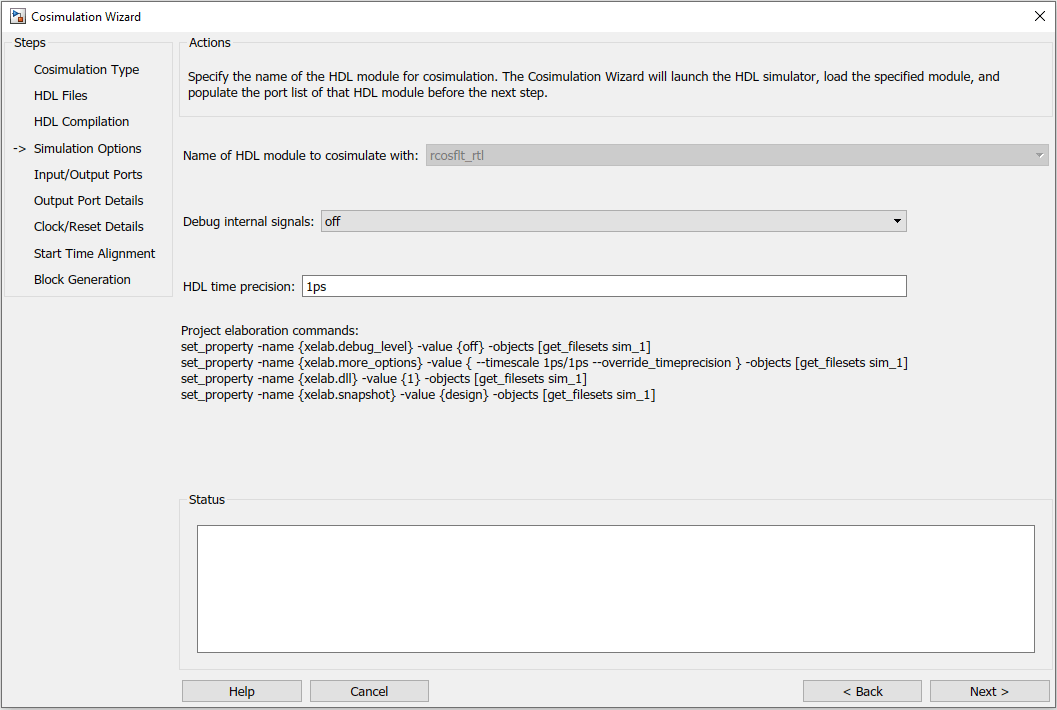

Vivado シミュレータ

デフォルトでは、モジュールの名前は

rcosflt_rtlに設定されています。このモジュールは、コシミュレーションに使用する Verilog/VHDL モジュールです。この例では、デバッグ内部信号を

offに設定し、HDL 時間精度を1psに設定します。

次へ をクリックして、Simulink ポート ペインに進みます。コシミュレーションウィザードは、指定された HDL モジュールとシミュレーション オプションを使用して、バックグラウンド コンソールで HDL シミュレーターを起動します。ウィザードが HDL シミュレータを起動すると、ウィザードは Verilog/VHDL モジュール rcosflt_rtl の入力ポートと出力ポートを設定し、次のステップで表示します。

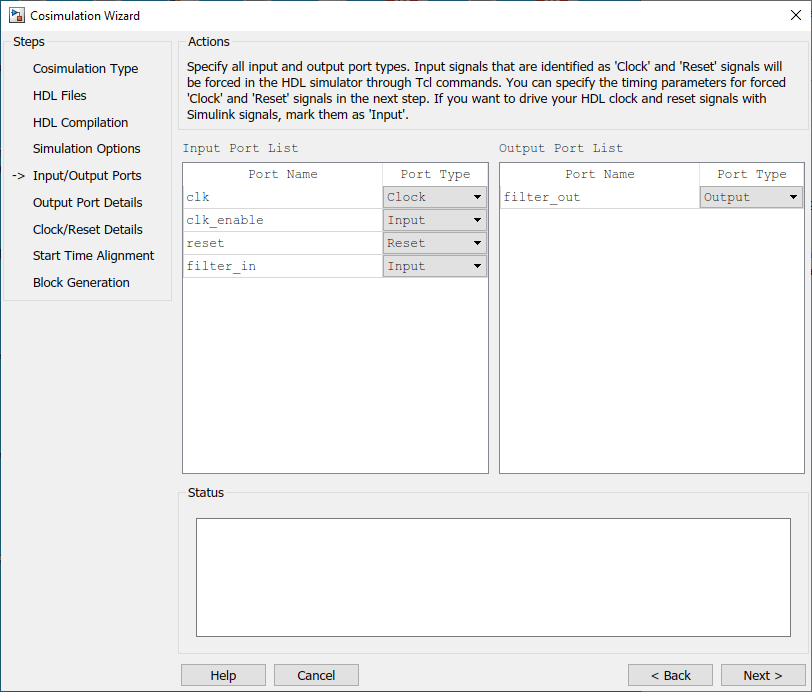

ポート タイプの指定 ステップでは、コシミュレーションウィザードに、それぞれ rcostflt_rtl の入力ポートと出力ポートを含む 2 つのテーブルが表示されます。

コシミュレーションウィザードは、各ポートのポート タイプを識別しようとします。ウィザードがポートを誤って識別した場合は、これらのテーブルを使用してポート タイプを変更できます。

入力ポートは、

Clock、Reset、Input、Unusedから選択できます。HDL Verifier は、コシミュレーション中にInputsとマークされた入力ポートのみを Simulink に接続します。HDL Verifier は、コシミュレーション中に

Outputとマークされた出力ポートを Simulink に接続します。ウィザードと Simulink は、コシミュレーション中にUnusedとマークされた出力ポートを無視します。ClockおよびResetとして識別される信号のパラメーターは、後の手順で変更できます。

デフォルトのポート タイプを受け入れ、次へ をクリックして、出力ポートの詳細ページに進みます。

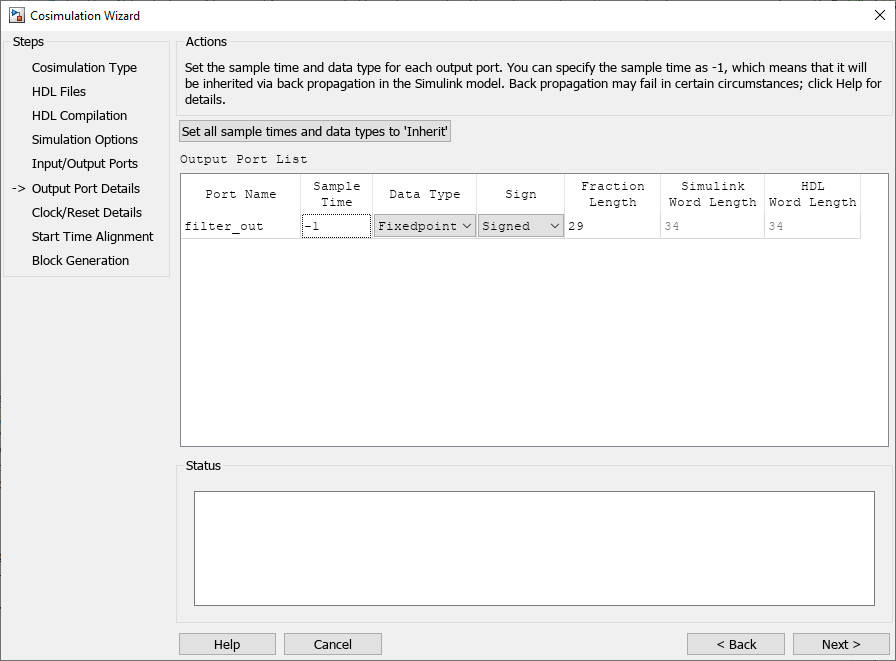

出力ポートの詳細ページで、次の手順を実行します。

バックプロパゲーションで継承するには、

filter_outから-1のサンプル時間を設定します。Verilog コードから、 コシミュレーション Wizard が出力を

sfix34_En29形式で表していることがわかります。次のフィールドを変更します。

データ型を

FixedpointにするSign を

SignedにするFraction Length を

29にする

次へ をクリックして、クロック/リセットの詳細ページに進みます。

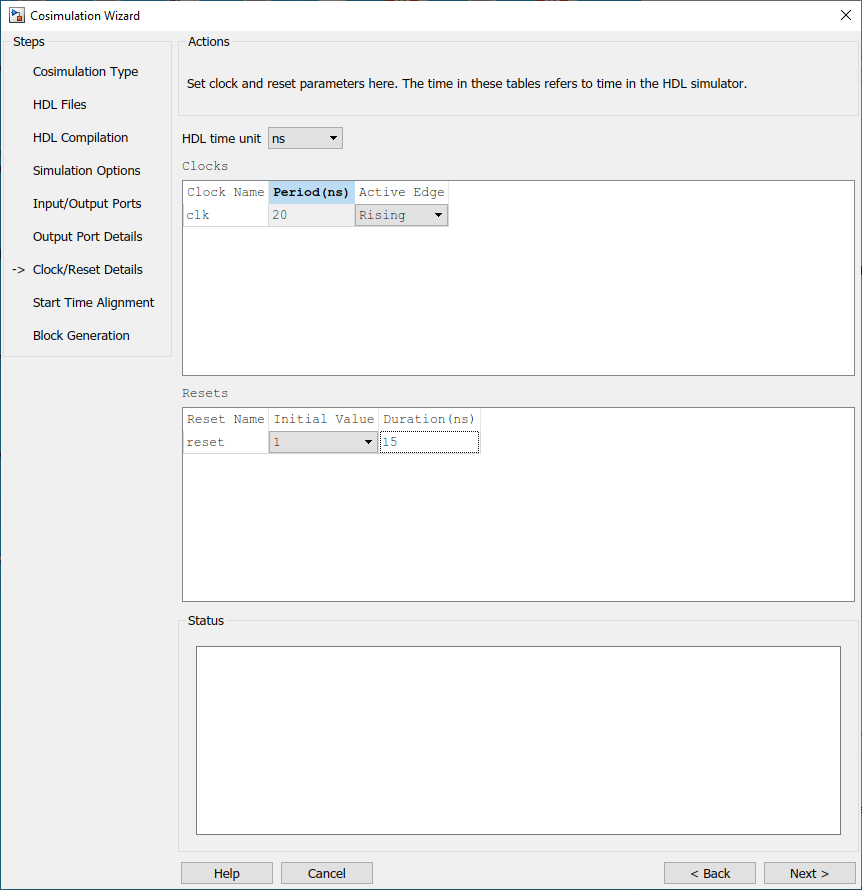

クロック/リセットページで、次の手順を実行します。

ModelSim、Xcelium、または VCS

HDL 時間単位を

nsに設定します。クロック周期を 20 に設定します。

アクティブ エッジを

Risingのままにするか設定します。リセット初期値を 1 のままにするか、1 に設定します。

リセット信号の持続時間を 15 に設定します。

Vivado シミュレータ

HDL 時間単位を

psに設定します。クロック周期を 20 に設定します。

アクティブ エッジを

Risingのままにするか設定します。リセット初期値を 1 のままにするか、1 に設定します。

リセット信号の持続時間を 15 に設定します。

次へ をクリックして、開始時間の調整ページに進みます。

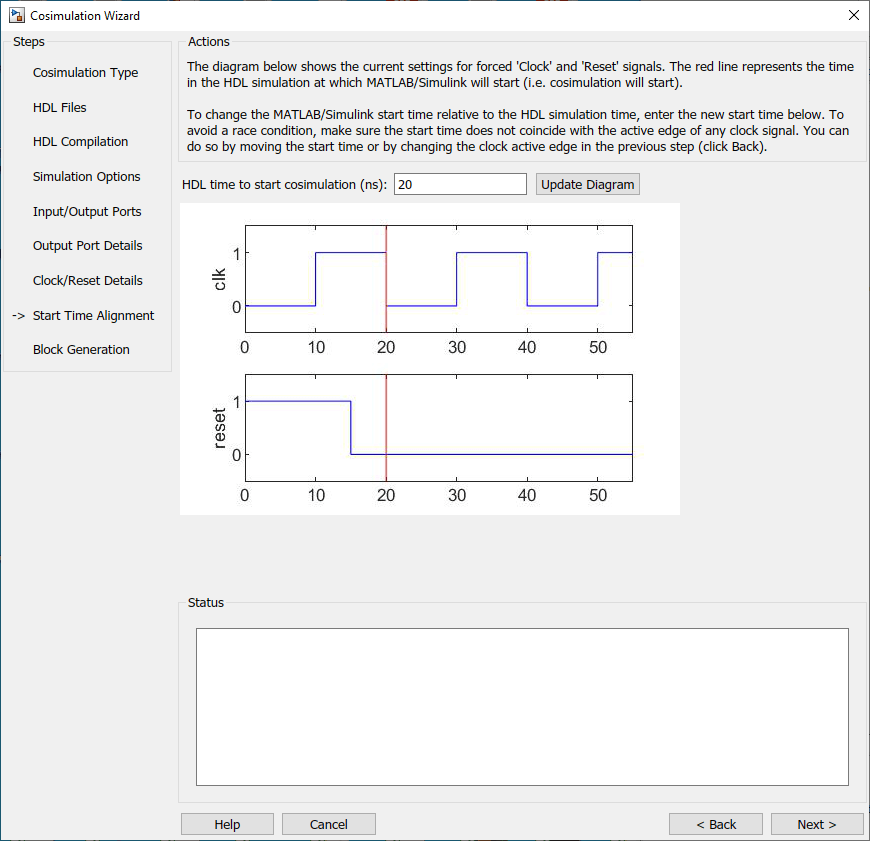

「開始時間の調整」ページには、クロック信号とリセット信号の波形のプロットが表示されます。コシミュレーションウィザードは、コシミュレーションを開始する HDL 時間を赤い線で表示します。開始時間は、Simulink が HDL シミュレータから最初の入力サンプルを取得する時間でもあります。

開始時間の調整ページで、調整を設定します。クロックのアクティブ エッジは立ち上がりエッジです。したがって、ModelSim または Xcelium では 20 ns (Vivado シミュレータでは 20 ps) で、レイズド コサイン フィルタの登録された出力は安定します。競合状態は存在せず、コシミュレーションを開始するためのデフォルトの HDL 時間は、このシミュレーションに必要なものです。開始時間を変更する必要はありません。

次へ をクリックして、ブロック生成に進みます。

HDL Cosimulation ブロックを生成する前に、コシミュレーションウィザードを終了する前にタイムスケールを決定するオプションがあります。あるいは、後でタイムスケールを計算するように HDL Verifier に指示することもできます。生成された HDL Cosimulation ブロックのすべての入出力ポートを接続してシミュレーションを開始すると、検証ソフトウェアによるタイムスケールの計算が行われます。

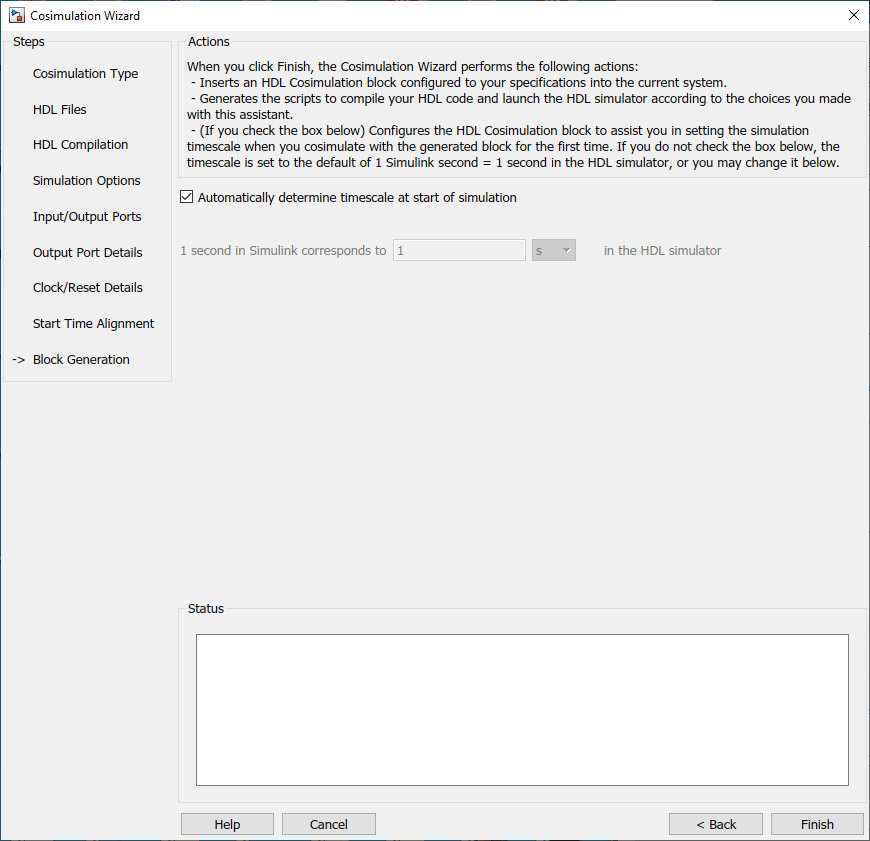

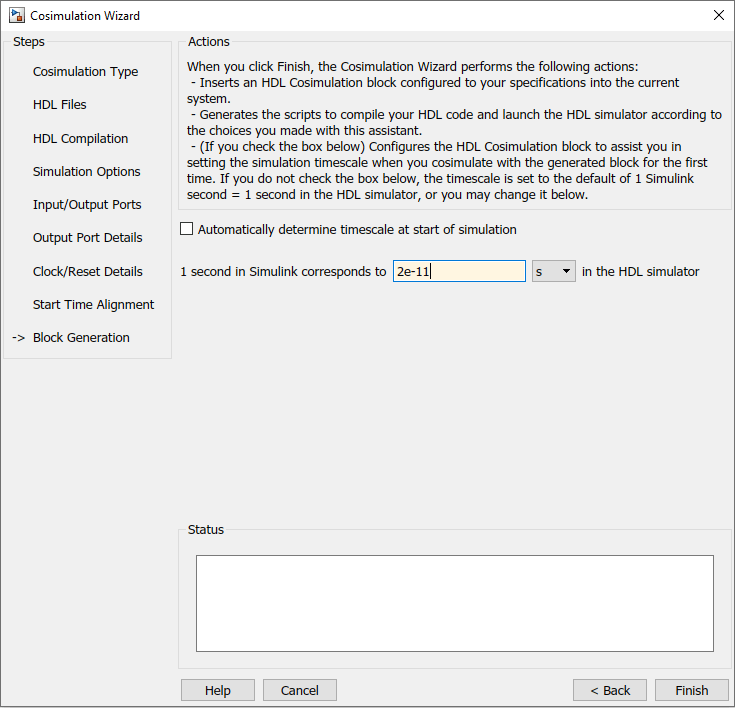

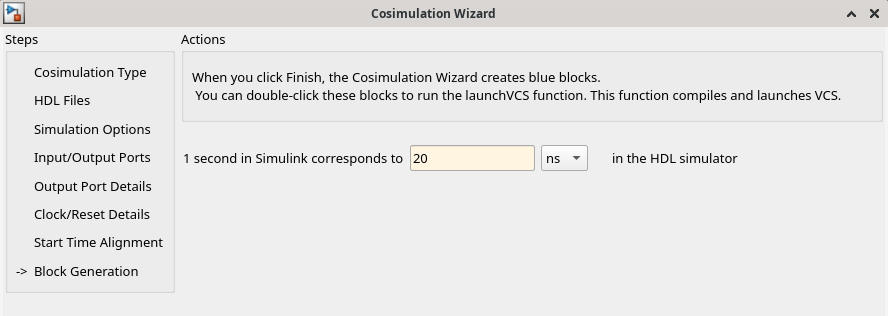

ブロック生成ページで、次の手順を実行します。

ModelSim または Xcelium

シミュレーション開始時にタイムスケールを自動的に決定するを選択したままにします (デフォルト)。後で、シミュレーションを開始する前に、計算されたタイムスケールを表示し、その値を変更する機会があります。

Vivado シミュレータ

シミュレーション開始時にタイムスケールを自動的に決定するのチェックを外し、HDL シミュレーターで Simulink の 1 秒が 2e-11 s に相当 するようにタイムスケールを設定します。

VCS

HDL シミュレータで、Simulink の 1 秒が 20 ns に相当 するように設定して、タイムスケールを設定します。

[完了] をクリックして、コシミュレーションウィザード セッションを完了します。

HDL設計を検証するためのテストベンチを作成する

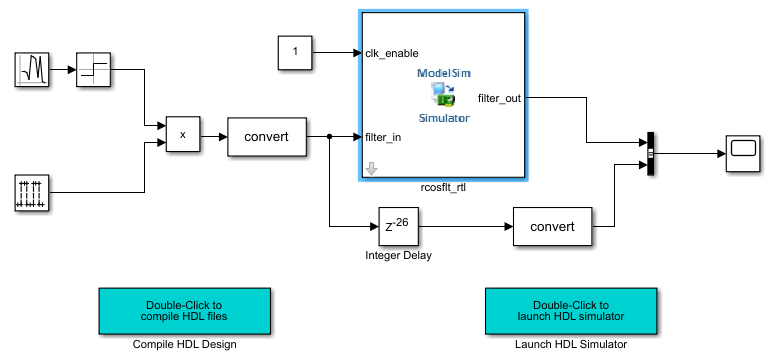

この例では、Simulink テストベンチ モデル rcosflt_tb が提供されています。コシミュレーションウィザードで [完了] をクリックすると、Simulink によってモデル キャンバスの中央に次の項目が挿入されます。

HDL Cosimulationブロック

HDL 設計を再コンパイルするためのブロック (ブロックをダブルクリックすると起動されるスクリプトへのリンクが含まれています)

HDL シミュレーターを起動するブロック (ブロックをダブルクリックすると起動するスクリプトへのリンクが含まれています) (Modelsim および Xceliumのみ)

HDL Cosimulation ブロックを配置して、定数ブロックと変換ブロックが HDL Cosimulation ブロックへの入力として並び、バスが出力として並ぶようにします。ブロックを接続します。モデルは次の図のようになります。

コシミュレーションを実行してHDL設計を検証する

ModelSim または Xcelium

Launch HDL Simulator というラベルの付いたブロックをダブルクリックして、HDL シミュレータを起動します。

HDL シミュレータの準備ができたら、Simulink に戻り、シミュレーションを開始します。

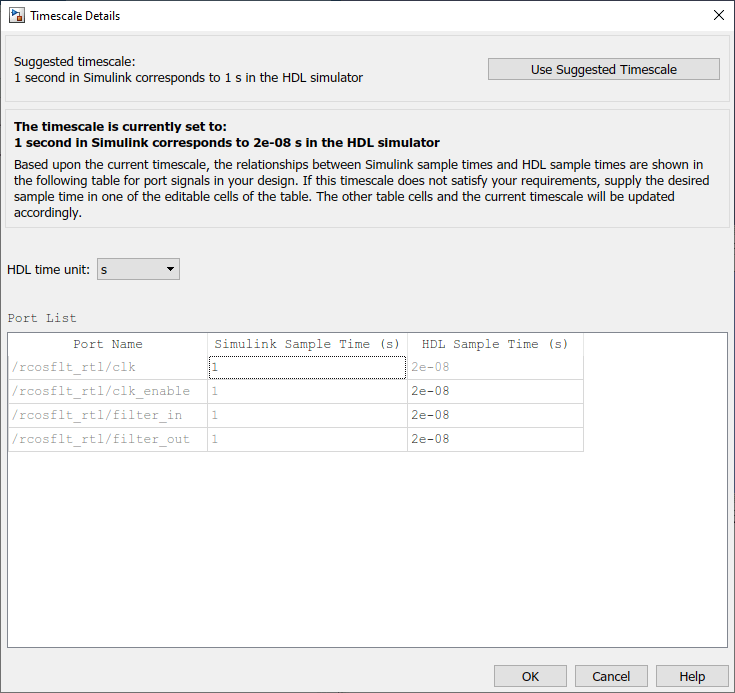

タイムスケールを決定します。コシミュレーションウィザードの最後のページで、シミュレーション開始時にタイムスケールを自動的に決定する オプションを選択したことを思い出してください。これを実行すると、HDL Verifier はシミュレーションを開始する代わりに、タイムスケールの詳細グラフィカル インターフェイスを起動します。HDL シミュレータと Simulink はどちらも

filter_inポートとfilter_outポートを 1 秒ごとにサンプリングします。ただし、HDL シミュレータでのサンプル時間はクロック周期 (20 ns) と同じである必要があります。/rcosflt_rtl/clkの Simulink サンプル時間を 1 (秒) に変更し、Enter を押します。その後、ウィザードはテーブルを更新します。次の図は新しいタイムスケールを示しています。Simulink の 1 秒は、HDL シミュレータの 2e-008 秒に相当します。

OK をクリックして、タイムスケールの詳細ダイアログを閉じます。Simulink シミュレーションを再起動し、テストベンチ モデルのスコープからの結果を確認します。

Vivado シミュレータ

Simulink ツールストリップの シミュレーション タブで、実行 をクリックしてシミュレーションを開始します。Simulink ブロックは共有 DLL を使用して単一のプロセスを実行するため、HDL シミュレーションには個別のプロセスはありません。

VCS

Compile HDL Design というラベルの付いたブロックをダブルクリックして、HDL デザインをコンパイルします。

Launch HDL Simulator というラベルの付いたブロックをダブルクリックして、HDL シミュレータを起動します。

HDL シミュレータの準備ができたら、Tcl コンソールに

runコマンドを入力します。Simulinkに戻り、シミュレーションを開始します。

スコープには、レイズド コサイン フィルターへの入力の遅延バージョンとそのフィルターの出力の両方が表示されます。このフィルタ出力を直接サンプリングすると、シンボル間干渉は発生しません。

関連項目