このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

HDL Cosimulation

Simulink を HDL シミュレータに接続して HDL 設計をコシミュレーションする

ライブラリ:

HDL Verifier /

For Use with AMD Vivado Simulator

HDL Verifier /

For Use with Cadence Xcelium

HDL Verifier /

For Use with Siemens ModelSim/Questa

HDL Verifier /

For Use with Synopsys VCS

説明

HDL Cosimulation ブロックは、HDL シミュレータでシミュレーション中の HDL モデルに入力信号を適用し、そこから出力信号を読み取ることで、ハードウェア コンポーネントをコシミュレーションします。コシミュレーション ウィザード を使用してこのブロックを設定および生成します。

Vivado® シミュレータとコシミュレーションを行う場合は、まず Cosimulation Wizard を使用してこのブロックを生成する必要があります。

VCS®、ModelSim™、または Xcelium™ と共シミュレーションする場合、オプションでウィザードをバイパスしてブロックを直接構成できます。

ブロックでは次のオプションを設定できます。

HDL モジュールの信号 (内部信号を含む) に対応するようにブロックの入力ポートと出力ポートをマッピングします。各出力ポートのサンプル時間を指定する必要があります。オプションで、各出力ポートのデータ型を指定できます。Vivadoコシミュレーションは、内部信号のマッピングをサポートしていません。

シミュレータ間でデータを交換するために使用される通信のタイプと通信設定。

Simulink® と HDL シミュレータのシミュレーション時間の単位間のタイミング関係。

モデルに適用する立ち上がりエッジまたは立ち下がりエッジ クロック。各クロック信号の周期を指定できます。

シミュレーションの前後に実行する Tcl コマンド。

このブロックを使用して、入力ポートまたは出力ポートのみでブロックを構成することにより、ソース デバイスまたはシンク デバイスをモデル化できます。

Simulink コード生成との互換性

このブロックは、HDL Coder™ による HDL コード生成に参加します。コーダーは、手動で記述されたコードまたはレガシー HDL コードへのインターフェイスを生成します。Simulink Coder™ による C コード生成には参加しません。

例

Synopsys VCS 向け Simulink HDLコシミュレーションを使い始める

Simulink および Synopsys® VCS シミュレータを使用して HDL 設計をコシミュレートします。

端子

ブロックに表示されるポートは、HDL シミュレータで実行されている HDL 設計からの信号に対応します。Ports タブには、ポートに対応する HDL 信号が表示されます。

Xcelium、VCS、または ModelSim シミュレータを使用する場合、ブロックパラメーターを変更することで、ポートを追加および削除したり、ポートのデータ型やサンプル時間を構成したりできます。オートフィル ボタンを使用して、HDL シミュレータへのポート情報要求を介してテーブルを入力します。この要求は、 HDL シミュレータで実行されている HDL 設計からのポート名と情報を返します (ブロックを生成するために コシミュレーション ウィザード を使用した場合、この手順は不要です)。HDLシミュレータから信号情報を取得するを参照してください。

メモ

Simulink と HDL シミュレータ間の接続を確立した後にのみ、オートフィル ボタンを使用できます。

HDL Cosimulation ブロックを構成するときに指定するすべての信号は、HDL シミュレータで読み取り/書き込みアクセス権を持っている必要があります。詳細については、HDL シミュレータの製品ドキュメントを参照してください。

入力

ブロック上のポートは HDL 設計上のポートに対応します。Ports タブでポートを追加または削除します。

データ型: int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | Fixed-point

出力

ブロック上のポートは HDL 設計上のポートに対応します。Ports タブでポートを追加または削除します。

データ型: int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | Fixed-point

パラメーター

この パラメーター は読み取り専用です。

このセクションには、コシミュレーション ウィザード を使用してこのブロックを生成した後の情報が表示されます。次の項目が表示されます。

HDLシミュレータ – Vivadoシミュレータ

HDL設計ライブラリ – HDLライブラリファイルの場所

HDL言語 – VHDLまたはVerilog

HDL時間精度 - HDL設計の時間精度

HDL波形ファイル – 波形ファイルの名前とパス

Vivado シミュレータ用のコシミュレーション ブロックを生成する場合、ブロック マスクを使用してポート、クロック、リセット、または時間精度の名前と方向を変更することはできません。これらの項目を変更するには、コシミュレーション ウィザード を開いてブロックを再生成します。

依存関係

このパラメーターは、Vivadoコシミュレーションを使用する場合にのみ表示されます。

端子

モデルに純粋な組み合わせパスが含まれている場合に発生する、コシミュレーションと Simulink 間の 1 つの出力サンプルの遅延差を排除します。HDL Cosimulation ブロックがフィードバック ループ内にあり、代数ループの警告またはエラーを生成する場合は、このチェック ボックスをオフにします。データ パス上にレジスタがあるシーケンシャル回路をシミュレートする場合、直接フィードスルーを指定しても、そのデータ パスのタイミングには影響しません。

依存関係

HDL シミュレータ パス名構文を使用して信号パス名を指定します。たとえば、Xcelium HDL シミュレータの場合は manchester.samp です。信号は、HDL 設計階層のどのレベルにでも配置できます。信号に対応する HDL Cosimulation ブロック端子には、この名前が付けられます。

Simulink でポートとモジュールのパス名を指定する規則については、Simulink テストベンチコシミュレーション用の HDL 信号/ポートとモジュールパスを指定する を参照してください。

HDL シミュレータの 波形 ウィンドウから信号パス名を直接コピーし、Full HDL Name フィールドに貼り付けることができます。Db::Path.Name ビューではなく Path.Name ビューを使用してください。信号パス名を Full HDL Name に貼り付けた後、適用 をクリックして貼り付け操作を完了し、信号リストを更新します。

依存関係

ブロックが コシミュレーション ウィザード から生成された場合、この値は変更しないでください。Vivado HDL Cosimulation ブロックの場合、パラメーターは読み取り専用です。

双方向ポートを追加するには、入力と出力の両方としてポートをリストに 2 回追加します。

入力 — Simulink が駆動する HDL 信号。Simulink は、指定されたサンプル レートで指定された HDL シミュレータ信号に値を格納します。

メモ

ブロック入力ポートを定義するときは、その信号への入力を駆動するソースが 1 つだけ設定されていることを確認してください。たとえば、複数のインスタンスを持つ入力ポートを定義しないでください。複数のソースが単一の信号に入力を駆動する場合、シミュレーション モデルは予期しない結果を生成します。

出力 — Simulink が読み取る HDL 信号。出力信号の場合、明示的なサンプル時間を指定する必要があります。データ型も指定できますが、幅は HDL の信号の幅と一致する必要があります。データ型の指定の詳細については、データ型 および 小数部の長さパラメーターを参照してください。

Simulink 信号には、'Z' 値がないため、トライステート セマンティクスはありません。双方向信号とインターフェースするには、出力ドライバの入力信号と有効信号、および入力ドライバの出力信号の両方に接続します。このアプローチでは、実際のトライステート バッファは HDL に残され、解決関数が他のトライステート バッファとのインターフェイスを処理できます。

依存関係

ブロックが コシミュレーション ウィザード から生成された場合、この値は変更しないでください。Vivado HDL Cosimulation ブロックの場合、パラメーターは読み取り専用です。

この パラメーター は読み取り専用です。

コシミュレーション ウィザード によって設定された HDL ポート信号のタイプを表示します。

依存関係

このパラメーターは、ブロックが Vivadoコシミュレーションで使用するために生成された場合にのみ表示されます。

この パラメーター は読み取り専用です。

コシミュレーション ウィザード によって設定された HDL ポート信号の寸法を表示します。

依存関係

このパラメーターは、ブロックが Vivadoコシミュレーションで使用するために生成された場合にのみ表示されます。

出力ポートに適用される連続したサンプル間の時間間隔。

Simulink は、ここで指定されたサンプル レートで、関連付けられた HDL シミュレータ信号から値を読み取ります。

一般に、Simulink はポートのサンプル期間を次のように処理します。

明示的なサンプル周期を持つ信号に入力ポートを接続すると、順方向伝播に基づいて、Simulink はそのレートをポートに適用します。

明示的なサンプル周期を持たない信号に入力ポートを接続すると、Simulink はモデル内の識別されたすべての入力ポートのサンプル周期の最小公倍数 (LCM) に等しいサンプル周期を割り当てます。

各出力ポートに明示的なサンプル時間を指定する必要があります。

Simulink サンプル時間ヒットに対応する HDL 時間は、タイムスケール 設定によって異なります。シミュレーションのタイムスケールを参照してください。

依存関係

このパラメーターを有効にするには、I/O Mode を 出力 に設定します。

継承 を選択すると、データ型が自動的に決定されます。ブロックは、継承されたワード長が HDL シミュレータから照会されたワード長と一致するかどうかを確認します。一致しない場合は、Simulink はエラー メッセージを生成します。たとえば、Signal Specification ブロックを出力に接続すると、継承 は Signal Specification ブロックで指定されたデータ型を出力ポートに強制します。

Simulink は出力ポートに接続された信号のデータ型を判別できない場合、HDL シミュレータにポートのデータ型を照会します。たとえば、HDL シミュレータがサイズ N ビットの信号に対して VHDL® データ型 STD_LOGIC_VECTOR を返す場合、出力ポートではデータ型 ufixN が強制されます。暗黙の小数部の長さは 0 です。

オプションの 小数部の長さ を使用して、明示的なデータ型を割り当てることもできます。データ型を明示的に割り当てることで、HDL Cosimulation ブロックの出力ポートに固定小数点データ型を強制することができます。たとえば、8 ビットの出力ポートの場合、符号 を Signed に設定し、小数部の長さ を 5 に設定すると、データ型は強制的に sfix8_En5 になります。幅を強制することはできません。幅は常に HDL シミュレータから継承されます。

データ型 および 小数部の長さ プロパティは、次のタイプの HDL 信号にのみ適用されます。

VHDL 信号(

STD_LOGICやSTD_LOGIC_VECTORなど、任意のロジック タイプ)wireまたはregタイプの Verilog® 信号

依存関係

このパラメーターを有効にするには、I/O Mode を 出力 に設定します。

Vivado シミュレータとのコシミュレーション中、このパラメーターは Simulink Data Type として表示されます。

明示的な出力ポート データ型の符号指定。

依存関係

このパラメーターを有効にするには、I/O Mode を 出力 に設定し、データ型 を FixedPoint に設定します。

固定小数点出力信号の小数部のサイズ(ビット単位)。たとえば、8 ビットの出力ポートの場合、符号 を Signed に設定し、小数部の長さ を 5 に設定すると、データ型は強制的に sfix8_En5 になります。幅を強制することはできません。幅は常に HDL シミュレータから継承されます。

依存関係

このパラメーターを有効にするには、I/O Mode を 出力 に設定し、データ型 プロパティを FixedPoint に設定します。

Data Type および Fraction Length プロパティは、次のタイプの HDL 信号にのみ適用されます。

VHDL 信号(

STD_LOGICやSTD_LOGIC_VECTORなど、任意のロジック タイプ)wireまたはregタイプの Verilog 信号

Simulink ポートのサイズ。129 未満の正の整数として指定します。

入力ポートの場合 — この値は inherit (読み取り専用) に設定されます。

HDL ワード長パラメーターが128 ビットより大きい場合、Simulink ポートの寸法は、コンパイル時に駆動信号のデータ型によって決定されます。以下に例を示します。

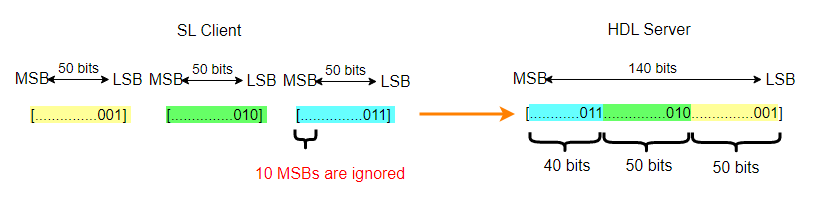

HDL ワード長 = 150 かつ Simulink ワード長 = 50 の場合、HDL Verifier™ はデータ幅が 50 ビットで、

sfix50(3)やufix50(3)などのサイズ 3 の次元を持つ Simulink ポートを許可します。HDL ワード長 = 140 かつ Simulink ワード長 = 50 の場合、HDL Verifier は Simulink の 150 ビットを HDL の 140 ビットにパックします。HDL Verifier は最後のワードの最上位 10 ビット (MSB) を無視します。

出力ポートの場合 — 2 つのケースがあります。

HDL ワード長パラメーターが129 ビット未満の場合、このパラメーターはHDL ポートの幅と一致し、読み取り専用になります。

HDL ワード長パラメーターが128 ビットより大きい場合、HDL Verifier はこのポートを表すポートのベクトルを作成します。以下に例を示します。

HDL ワード長 = 150 かつ Simulink ワード長 = 50 の場合、HDL Verifier はデータ幅が 50 ビットの Simulink ポートを作成します。たとえば、

sfix50(3)またはufix50(3)です。HDL ワード長 = 150 かつ Simulink ワード長 = 60 の場合、HDL Verifier は

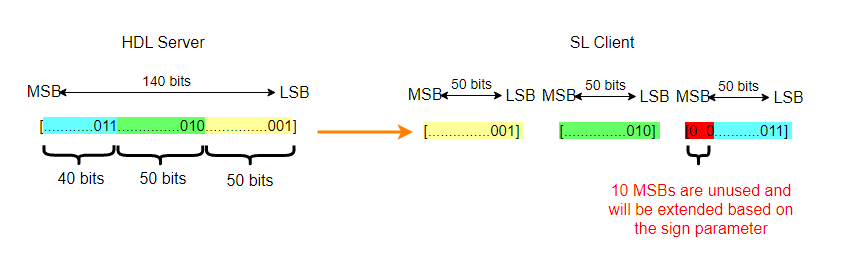

sfix60(3)やufix60(3)などのデータ幅が 60 の Simulink ポートを作成します。HDL ワードには 150 ビットしかなく、Simulink ポートには 180 ビットが必要なので、30 ビットがパディングまたは符号拡張されます。HDL ワード長 = 140 かつ Simulink ワード長 = 50 の場合、HDL 出力の 50 ビットごとに Simulink ワードとして表されます。最後の Simulink ワードの上位 10 ビットは未使用で、Signパラメーターに従って拡張されます。

依存関係

HDL ワード長が 129 より小さい場合、このパラメーターは読み取り専用になります。

この パラメーター は読み取り専用です。

HDL ポートのサイズ (ビット単位)。

Verilog またはSystemVerilog の例:以下のコードでは、入力 In1 の HDL ワード長は 140 ビット、出力 Out1 の HDL ワード長は 160 ビットです。

input [1:0][69:0] In1; output [159:0] Out1;

VHDLの例:以下のコードでは、In1 の HDL ワード長は 120 ビット、In2 の HDL ワード長は 1200 ビットです。

TYPE matrix_of_std_logic_vector120 IS ARRAY (NATURAL RANGE <>, NATURAL RANGE <>) OF std_logic_vector(119 DOWNTO 0); In1: IN matrix_of_std_logic_vector120(0 TO 4, 0 TO 1); In2: IN std_logic_vector(1199 DOWNTO 0);

クロック

メモ

Vivado シミュレータとのコシミュレーション中、このタブの名前は Clocks, Resets, Enables になります。

VCS シミュレータとのコシミュレーション中は、このタブは使用できません。

launchVCS関数のPreSimulationTclプロパティを使用して、クロック信号とリセット信号を定義します。

コシミュレーション モデルに刺激を適用するオプションの立ち上がりエッジ クロックと立ち下がりエッジ クロックを作成します。スクロール リストには、デポジット メソッドを使用してモデル化している HDL 信号に値を駆動する HDL クロックが表示されます。クロック信号はシングルビット信号である必要があります。ベクトル信号はサポートされていません。クロック信号の追加と編集の手順については、HDL コシミュレーション ブロックのクロック ペインでオプションのクロックを作成する を参照してください。

コシミュレーションを開始する前に HDL シミュレーションの実行に必要な時間を指定します。負でない整数を指定し、メニューから時間単位を選択します。

fs– フェムト秒ps– ピコ秒ns– ナノ秒us– マイクロ秒ms– ミリ秒s– 秒

依存関係

このパラメーターを有効にするには、Vivadoコシミュレーション用にこのブロックを生成します。

HDL シミュレータ パス名構文を使用して、各クロックを信号パス名として指定します。たとえば、/manchester/clk または manchester.clk です。

Simulink におけるパスの仕様に関する情報および要件については、Simulink テストベンチコシミュレーション用の HDL 信号/ポートとモジュールパスを指定する を参照してください。

HDL シミュレータの 波形 ウィンドウから信号パス名を直接コピーし、Full HDL Name フィールドに貼り付けることができます。Db::Path.Name ビューではなく Path.Name ビューを使用してください。信号パス名を Full HDL Name に貼り付けた後、適用 をクリックして貼り付け操作を完了し、信号リストを更新します。

依存関係

ブロックが コシミュレーション ウィザード から生成された場合、この値は変更しないでください。Vivado HDL Cosimulation ブロックの場合、パラメーターは読み取り専用です。

次のいずれかのオプションを選択します。

立ち上がり– 立ち上がりエッジクロックを指定します。立ち下がり– 立ち下がりエッジクロックを指定します。

期間と継続時間は Simulink 回です。Simulink 時間を HDL 時間に関連付けるには、[タイムスケール] タブに移動して [タイムスケールを今すぐ特定] をクリックします。

依存関係

このパラメーターは、ModelSim または Xceliumコシミュレーションでのみ表示されます。

Vivadoコシミュレーションの場合は、次のいずれかのオプションを選択します。

Active Rising Edge Clock– 立ち上がりエッジが Simulink が入力を駆動するときからオフセットされる、50% デューティ サイクルの周期信号を作成します。Active Falling Edge Clock– Simulink が入力を駆動するときの下降エッジがオフセットされる、50% デューティ サイクルの周期信号を作成します。Step 0 to 1– 指定された期間 0 を駆動して開始し、その後 1 に遷移するステップ関数を作成します。Step 1 to 0– 指定された期間にわたって 1 を駆動して開始し、その後 0 に遷移するステップ関数を作成します。

期間と継続時間は Simulink 回です。Simulink 時間を HDL 時間に関連付けるには、[タイムスケール] タブに移動して [時間の表示とタイムスケールの提案] をクリックします。

依存関係

このパラメーターは、Vivadoコシミュレーションでのみ表示されます。

明示的なクロック周期を指定するには、2 つの解像度単位 (ティック) 以上のサンプル時間を入力します。

クロック周期が偶数でない場合、Simulink は 50% のデューティ サイクルを作成できません。代わりに、HDL Verifier ソフトウェアは clockperiod/2 で立ち下がりエッジを作成します (最も近い整数に切り捨てられます)。

ModelSim または Xcelium の場合、期間と期間は Simulink 時間として指定され、Vivado の場合、それらは HDL 時間として指定されます。

依存関係

このプロパティは、VCS とのコシミュレーションでは使用できません。

タイムスケール

Simulink と HDL シミュレータ間のタイミング関係を手動または自動で選択します。これらのパラメーターは、1 秒の Simulink 時間と HDL シミュレータ時間の量との間の対応を指定します。この HDL シミュレータ時間の量は、次のいずれかの方法で表現できます。

相対的タイミング関係 (Simulink 秒は HDL シミュレータの精度、つまり「ティック」に相当します)。

絶対タイミング関係(Simulink秒はHDLシミュレータ時間の絶対単位に対応します)

相対タイミング モードと絶対タイミング モードの計算の詳細については、Simulink と HDL シミュレータのタイミング関係の定義 を参照してください。

コシミュレーション中の Simulink と HDL シミュレータの関係、および相対タイミング モードと絶対タイミング モードの動作の詳細については、 シミュレーションのタイムスケール を参照してください。

すべてのポート、クロック、リセット、イネーブルの Simulink 時間と HDL 時間の関係を表示するには、時間の表示とタイムスケールの提案 をクリックします。このアクションは、必要に応じて使用可能なタイムスケールも自動的に決定します。

このオプションを選択すると、HDL Verifier は Simulink シミュレーションを開始するときにタイムスケールを計算します。このオプションが選択されていない場合は、タイムスケールを今すぐ特定 をクリックすると、シミュレーションを開始せずにすぐにタイムスケールが計算されます。Vivadoコシミュレーションの場合、このボタンは 時間の表示とタイムスケールの提案 と表示されます。あるいは、タイムスケールを手動で選択することもできます。自動タイムスケール計算のガイダンスについては、「タイミング関係を自動的に指定する」を参照してください。

依存関係

VCSコシミュレーションの場合、このパラメーターは無効になります。VCS と Simulink 間の接続を確立した後、タイムスケールを表示 をクリックすると、ポート時間マッピング情報を含むダイアログ ボックスが開きます。VCSコシミュレーションの開始の詳細については、MATLABからVCSを開始 を参照してください。

このパラメーターは、Time 値と TimeUnit 値で構成されます。

コシミュレーションの相対タイミングモードを構成するには:

TimeUnit のデフォルト設定である

Tickが選択されていることを確認します。そうでない場合は、右側のリストから選択してください。左側の Time テキスト ボックスにスケール係数を入力します。デフォルトのスケール係数は 1 です。

コシミュレーションの絶対タイミングモードを構成するには:

TimeUnit を絶対時間の単位に設定します:

fs(フェムト秒)、ps(ピコ秒)、ns(ナノ秒)、us(マイクロ秒)、ms(ミリ秒)、またはs(秒)。左側の Time テキスト ボックスにスケール係数を入力します。デフォルトのスケール係数は 1 です。

接続

このタブは、Vivado シミュレータとのコシミュレーション中には表示されません。

Simulink と HDL シミュレータ間の接続のタイプ。

完全なシミュレーション:インターフェースを確認し、HDL シミュレーションを実行します。インターフェイスの確認のみ:HDL シミュレータに接続し、信号名、次元、データ型を確認しますが、HDL シミュレーションは実行しません。Simulink シミュレーション中は、HDL シミュレータとの接続は行われません。接続なし:HDL シミュレータと通信しないでください。HDL シミュレーターを起動する必要はありません。

両方のアプリケーションが同じコンピューター上で実行される場合、アプリケーション間の通信チャネルとして共有メモリまたは TCP ソケットを選択できます。このオプションを選択しない場合、TCP/IP ソケット モードのみが使用可能になり、接続方法 リストは使用できなくなります。

依存関係

VCSコシミュレーションの場合、このパラメーターは無効になります。

ソケット: Simulink と HDL シミュレーターは、指定された TCP/IP ソケットを介して通信します。TCP/IP ソケット モードはより汎用性があります。単一システムおよびネットワーク構成に使用できます。このオプションは最大のスケーラビリティを提供します。TCP/IP ソケット通信の詳細については、TCP/IPソケットポート を参照してください。共有メモリ: Simulink と HDL シミュレータは共有メモリを介して通信します。共有メモリ通信は最適なパフォーマンスを提供し、通信のデフォルト モードです。

依存関係

このパラメーターは、[HDL シミュレーターはこのコンピューター上で実行されている] を選択した場合に表示されます。

VCSコシミュレーションはソケット通信のみをサポートします。

このパラメーターは、Simulink と HDL シミュレータを別のコンピュータで実行する場合に適用されます。

依存関係

VCSコシミュレーションの場合、このパラメーターは読み取り専用です。

共有メモリを使用していない場合は、コンピュータ システムの有効な TCP ソケット ポート番号またはサービスを指定します。TCP ソケット ポートの選択については、TCP/IPソケットポート を参照してください。

このオプションを選択すると、HDL Cosimulation ブロック アイコンに現在の通信パラメーター設定が表示されます。共有メモリを選択した場合、アイコンには SharedMem が表示されます。TCP ソケット通信を選択した場合、アイコンには Socket と表示され、ホスト名とポート番号が hostname:port の形式で表示されます。

この情報は、各ブロックが HDL シミュレータの異なるインスタンスと通信している複数の HDL Cosimulation ブロックを区別するのに役立ちます。

シミュレーション

このタブは、Vivado シミュレータとのコシミュレーション中は表示されません。

Simulink でシミュレーションを開始する前に HDL シミュレーターを実行する時間を指定します。この時間を指定すると、Simulink ブロックの信号と HDL 信号が適切に整列され、追加の遅延なしで直接比較および検証できるようになります。

この設定は、PreRunTime 値と PreRunTimeUnit 値で構成されます。

PreRunTime:任意の有効な時間値。既定値は 0 です。

PreRunTimeUnit:PreRunTime の時間単位を指定します。

Ticksmsusnspsfs

コシミュレーションツールは、Simulink モデルの HDL コンポーネントをシミュレートする前に、HDL シミュレータでこれらのコマンドを実行します。1 行に複数のコマンドを入力する場合は、各コマンドの末尾に標準の Tcl 連結演算子であるセミコロン (;) を追加します。

たとえば、このパラメーターを使用して、シミュレーションが実行中であることを確認するための 1 行の echo コマンドを生成したり、広範なシミュレーションの初期化と起動シーケンスを実行する複雑なスクリプトを生成したりできます。これらのコマンドを使用してシミュレーションの状態を変更することはできません。

有効な Tcl コマンドを任意に指定できます。指定する Tcl コマンドには、HDL シミュレータ プロジェクトをロードしたりシミュレータの状態を変更したりするコマンドを含めることはできません。たとえば、文字ベクトルには、start、stop、restart (ModelSim の場合)、または run、stop、reset (Xcelium の場合) などのコマンドを含めることはできません。

依存関係

VCSコシミュレーションの場合、このパラメーターは無効になります。launchVCS 関数の PreSimulationTcl プロパティを使用して、シミュレーション前の Tcl コマンドを定義します。

コシミュレーションツールは、Simulink モデルの HDL コンポーネントをシミュレートした後、HDL シミュレータでこれらのコマンドを実行します。

有効な Tcl コマンドを任意に指定できます。指定する Tcl コマンドには、HDL シミュレータ プロジェクトをロードしたりシミュレータの状態を変更したりするコマンドを含めることはできません。たとえば、文字列には、start、stop、restart (ModelSim の場合)、または run、stop、reset (Xcelium の場合) などのコマンドを含めることはできません。

メモ

各 ModelSim シミュレーションの後に、シミュレーターはカバレッジ結果を更新するのには時間がかかります。このプロセスと次のコシミュレーションセッション間の潜在的な競合を防ぐには、各連続シミュレーションの間に短い一時停止を追加します。

依存関係

VCSコシミュレーションの場合、このパラメーターは無効になります。launchVCS 関数の PostSimulationTcl プロパティを使用して、シミュレーション後の Tcl コマンドを定義します。

拡張機能

HDL Coder には、HDL の実装および合成されたロジックに影響する追加の構成オプションがあります。Siemens® ModelSim、Cadence® Xcelium、または AMD® Vivado シミュレータで使用されるコシミュレーション ブロックの HDL コードを生成できます。

各 HDL Cosimulation ブロックは、HDL シミュレーターで実行される HDL モデルに入力信号を適用し、そこから出力信号を読み取ることで、ハードウェア コンポーネントをコシミュレーションします。コシミュレーション モデルの生成 (HDL Coder)を参照してください。

HDLコシミュレーションを設定する際のタイミング、レイテンシ、データ型、フレームベースの処理などの問題については、HDLコシミュレーションブロックインターフェースの定義 を参照してください。

HDL Cosimulation ブロックを HDL Coder と組み合わせて使用すると、手動で記述した HDL コードやレガシー HDL コードへのインターフェイスを生成できます。モデルに HDL Cosimulation ブロックが含まれている場合、コーダーは選択されたターゲット言語に応じて VHDL または Verilog インターフェイスを生成します。

ターゲット言語が VHDL の場合、生成されるインターフェースには以下が含まれます。

エンティティの定義。エンティティは、HDL Cosimulation ブロックで構成されたポートに名前とデータ型が対応するポート (入力、出力、クロック) を定義します。クロック イネーブル ポートとリセット ポートも宣言されます。

コンポーネント宣言、HDL Cosimulation ポートに接続された信号に対応する信号を宣言するコンポーネント構成、およびコンポーネントのインスタンス化を含む RTL アーキテクチャ。

モデルに必要なポート割り当てステートメント。

ターゲット言語が Verilog の場合、生成されるインターフェースには以下が含まれます。

HDL Cosimulation ブロックで構成されたポートに名前とデータ型が対応するポート (入力、出力、クロック) を定義するモジュール。このモジュールは、クロック イネーブル ポートとリセット ポート、および HDL Cosimulation ポートに接続された信号に対応する

wire宣言も定義します。モジュールインスタンス。

モデルに必要なポート割り当てステートメント。

コード生成を開始する前に、モデルがコード生成の要件を満たしていることを確認します。コード生成の要件を確認するには、[デバッグ] タブを選択し、[モデルの更新] をクリックします。

このブロックには 1 つの既定の HDL アーキテクチャがあります。

実装パラメーターの説明については、ブラック ボックスまたは HDL コシミュレーション インターフェイスのカスタマイズ (HDL Coder) を参照してください。

バージョン履歴

R2008a で導入Synopsys VCS シミュレータ用の HDL Cosimulation ブロックを作成するには、このブロックを Simulink テストベンチに追加し、HDL DUT に合わせてパラメーターを設定します。端子名とプロパティ、タイムスケール、接続、シミュレーション オプションを指定します。

Vivado シミュレータ用の HDL Cosimulation ブロックを作成するには、コシミュレーション ウィザード を使用して HDL Cosimulation ブロックを生成および構成します。次に、生成されたブロックを Simulink テストベンチで使用します。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)