このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

クロック、リセット、およびイネーブル信号

クロック、リセット、イネーブルの駆動

コシミュレーションでモデルに内部刺激を適用する立ち上がりエッジまたは立ち下がりエッジのクロック、リセット、またはクロック イネーブル信号を作成できます。これらの信号は次の方法で追加できます。

これらの信号を HDL コードに直接実装します。モデルがはるかに大きな HDL 設計の一部である場合、ユーザー (または大規模なモデル設計者) は、これらの信号を Verilog® または VHDL® ファイルに実装することを選択できます。ただし、その実装はこのドキュメントの範囲を超えています。詳細については、HDL リファレンスを参照してください。

Simulink ブロックを使用して信号を追加する

Simulink® ブロックを使用して、Simulink モデルに立ち上がりエッジまたは立ち下がりエッジのクロック、リセット、またはクロック イネーブル信号を追加します。モデルにブロックを追加する手順については、『Simulink ユーザー ガイドおよびリファレンス』を参照してください。

次の例の抜粋では、網掛けされた領域に、複数の HDL Cosimulation ブロック モデルへの入力としてクロック、リセット、およびクロック イネーブル信号が表示されています。これらの信号は、2 つの Simulink データ型変換ブロックと定数ソース ブロックを使用して作成され、「Manchester Receiver Subsystem」というラベルの付いた HDL コシミュレーション ブロックに接続されます。

HDL コシミュレーション ブロックのクロック ペインでオプションのクロックを作成する

メモ

ModelSim® および Xcelium™ ユーザーのみ対象です。

ブロック定義でクロックを指定すると、Simulink は指定された HDL 信号を駆動する立ち上がりエッジまたは立ち下がりエッジのクロックを作成します。

Simulink は、50% のデューティ サイクルと、立ち下がりエッジの場合に反転される定義済みの位相を持つクロックを作成しようとします。該当する場合、Simulink は、奇数の Simulink サンプル時間に対応するためにデューティ サイクルを低下させます。最悪の場合、サンプル時間 T=3 に対してデューティ サイクルは 66% になります。

Timescales ペインを相対タイミング モードまたは絶対タイミング モードのどちらに設定した場合でも、クロック周期には次の制限が適用されます。

明示的なクロック周期を指定する場合は、2 解像度単位 (ティック) 以上のサンプル時間を入力する必要があります。

クロック周期 (明示的に指定されているかデフォルトになっているかに関係なく) が偶数でない場合、Simulink は 50% のデューティ サイクルを作成できないため、HDL Verifier™ ソフトウェアは

(最も近い整数に切り捨て) で立ち下がりエッジを作成します。

相対タイミング モードと絶対タイミング モードの計算の詳細については、Simulink と HDL シミュレータのタイミング関係の定義 を参照してください。

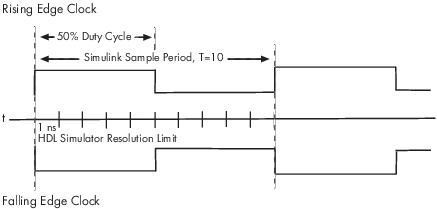

次の図は、Simulink サンプル時間が T=10、HDL シミュレータの解像度制限が 1 ns の立ち上がりエッジ クロックと立ち下がりエッジ クロックを含むタイミング図を示しています。この図は、これらのタイミング パラメータが与えられた場合、クロックのデューティ サイクルが 50% であることも示しています。

クロックを作成するには、次の手順を実行します。

HDL シミュレーターで、ブロックで定義する予定のクロック信号パス名を決定します。これを行うには、「HDL 信号をブロック ポートにマップする」の手順 1 でポートの信号パス名を決定するために説明したのと同じ方法を使用できます。

[ブロック パラメータ] ダイアログ ボックスの [Clocks] タブを選択します。

新しいクロック信号を追加するには、New をクリックします。

デフォルトのクロック信号名 (

/top/clk) をダブルクリックして、Full HDL Name 列の下のテーブルでクロック信号パス名を直接編集します。次に、HDL シミュレータ パス名構文を使用して新しいクロックを指定します。Simulink テストベンチコシミュレーション用の HDL 信号/ポートとモジュールパスを指定するを参照してください。HDL シミュレーターは、Clocks ペインでベクトル信号をサポートしていません。信号は 1 と 0 の値を持つ論理型である必要があります。

クロックが立ち上がりエッジ信号を生成するか、立ち下がりエッジ信号を生成するかを指定するには、Active Clock Edge リストから

RisingまたはFallingを選択します。Period フィールドはクロック周期を指定します。デフォルト (

2) を受け入れるか、Period フィールドをダブルクリックして目的のクロック周期を明示的に入力して上書きします。Period フィールドを偶数として指定します。最小値は

2です。クロック信号の編集が完了したら、Apply をクリックして、変更内容を Simulink に登録します。

次のダイアログ ボックスは、HDL Cosimulation ブロックの立ち上がりエッジ クロック clk をデフォルトの周期 2 で定義します (Xcelium で使用する場合の例を示します)。

力コマンドを追加して信号を駆動する

クロック、リセット、およびイネーブル信号は、次の 2 つの方法のいずれかで駆動できます。

Simulation ペインに強制コマンドを追加する (ModelSim および Xcelium ユーザーのみ)

HDL Verifier HDLシミュレータ起動コマンド(

vsimまたはnclaunch)のいずれかとforceコマンドを使用して信号を駆動することにより

例: HDLコシミュレーションブロックシミュレーションペインに入力されたforceコマンド

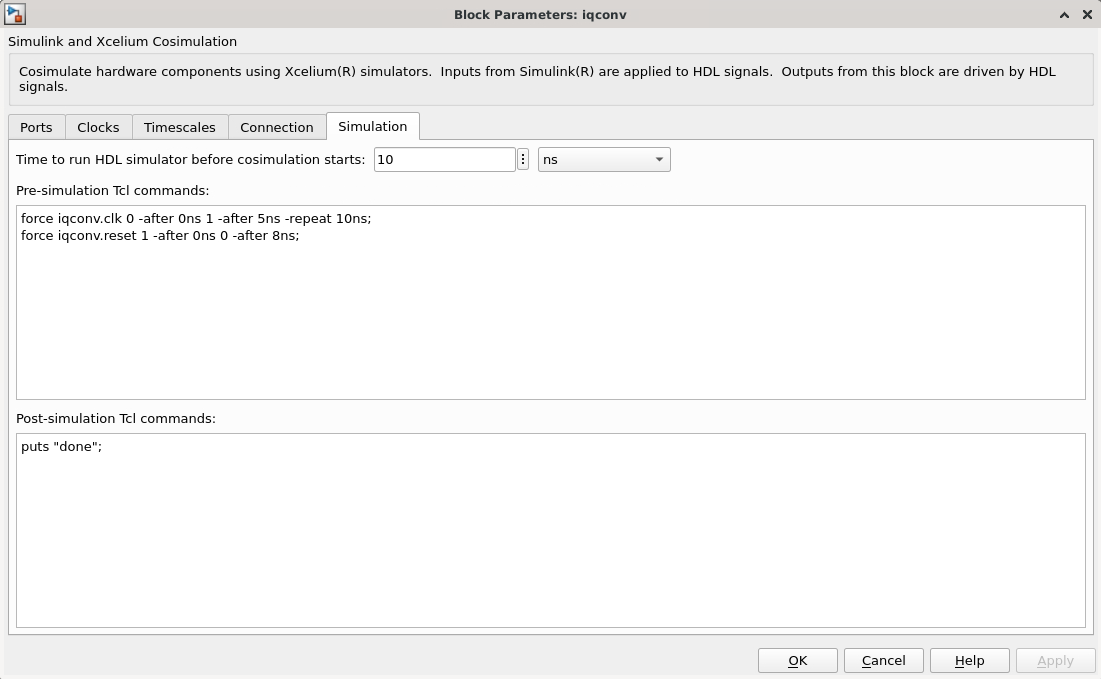

以下は、Xcelium で使用するために HDL コシミュレーション ブロックの Simulation ペインに強制コマンドを入力する例です。

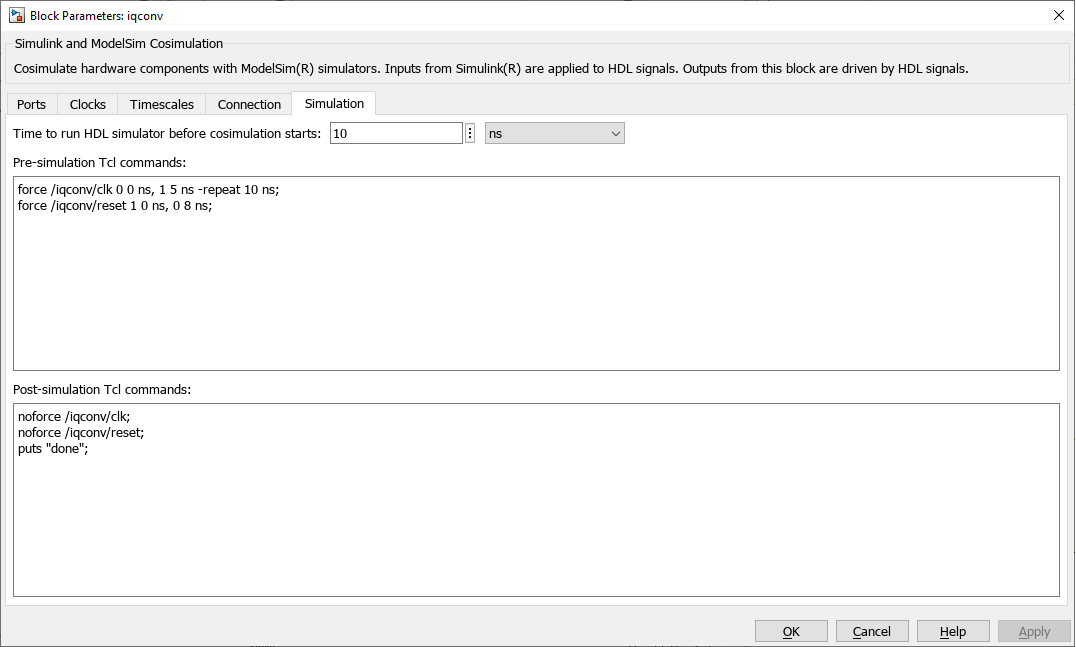

以下は、ModelSim で使用するために HDL コシミュレーション ブロックの Simulation ペインに強制コマンドを入力する例です。

例: HDL Verifier HDL シミュレータ起動コマンドで使用される force コマンド

vsim 関数と強制コマンド (ModelSim ユーザー):

vsim('tclstart', {'force /iqconv/clk 0 0, 1 5 ns -repeat 10 ns',

'force /iqconv/reset 1 0 ns, 0 8 ns'});nclaunch 関数と強制コマンド (Xcelium ユーザー):

nclaunch('tclstart',['-input "{force iqconv.clk 0 -after 5ns -repeat 10ns}"',

'-input "{force iqconv.reset 1 -after 0ns 0 -after 8ns}"',]);