このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

Simulink コシミュレーション テスト ベンチを作成する

これらの手順では、Simulink® ソフトウェアをテストベンチとして使用して HDL 設計をコシミュレーションする方法について説明します。

Simulink ブロック ライブラリから Simulink ブロックを追加して、Simulink テスト ベンチ モデルを作成します。ハードウェア モデル コンポーネントをコシミュレーション ブロックとして置き換えたり追加したりする前に、モデルを徹底的に実行してテストしてください。

HDL モジュールをコード化します。HDL シミュレーターでモジュールをコンパイル、詳細化、シミュレートします。HDLコンポーネントのコーディングを参照してください。

MATLAB® および Simulink で使用するために HDL シミュレータを起動し、HDL Verifier™ ライブラリをロードします。Simulink でコシミュレーション用の HDL シミュレータを起動しますを参照してください。

HDL Cosimulation ブロックを Simulink テスト ベンチ モデルに追加します。HDLコシミュレーションブロックを挿入を参照してください。

HDL Cosimulation ブロック インターフェイスを定義します。HDLコシミュレーションブロックインターフェースを構成するを参照してください。

(オプション) シミュレーション セッション中に変数値の変更を記録するには、To VCD File ブロックを追加します。値変更ダンプ (VCD) ファイルを追加するを参照してください。

まず HDL シミュレーターでシミュレーションを開始し、次に Simulink モデルを実行します。Simulinkコシミュレーションセッションを実行するを参照してください。

Vivado® ユーザー: 上記の手順 3 ~ 7 を次の手順に置き換えます。

Cosimulation Wizard を使用して、Vivado コシミュレーション用の HDL Cosimulation ブロックを生成します。詳細については、HDL コシミュレーション ブロックの HDL コードをインポートするを参照してください。

生成された HDL Cosimulation ブロックを Simulink テストベンチ モデルに追加します。

Simulink からシミュレーションを開始します。HDL Cosimulation ブロックは共有ライブラリをロードし、Vivado との協調シミュレーションを実行します。

HDLコンポーネントのコーディング

HDL Verifier インターフェイスは、HDL シミュレータと Simulink 間のすべてのデータをポート データとして渡します。HDL Verifier ソフトウェアは、既存の HDL モジュールと連携して動作します。ただし、Simulink 検証を対象とする HDL モジュールをコーディングする場合は、2 つの環境間で共有されるデータのタイプと方向モードを考慮する必要があります。

テストベンチで使用するために HDL コンポーネントでポート方向モードを指定する

モジュール ステートメントでは、各ポートの方向モード (入力、出力、または双方向) を指定する必要があります。次の表では、これら 3 つのモードを定義します。

| VHDL® モードを使用します... | Verilog® モードを使用します... | ポートの場合... |

|---|---|---|

IN | input | MATLAB関数またはSimulinkテストベンチで駆動できる信号を表す |

OUT | output | MATLAB関数またはSimulinkテストベンチに渡される信号値を表す |

INOUT | inout | MATLAB関数またはSimulinkテストベンチによって駆動されるか、または値を渡せる双方向信号を表します。 |

テストベンチで使用するために HDL コンポーネントでポート データ型を指定する

このセクションでは、HDL モジュールのポートに MATLAB と互換性のあるデータ型を指定する方法について説明します。HDL Verifier インターフェイスが MATLAB 環境のデータ型を変換する方法の詳細については、サポートされているデータ型 を参照してください。

メモ

サポートされていないタイプを使用すると、HDL Verifier ソフトウェアは警告を発し、実行時にポートを無視します。たとえば、実行時に 5 つのポートを持つインターフェイスを定義し、そのうちの 1 つが VHDL アクセス ポートである場合、インターフェイスは警告を表示し、コードでは 4 つのポートのみを認識します。

テストベンチで使用するための HDL 設計のコンパイルと詳細化

HDL 設計のコンパイルと詳細化の手順については、HDL シミュレータのドキュメントを参照してください。

HDLコシミュレーションブロックインターフェースを構成する

このワークフローは、HDL Cosimulation ブロックを構成および生成するために Cosimulation Wizard を使用する代わりに使用できます。Vivado 協調シミュレーションの場合は、Cosimulation Wizard を使用する必要があります。HDL コシミュレーション ブロックの HDL コードをインポートするを参照してください。

HDLコシミュレーションブロックを挿入

モデルのコンポーネントの 1 つを VHDL または Verilog でコーディングし、HDL シミュレーター環境でシミュレートした後、次の手順を実行して、HDL 表現を HDL Cosimulation ブロックとして Simulink モデルに統合します。

Simulink モデルがまだ開いていない場合は開きます。

HDL Cosimulation ブロックが置き換えるモデル コンポーネントを削除します。

Simulink ライブラリ ブラウザで、HDL Verifier ブロック ライブラリをクリックします。次に、サポートされている HDL シミュレータのブロック ライブラリを選択できます。以下に示すように、Mentor Graphics® ModelSim® HDL Cosimulation ブロックまたは Cadence® Xcelium™ HDL Cosimulation ブロックのいずれかを選択します。

ライブラリ ブラウザから HDL Cosimulation ブロックをモデルにコピーします。

ブロックポートを接続する

HDL Cosimulation ブロック ポートを Simulink モデルの該当するブロック ポートに接続します。

シンク デバイスをモデル化するには、入力のみでブロックを構成します。

ソース デバイスをモデル化するには、出力のみを使用してブロックを構成します。

HDLコシミュレーションブロックパラメータを開く

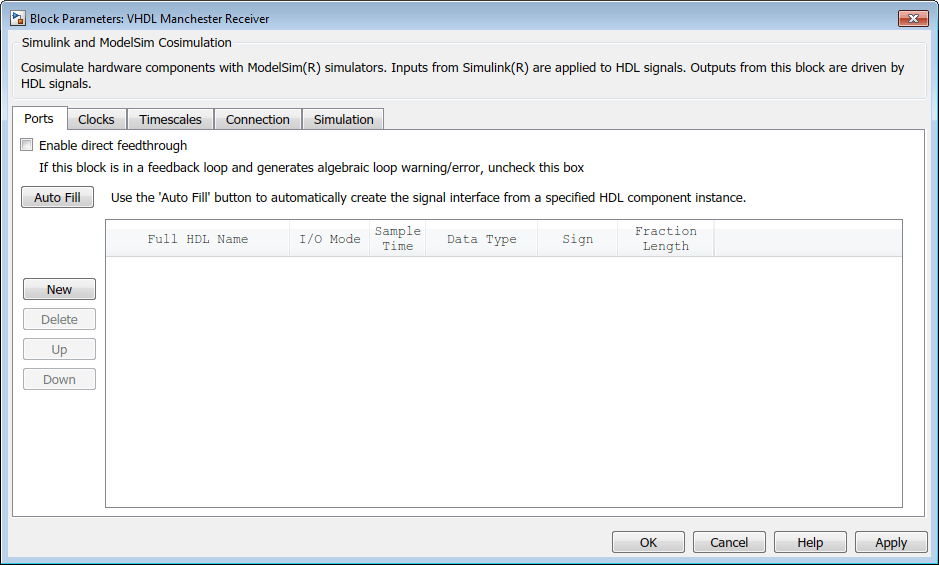

HDL Cosimulation ブロックのブロック パラメータ ダイアログ ボックスを開くには、ブロック アイコンをダブルクリックします。Simulink では、次のブロック パラメータ ダイアログ ボックスが表示されます (例として、ModelSim で使用する HDL Cosimulation ブロックのダイアログ ボックスを以下に示します)。

HDL信号をブロックポートにマッピングする

HDL Verifier HDL Cosimulation ブロックを構成する最初の手順は、HDL デザインの信号と信号インスタンスを HDL Cosimulation ブロックのポート定義にマッピングすることです。入力ポートと出力ポートを識別するだけでなく、各出力ポートのサンプル時間も指定できます。各出力ポートに固定小数点データ型を指定することもできます。

マップする信号は、HDL 設計階層の任意のレベルに配置できます。

信号をマッピングするには、次のいずれかのアクションを実行できます。

ブロック パラメータ ダイアログ ボックスの Ports ペインに信号情報を手動で入力します。このアプローチは、HDL モデルから少数の信号を Simulink に接続する場合により効率的です。

Auto Fill ボタンを使用すると、HDL Cosimulation ブロックが HDL シミュレータにクエリを送信して信号情報を取得します。このアプローチにより、Simulink モデルに接続する信号が多数ある HDL モデルをコシミュレーションする場合に、大幅な労力を節約できます。ただし、場合によっては、クエリによって返された信号データを編集する必要があります。

メモ

コシミュレーションで使用される信号に読み取り/書き込みアクセス権があることを確認します。パフォーマンスを向上させるには、コシミュレーションで使用される信号のみにアクセスできるようにする必要があります。このルールは、Ports、Clocks、および Simulation ペイン上のすべての信号、および他の方法で追加されたすべての信号に適用されます。

Simulink テストベンチコシミュレーション用の HDL 信号/ポートとモジュールパスを指定する. これらのルールは、Simulink のシグナル/ポートおよびモジュール パスの仕様に関するものです。その他の仕様も機能する可能性がありますが、今回のリリースまたは将来のリリースでは明示的または暗黙的にサポートされていません。

HDL 設計には通常階層があり、それがこの構文の理由です。この仕様はファイル名の階層を表すものではありません。

HDLシミュレータから信号情報を取得する. Auto Fill ボタンを使用すると、HDL シミュレータ クエリを開始し、HDL シミュレータでシミュレーション中の HDL モデル内のコンポーネントまたはモジュールへのパスを指定できます。通常、クエリが完了した後、ポート情報の変更が必要になります。Auto Fill が動作するには、HDL モジュールがロードされた状態で HDL シミュレーターを実行する必要があります。

次の例では、必要な手順について説明します。

メモ

この例は、マンチェスター レシーバー モデルの修正されたコピーに基づいており、最初に Ports および Clocks ペインからすべての信号が削除されています。

HDL Cosimulation ブロックのブロック パラメータ ダイアログ ボックスを開きます。Ports タブをクリックします。Ports ペインが開きます (例として、ModelSim で使用する HDL Cosimulation ブロックの Ports ペインを下の図に示します)。

ヒント

Auto Fill を実行する前にすべてのポートを削除して、未使用の信号がポート リストに残らないようにします。

Auto Fill ボタンをクリックします。Auto Fill ダイアログ ボックスが開きます。

このモーダル ダイアログ ボックスは、HDL モデル内のコンポーネントまたはモジュールへのインスタンス パスを要求します。ここでは、編集フィールドに明示的な HDL パスを入力します。入力したパスはファイル パスではなく、ソース ファイルとは関係ありません。

この例では、自動入力機能によって、

manchesterと呼ばれる VHDL コンポーネントのポート データを取得します。HDL パスは/top/manchesterとして指定されます。パスの仕様は HDL シミュレータによって異なります。Simulink コンポーネントコシミュレーション用の HDL 信号/ポートとモジュールパスを指定する を参照してください。

Fill をクリックするとダイアログ ボックスが閉じられ、クエリが送信されます。

HDL シミュレータがポート データを返すと、次の図に示すように、自動入力機能によってそのデータが Ports ペインに入力されます (Cadence Xcelium での使用例を示しています)。

ポートの追加をコミットするには、Apply をクリックします。

ポート ペインから未使用の信号を削除し、クロック信号を追加します。

上の図は、クエリによってクロック、クロック イネーブル、リセット ポート (それぞれ

clk、enable、resetというラベルが付けられている) がポート リストに入力されたことを示しています。Ports ペインから

clk、enable、reset信号を削除し、Clocks ペインにclk信号を追加します。これらのアクションの結果、次の図に示す信号が生成されます。

Auto Fill は出力ポートのデフォルト値を返します:

Sample time:

1データ型:

Inherit小数部の長さ:

Inherit

モデルの必要に応じてこれらの値を変更する必要がある場合があります。この例では、すべての出力に対して Sample time を

10に設定する必要があります。「信号データ型の指定」を参照してください。ブロック パラメータ ダイアログ ボックスを閉じる前に、Apply をクリックして、行った編集内容を確定します。

Auto Fill が、対象コンポーネントの すべての 入力と出力に関する情報を返したことを確認します。多くの場合、これには HDL シミュレータでは機能するが Simulink モデルでは接続できない信号が含まれます。不要なエントリは、Ports ペインのリストから削除できます。Simulink からの信号を駆動することは 可能 です。Simulink ブロックを配置して値を定義するだけです。

Auto Fill は内部信号の情報を返さないことに注意してください。Simulink モデルがこのような信号にアクセスする必要がある場合は、それらを Ports ペインに手動で入力する必要があります。たとえば、マンチェスター レシーバー モデルの場合、手順 8 に示すように、top/manchester/sync_i、top/manchester/isum_i、および top/manchester/qsum_i の出力ポート エントリを追加する必要があります。

Xcelium および ModelSim ユーザー:clk、reset、clk_enable は、クロック ペインとシミュレーション ペインに表示される場合もありますが、必ずしも表示される必要はありません。これらの信号は、Simulink から明示的に駆動することを選択した場合はポートになります。

メモ

Auto Fill を使用して VHDL 信号をインポートすると、HDL シミュレーターは信号名をすべて大文字で返します。

信号情報を手動で入力する. Ports ペインに信号情報を直接入力するには、次の手順を実行します。

HDL シミュレーターで、ブロックで定義する予定の HDL 信号の信号パス名を決定します。たとえば、ModelSim シミュレータでは、次の波形ウィンドウは、すべての信号が最上位モジュール

manchesterに従属していることを示しています。

Simulink で、HDL Cosimulation ブロックのブロック パラメータ ダイアログ ボックスがまだ開いていない場合は開きます。

Ports ペイン タブを選択します。Simulink は次のダイアログ ボックスを表示します (Xcelium で使用する場合の例を示します)。

このペインでは、Simulink ブロックに含めるデザインの HDL 信号を定義し、出力ポートのサンプル時間とデータ型を設定します。Ports ペインで指定する必要があるパラメータは、ブロックがモデル化しているデバイスのタイプに応じて次のように異なります。

入力と出力の両方を持つデバイスの場合: ブロック入力ポート、ブロック出力ポート、出力サンプル時間、および出力データ型を指定します。

出力ポートの場合は、デフォルトを受け入れるか、明示的なサンプル時間を入力します。データ型は明示的に指定することも、

Inherit(デフォルト) に設定することもできます。デフォルトでは、出力ポートのデータ型は、ポートに接続された信号から継承されるか、HDL モデルから派生されます。シンク デバイスの場合: ブロック出力ポートを指定します。

ソース デバイスの場合: ブロック入力ポートを指定します。

既存のデフォルト信号をダブルクリックして、Full HDL name 列に信号パス名を入力します。

HDL シミュレータ パス名構文を使用します (Simulink テストベンチコシミュレーション用の HDL 信号/ポートとモジュールパスを指定する で説明)。

信号を追加する場合は、New をクリックしてデフォルト値を編集します。I/O Mode 列から

InputまたはOutputのいずれかを選択します。必要に応じて、残りの手順で説明するように、信号の Sample Time、Data Type、および Fraction Length パラメータを明示的に設定します。

クロック信号の編集が完了したら、Apply をクリックして、変更内容を Simulink に登録します。

次のダイアログ ボックスには、HDL Cosimulation ブロックのポート定義が表示されます。信号パス名は、HDL シミュレータの wave ウィンドウに表示されるパス名と一致します (Xcelium の例を示します)。

メモ

入力ポートを定義するときは、そのポートへの入力を強制するソースが 1 つだけ設定されていることを確認してください。複数のソースが信号を駆動する場合、Simulink モデルは予期しない結果を生成する可能性があります。

出力ポートのサンプル時間を指定する必要があります。Simulink は、指定した値と Timescales ペインの現在の設定を使用して、実際のシミュレーション サンプル時間を計算します。

HDL Verifier コシミュレーション環境でのサンプル時間の詳細については、シミュレーションのタイムスケール を参照してください。

必要に応じて各出力ポートの固定小数点データ型を明示的に構成することも、デフォルト (

Inherited) を使用することもできます。デフォルトでは、Simulink は出力ポートのデータ型を次のように決定します。Simulink は、出力ポートに接続された信号のデータ型を判別できる場合、そのデータ型を出力ポートに適用します。たとえば、接続された信号仕様ブロックのデータ型は、バックプロパゲーションによってわかります。それ以外の場合、Simulink は HDL シミュレータにクエリを実行して、HDL モジュールからの信号のデータ型を決定します。

信号に明示的な固定小数点データ型を割り当てるには、次の手順を実行します。

Data Type 列から

SignedまたはUnsignedのいずれかを選択します。信号に小数部分がある場合は、Fraction Length を入力します。

たとえば、モデルに

Signedデータ型の 8 ビット信号があり、Fraction Length が5の場合、HDL Cosimulation ブロックはそれにデータ型sfix8_En5を割り当てます。モデルに小数部のないUnsigned16 ビット信号 (0の Fraction Length) がある場合、HDL Cosimulation ブロックはそれにデータ型ufix16を割り当てます。

ダイアログ ボックスを閉じる前に、Apply をクリックして編集内容を登録します。

入力ポートの値で出力ポートを直接制御する. ダイレクト フィードスルーを有効にすると、入力ポートの値の変更がゼロ時間で出力ポートに伝播されるため、純粋な組み合わせロジックを使用した HDL 設計で出力サンプル時に発生する可能性のある遅延が排除されます。次の図に示すように、Ports ペインで直接フィードスルーを有効にするオプションを指定します。

信号データタイプの指定

Data Type および Fraction Length パラメータは出力信号にのみ適用されます。HDL Cosimulation ブロックのポート ペインの説明にある Data Type と Fraction Length を参照してください。

Simulink と HDL シミュレータのタイミング関係を構成する

ブロック パラメータ ダイアログ ボックスの Timescales ペインを使用して、Simulink と HDL シミュレータ間のタイミング関係を構成します。Timescales パラメータを設定する前に、シミュレーションのタイムスケール を読んで、サポートされているタイミング モードと、タイミング モードの選択を決定する問題を理解してください。

HDL Cosimulation ブロック参照で説明されているように、Timescales ペインで Simulink と HDL シミュレータ間の相対または絶対タイミング関係を指定できます。

Simulink と HDL シミュレータのタイミング関係. シミュレーション時間の表現の違いは、HDL Verifier インターフェイスを使用して 2 つの方法のいずれかで調整できます。

タイミング関係を手動で定義する(Timescales ペインを使用)

関係を手動で定義する場合は、HDL シミュレーターで Simulink の 1 秒を表すフェムト秒、ピコ秒、ナノ秒、マイクロ秒、ミリ秒、秒、またはティックの数を決定します。

この HDL シミュレータ時間の量は、次のいずれかの方法で表現できます。

相対的な用語で(つまり、HDL シミュレータのティック数として)。この場合、コシミュレーションは 相対タイミング モード で動作すると言われます。HDL Cosimulation ブロックは、コシミュレーションの相対タイミング モードにデフォルト設定されます。相対タイミング モードの詳細については、相対タイミングモード を参照してください。

絶対単位(ミリ秒やナノ秒など)。この場合、コシミュレーションは 絶対タイミング モード で動作すると言われます。絶対タイミング モードの詳細については、絶対タイミングモード を参照してください。

相対時間と絶対時間の詳細については、シミュレーションのタイムスケール を参照してください。

HDL Verifier がタイムスケールを定義できるようにする(Timescales ペインを使用)

リンク ソフトウェアでタイミング関係を定義できるようにすると、HDL シミュレータと Simulink 間のタイムスケール係数を、HDL シミュレータの 1 秒 = Simulink の 1 秒にできるだけ近くなるように設定しようとします。この設定が不可能な場合、リンク製品は Simulink モデル ポートの信号レートを HDL シミュレータ ティックの可能な限り低い数に設定しようとします。

始める前に、HDL シミュレータが実行中であることを確認してください。HDL Verifier ソフトウェアは、HDL シミュレータが実行中の場合のみ、HDL シミュレータの解像度制限を取得できます。

ブロック ダイアログでパラメータを設定するときに Timescale オプションをクリックしてから Determine Timescale Now をクリックすると、HDL Verifier でタイムスケールを計算するように選択できます。また、シミュレーションの開始時に Automatically determine timescale at start of simulation を選択すると、HDL Verifier でタイムスケールを計算するように選択できます。

Determine Timescale Now をクリックすると、HDL Verifier は Simulink を HDL シミュレータに接続し、HDL シミュレータの解像度を使用して最適なタイムスケールを計算できるようになります。HDL Verifier が提案するタイムスケールを受け入れることも、ポート リストを直接変更することもできます。最初に計算された設定に戻す場合は、Use Suggested Timescale をクリックします。HDL デザイン内のすべてのポートのサンプル時間を表示する場合は、Show all ports and clocks を選択します。

Automatically determine timescale at start of simulation を選択すると、Simulink でシミュレーションが開始されたときに同じダイアログが表示されます。該当する場合は、ブロックを構成するときに Determine Timescale Now をクリックした場合と同じ調整をその時点で行います。

HDLコシミュレーションブロックで通信リンクを構成する

共有メモリまたはソケット通信を選択する必要があります。MATLAB または Simulink を使用した HDLコシミュレーションを参照してください。

通信の種類を決定したら、ブロック パラメータ ダイアログ ボックスの Connection ペインでブロックの通信リンクを構成します (例では ModelSim での使用を示しています)。

通信構成については、次の手順で説明します。

Simulink と HDL シミュレータが同じコンピュータ上で実行されているかどうかを判断します。そうであれば、手順 4 に進みます。

The HDL simulator is running on this computerをクリア。(このチェックボックスはデフォルトでオンになっています。)Simulink と HDL シミュレーターは異なるコンピューター上で実行されているため、HDL Verifier は Connection method を

Socketに設定します。Host name テキスト フィールドに、HDL シミュレーション (HDL シミュレータ内) を実行しているコンピューターのホスト名を入力します。Port number or service テキスト フィールドに、コンピュータ システムの有効なポート番号またはサービスを指定します。TCP/IP ソケット ポートの選択については、TCP/IPソケットポート を参照してください。手順 5 に進みます。

HDL シミュレータと Simulink が同じコンピュータ上で実行されている場合は、通信チャネルに共有メモリを使用するか、TCP/IP ソケットを使用するかを決定します。さまざまな通信モードの詳細については、「MATLAB または Simulink を使用した HDLコシミュレーション」を参照してください。

TCP/IP ソケット通信を選択した場合は、Port number or service テキスト フィールドにコンピュータ システムの有効なポート番号またはサービスを指定します。TCP/IP ソケット ポートの選択については、TCP/IPソケットポート を参照してください。

共有メモリ通信を選択する場合は、Shared memory チェックボックスをオンにします。

Simulink シミュレーションを実行するときに HDL シミュレーターをバイパスする場合は、Connection Mode オプションを使用して、必要なシミュレーション接続のタイプを指定します。次のいずれかのオプションを選択します。

Full Simulation:インターフェースを確認し、HDL シミュレーションを実行します (デフォルト)。

Confirm Interface Only:HDL シミュレーターで予想される信号名、次元、データ型を確認しますが、HDL シミュレーションは実行しません。

No Connection:HDL シミュレータと通信しないでください。HDL シミュレータを起動する必要はありません。

2 番目と 3 番目のオプションでは、HDL Verifier ソフトウェアは Simulink シミュレーション中に HDL シミュレータと通信しません。

[適用] をクリックします。

次の例のダイアログ ボックスは、HDL Cosimulation ブロックの通信定義を示しています。ブロックは、同じコンピュータ上で実行されている Simulink と HDL シミュレータ用に構成され、TCP/IP ポート 4449 を介して TCP/IP ソケット モードで通信します。

HDL コシミュレーション ブロック パラメータ ダイアログ ボックスでシミュレーション前およびシミュレーション後の Tcl コマンドを指定する

HDL シミュレータが Simulink モデルの HDL コンポーネントをシミュレートする前と後に実行する Tcl コマンドを指定するオプションがあります。Tcl は、ほとんどの HDL シミュレーション環境でサポートされているプログラム可能なスクリプト言語です。Tcl の使用範囲は、シミュレーションが実行中であることを確認するための 1 行の puts コマンドのような単純なものから、広範なシミュレーションの初期化と起動シーケンスを実行する複雑なスクリプトのような完全なものまで多岐にわたります。たとえば、シミュレーション ペインの Post- simulation command フィールドを使用して、シミュレーション実行の終了時に HDL シミュレータを再起動するように指示できます。

ModelSim ユーザーへの注意

各シミュレーションの後、カバレッジ結果を更新するには ModelSim 時間がかかります。このプロセスと次のコシミュレーション セッション間の潜在的な競合を防ぐには、各連続シミュレーションの間に短い一時停止を追加します。

HDL Cosimulation ブロック パラメータ ダイアログ ボックスの Simulation ペインの Pre-simulation コマンドまたは Post-simulation コマンド テキスト フィールドに Tcl コマンドを入力することにより、シミュレーション前およびシミュレーション後の Tcl コマンドを指定できます。

Tcl コマンドを指定するには、次の手順を実行します。

ブロック パラメータ ダイアログ ボックスの Simulation タブを選択します。ダイアログ ボックスは次のように表示されます (ModelSim での使用例を示します)。

Pre-simulation commands テキスト ボックスには、参照用の

putsコマンドが含まれています。Pre-simulation command および Post-simulation command テキスト ボックスに 1 つ以上のコマンドを入力します。テキスト ボックスでは、1 行につき 1 つの Tcl コマンドを指定することも、各コマンドの後に標準の Tcl 連結演算子であるセミコロン (;) を追加して 1 行につき複数のコマンドを入力することもできます。

[適用] をクリックします。

プログラムによるブロックパラメータの制御

ブロック パラメータを制御する 1 つの方法は、HDL Cosimulation ブロックのグラフィカル ダイアログ ボックスを使用することです。ただし、マスク パラメータ値とシミュレーションの実行をプログラムで制御することで、ブロックを制御することもできます。パラメータ値は、Simulink get_param 関数を使用して読み取り、Simulink set_param 関数を使用して書き込むことができます。すべてのブロック パラメータには、次のいずれであるかを示す属性があります。

調整可能 - シミュレーションの実行中に属性が変更される場合があります。

評価済み - パラメータ値は評価され、S 関数によって使用される実際の値が決定されます。

HDL Cosimulation ブロックには調整可能なパラメーターがないため、シミュレーションの実行中に値を変更しようとするとエラーが発生します。ただし、評価されるパラメータはいくつかあります。

ブロックを右クリックし、View Mask を選択してから Parameters タブを選択すると、パラメータとその属性のリストが表示されます。Variable 列にはプログラム パラメータ名が表示されます。あるいは、HDL Cosimulation ブロックを選択し、MATLAB プロンプトで次のコマンドを入力して、プログラムで名前を取得することもできます。

>> get_param(gcb, 'DialogParameters')

MATLAB を使用してシミュレーションを制御し、パラメータ値をマスクする例をいくつか示します。通常、コマンドはスクリプトまたは関数ファイルに配置され、モデル開発者が利用できるいくつかのコールバック フックによって呼び出されます。コードは、次の推奨される Simulink 場所のいずれかに配置できます。

モデルワークスペース内。[モデル化] タブの [設計] セクションで、[モデル エクスプローラー] をクリックします。モデル エクスプローラー ダイアログ ボックスの Model Hierarchy ペインで、Simulink Root 、

model_name、 Model Workspace を選択します。Model Workspace ペインの Data source リストから。Model Fileを選択します。モデルコールバック内。Modeling タブの Setup セクションで、Model Settings 、 Model Properties をクリックします。[モデル プロパティ] ダイアログ ボックスの [Callbacks] タブでコールバック関数を指定します。

サブシステムのコールバック内。空のサブシステムを右クリックし、Properties 、 Callbacks を選択します。多くの HDL Verifier デモでは、この手法を使用して、

OpenFcnコールバックに MATLAB コードを配置することで HDL シミュレーターを起動します。HDL Cosimulation ブロックのコールバック内。HDL Cosimulation ブロックを右クリックし、Properties 、 Callbacks を選択します。

次に例を示します。HDL シミュレータ通信用のソケット番号の値をスクリプト化する. 回帰環境では、他のシミュレーション実行との衝突を避けるために、シミュレーション中に Simulink/HDL シミュレータ接続のソケット番号を決定する必要がある場合があります。getAvailableSocketPort 関数を使用して使用可能なソケットを確認し、Simulink と HDL シミュレーターの両方がそのソケットを使用するように設定します。

この例では、Questa® を HDL シミュレータとして使用し、Linux® プラットフォームでそのタスクを処理できるコードを示します。

p = getAvailableSocketPort();

set_param('mymodel/HDL Cosimulation',CommSharedMemory='off',CommPortNumber=num2str(p));

vsim(socketsimulink=p, tclstart={});incisiveを使用する場合は、nclaunch関数を使用してソケットを設定し、シミュレータを起動します。

nclaunch(socketsimulink=p, tclstart={});