このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

サポートされているデータ型

HDL データを変換して MATLAB または Simulink に送信する

HDL アプリケーションで HDL データを MATLAB® 関数または Simulink® ブロックに送信する必要がある場合は、まずデータを MATLAB および HDL Verifier™ ソフトウェアでサポートされている型に変換する必要があります。

HDL モデルの MATLAB 関数または Simulink ブロックをプログラムするには、アプリケーションに必要な型変換を理解する必要があります。また、使用している HDL と MATLAB で使用される配列インデックス規則の違いを処理する必要がある場合もあります (次のセクションを参照)。

関数に渡される引数のデータ型によって、次のことが決まります。

データを操作する前に必要な変換の種類

HDLシミュレータにデータを返すために必要な変換の種類

次の表は、型がスカラーか配列かに基づいて、HDL Verifier ソフトウェアがサポートされている VHDL® データ型を MATLAB 型に変換する方法をまとめたものです。

VHDL から MATLAB へのデータ型変換

| VHDL タイプ... | スカラーが変換されると... | 配列が変換されると... |

|---|---|---|

STD_LOGIC、STD_ULOGIC および BIT | 目的の論理状態の文字リテラルに一致する文字。 | |

STD_LOGIC_VECTOR、STD_ULOGIC_VECTOR、BIT_VECTOR、SIGNED、および UNSIGNED | 文字ごとに 1 ビットを持つ文字の列ベクトル (VHDL HDL シミュレータの変換 で定義)。 | |

STD_LOGIC_VECTOR、STD_ULOGIC_VECTOR、BIT_VECTOR、SIGNED、UNSIGNED の配列 | VHDL ポート サイズと同等のサイズの文字配列 (上記で定義)。 | |

INTEGER および NATURAL | 「int32」を入力します。 | VHDL ポート サイズと同等のサイズを持つ int32 型の配列。メモ

|

REAL | 「double」を入力します。 | VHDL ポート サイズと同等のサイズを持つ double 型の配列。メモ

|

TIME | 秒単位の時間値の場合は double と入力し、シミュレータの時間増分を表す値の場合は int64 と入力します (hdldaemon の 'time' オプションの説明を参照してください)。 | VHDL ポート サイズと同等のサイズを持つ double または int64 型の配列。 |

| 列挙型 | VHDL ラベルまたは文字リテラルの MATLAB 表現を含む文字ベクトルまたは文字列スカラー。たとえば、ラベル high は 'high' に変換され、文字リテラル 'c' は '''c''' に変換されます。 | 定義された列挙型のラベルに等しい各要素を持つ文字ベクトルのセル配列または文字列配列。各要素は、VHDL ラベルまたは文字リテラルの MATLAB 表現です。たとえば、ベクトル (one, '2', three) は列ベクトル ['one'; '''2'''; 'three'] に変換されます。文字リテラルのみを含むユーザー定義の列挙型で、STD_LOGIC_VECTOR、STD_ULOGIC_VECTOR、BIT_VECTOR、SIGNED、UNSIGNED 型で示されているように、文字のベクトルまたは配列に変換されます。 |

次の表は、HDL Verifier ソフトウェアがサポートされている Verilog® データ型を MATLAB 型に変換する方法をまとめたものです。このソフトウェアは、Verilog に対して最大 128 ビットのパック配列をサポートします。

Verilog から MATLAB へのデータ型変換

| Verilog タイプ... | 変換すると… |

|---|---|

wire, reg | 目的の論理状態 (ビット) の文字リテラルに一致する文字または文字の列ベクトル。 |

次の表は、HDL Verifier ソフトウェアがサポートされている SystemVerilog データ型を MATLAB 型に変換する方法をまとめたものです。このソフトウェアは、SystemVerilog の最大 128 ビットのパック配列をサポートします。

SystemVerilog から MATLAB へのデータ型変換

| SystemVerilog 型... | 変換すると… |

|---|---|

wire, reg, logic | 目的の論理状態 (ビット) の文字リテラルに一致する文字または文字の列ベクトル。 |

integer | 目的の論理状態 (ビット) の文字リテラルに一致する 32 要素の文字の列ベクトル。出力のみサポートされます。 |

bit | boolean/ufix1 |

byte | int8/uint8 |

shortint | int16/uint16 |

int | int32 |

longint | int64/uint64 |

real | double |

packed array (ビット/ロジック ベクトル) |

|

SystemVerilog から Simulink へのデータ型変換

| SystemVerilog 型... | 変換すると… |

|---|---|

wire, reg, logic | 目的の論理状態 (ビット) の文字リテラルに一致する文字または文字の列ベクトル。 |

integer | 目的の論理状態 (ビット) の文字リテラルに一致する 32 要素の文字の列ベクトル。出力のみサポートされます。 |

bit | boolean/ufix1 |

byte | int8/uint8 |

shortint | int16/uint16 |

int | int32 |

longint | int64/uint64 |

real | double |

packed array (ビット/ロジック ベクトル) |

|

unpacked array | Simulink ベクトル。詳細については、Simulink SystemVerilog アンパック配列のサポート を参照してください。 |

struct | 各構造体メンバーは単一のポートとして表されます。 メモ

|

メモ

SystemVerilog のサポートには、上記のタイプの信号が含まれます。次の SystemVerilog タイプはサポートされていません。

shortrealSystemVerilog タイプunionSystemVerilog タイプネストされた構造

SystemVerilog インターフェース

MATLAB と HDL のビットベクトル インデックスの違い

HDL では、MSB-0 または LSB-0 の番号付けを使用してビット ベクトルを柔軟に定義できます。MATLAB では、ビット ベクトルは常に LSB-0 番号付けと見なされます。データの破損を防ぐために、HDL インターフェイスには LSB-0 インデックスを使用することをお勧めします。

VHDL でロジック ベクトルを次のように定義します。

signal s1 : std_logic_vector(7 downto 0);

または Verilog では次のようにします。

reg[7:0] s1;

これはMATLABのint8にマッピングされ、s1[7]がMSBになります。あるいは、VHDL ロジック ベクトルを次のように定義します。

signal s1 : std_logic_vector(0 to 7);

または Verilog では次のようにします。

reg[0:7] s1;

これはMATLABのint8にマッピングされ、s1[0]がMSBになります。

MATLAB と HDL の配列インデックスの違い

多次元配列では、同じ基礎となる OS メモリ バッファーが、MATLAB と HDL シミュレーターの異なる要素にマップされます (このマッピングは、異なる言語が同じ配列の要素に名前を付けるために提供する異なる方法のみを反映しています)。matlabtb 関数と matlabcp 関数の両方を使用する場合は、両方のアプリケーションで一貫して値を割り当て、解釈するように注意してください。

HDL では、多次元配列は次のように宣言されます。

type matrix_2x3x4 is array (0 to 1, 4 downto 2) of std_logic_vector(8 downto 5);

メモリレイアウトは次のようになります。

bit 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 - dim1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 dim2 4 4 4 4 3 3 3 3 2 2 2 2 4 4 4 4 3 3 3 3 2 2 2 2 dim3 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5

この同じレイアウトは、次の MATLAB 4x3x2 マトリックスに対応します。

bit 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 - dim1 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 dim2 1 1 1 1 2 2 2 2 3 3 3 3 1 1 1 1 2 2 2 2 3 3 3 3 dim3 1 1 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2 2 2 2 2 2 2 2

したがって、H が HDL 配列で、M が MATLAB 行列である場合、次のインデックス値は同じになります。

b1 H(0,4,8) = M(1,1,1) b2 H(0,4,7) = M(2,1,1) b3 H(0,4,6) = M(3,1,1) b4 H(0,4,5) = M(4,1,1) b5 H(0,3,8) = M(1,2,1) b6 H(0,3,7) = M(2,2,1) ... b19 H(1,3,6) = M(3,2,2) b20 H(1,3,5) = M(4,2,2) b21 H(1,2,8) = M(1,3,2) b22 H(1,2,7) = M(2,3,2) b23 H(1,2,6) = M(3,3,2) b24 H(1,2,5) = M(4,3,2)

このインデックスを N 次元に拡張できます。一般に、左から右に番号が付けられている場合、寸法は逆になります。HDL の右端の次元は、MATLAB の左端の次元に対応します。

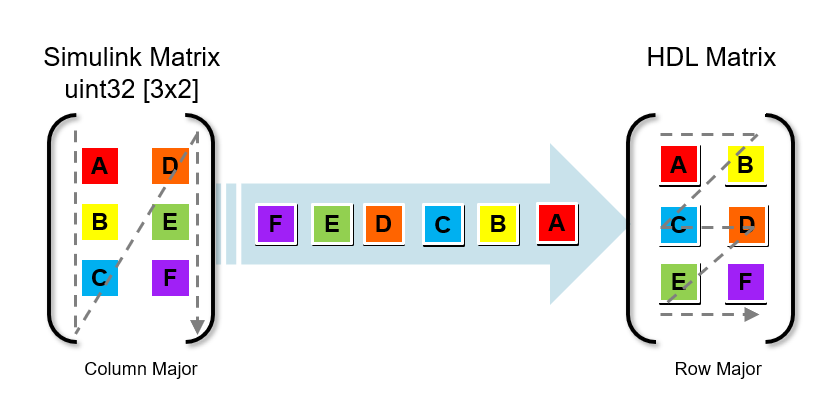

配列のインデックス - 列優先

SystemVerilog DUT を使用して Simulink コシミュレーションを実行し、DUT に unpacked array ポートが含まれている場合、HDL Verifier は列優先順に配列をインデックスすることに注意してください。たとえば、次のように定義された 3x2 HDL マトリックスの場合:

logic [31:0] In1 [0:2][0:1]

この図では、列優先で Simulink 行列をインデックスすると、次の順序で列ごとに要素が読み取られます。

A, B, C, D, E, F

m1 が Simulink マトリックスで、m2 が HDL マトリックスである場合、次のインデックス値は同じになります (Simulink インデックス モードが 0-base であると仮定)。m1(0,0) = m2(0,0) = A m1(1,0) = m2(0,1) = B m1(2,0) = m2(1,0) = C m1(0,1) = m2(1,1) = D m1(1,1) = m2(2,0) = E m1(2,1) = m2(2,1) = F

操作のためのデータの変換

シミュレーション MATLAB 関数が HDL シミュレータから受信したデータをどのように使用するかに応じて、データを操作する前に、データを別の型に変換するように関数をコーディングする必要がある場合があります。次の表に、このような変換が必要となる状況を示します。

必要なデータ変換

| この機能が必要な場合... | 説明 |

|---|---|

double以外の型として受信された数値データを計算します | 計算を実行する前に、 datas(inc+1) = double(idata); |

| 標準ロジックまたはビットベクトルを符号なし整数または正の小数に変換する |

uval = mvl2dec(oport.val) この例では、標準ロジックまたはビット ベクトルが文字リテラル

この機能の詳細については、 |

| 標準ロジックまたはビットベクトルを負の小数に変換する |

suval = mvl2dec(oport.val, true); この例では、標準ロジックまたはビット ベクトルが文字リテラル |

例

次のコードの抜粋は、コールバックに渡されるデータのデータ型変換を示しています。

InDelayLine(1) = InputScale * mvl2dec(iport.osc_in',true);

この例では、次のように all 関数を使用して、VHDL タイプ STD_LOGIC および STD_LOGIC_VECTOR のポート値をテストします。

all(oport.val == '1' | oport.val == '0')

この例では、すべての要素が '1' または '0' の場合に True を返します。

HDLシミュレータに戻すためのデータの変換

シミュレーション MATLAB 関数が HDL シミュレータにデータを返す必要がある場合は、まずデータを HDL Verifier ソフトウェアでサポートされている型に変換する必要があります。次の表は、VHDL および Verilog に対してこのような変換が必要となる状況を示しています。

メモ

データ値が HDL シミュレータに返されるとき、char 配列のサイズは、該当する場合は先頭のゼロを含めて HDL 型と一致する必要があります。次に例を示します。

oport.signal = dec2mvl(2)

signal が HDL で 2 ビット型の場合にのみ機能します。HDL タイプが他の場合、2 番目の引数を 指定する必要があります。

oport.signal = dec2mvl(2, N)

ここで、N は HDL データ型のビット数です。

VHDL HDL シミュレータの変換

| タイプ...の IN ポートにデータを返すには | 説明 |

|---|---|

STD_LOGIC、STD_ULOGIC または BIT | 目的のロジック状態の文字リテラルに一致する文字としてデータを宣言します。 iport.s1 = 'X'; %STD_LOGIC iport.bit = '1'; %BIT |

STD_LOGIC_VECTOR、STD_ULOGIC_VECTOR、BIT_VECTOR、SIGNED または UNSIGNED | データを、文字ごとに 1 ビットを持つ文字の列ベクトルまたは行ベクトル (上記で定義) として宣言します。次に例を示します。 iport.s1v = 'X10ZZ'; %STD_LOGIC_VECTOR iport.bitv = '10100'; %BIT_VECTOR iport.uns = dec2mvl(10,8); %UNSIGNED, 8 bits |

STD_LOGIC_VECTOR、STD_ULOGIC_VECTOR、BIT_VECTOR、SIGNED、または UNSIGNED の配列 | データを、VHDL ポート サイズと同等のサイズの文字型の配列として宣言します。MATLAB と HDL の配列インデックスの違いを参照してください。 |

INTEGER または NATURAL | データを、VHDL 配列サイズと同等のサイズを持つ iport.int = int32(1:10)'; メモ

|

REAL | データを、VHDL ポート サイズと同等のサイズを持つ iport.dbl = ones(2,2); メモ

|

TIME | VHDL iport.t1 = int64(1:10)'; %Simulator time

%increments

iport.t2 = 1e-9; %1 nsec

|

| 列挙型 | スカラー ポートの場合はデータを文字ベクトルまたは文字列スカラーとして宣言し、配列ポートの場合は各要素が定義された列挙型のラベルに等しい文字ベクトルのセル配列または文字列配列として宣言します。 iport.char = {'''A''', '''B'''}; %Character

%literal

iport.udef = 'mylabel'; %User-defined label

|

| 標準ロジックまたはビット表現の文字配列 | 整数を変換するには、 oport.slva =dec2mvl([23 99],8)'; |

Verilog HDL シミュレータの変換

タイプ...の input ポートにデータを返すには | 説明 |

|---|---|

reg, wire | 目的の論理状態の文字リテラルに一致する文字または文字の列ベクトルとしてデータを宣言します。次に例を示します。 iport.bit = '1'; |

HDL シミュレータ用の SystemVerilog 変換

タイプ...の input ポートにデータを返すには | 説明 |

|---|---|

reg, wire, logic | 目的の論理状態の文字リテラルに一致する文字または文字の列ベクトルとしてデータを宣言します。次に例を示します。 iport.bit = '1'; |

integer | データを、文字ごとに 1 ビットを持つ 32 要素の列ベクトル文字 (上記で定義) として宣言します。 |

パック配列は最大 128 ビットまでサポートされます。

メモ

SystemVerilog のサポートには、上記のタイプのスカラー信号のみが含まれます。次の SystemVerilog タイプはサポートされていません。

配列と多次元配列

shortrealSystemVerilog タイプSystemVerilog 集約型(

unionやstructなど)SystemVerilog インターフェース

Simulink ワイド HDL ポートの処理

HDL モジュールに 128 ビットより広いポートがある場合、Simulink はこのポートを表すポートのベクトルを作成します。Cosimulation Wizard は HDL ポートのサイズを推測します。次に、HDL Cosimulation ブロックで Simulink ワード長 パラメータを設定できます。

入力ポートの場合 — Simulink ポートの寸法は、コンパイル時に駆動信号のデータ型によって決定されます。次に例を示します。

HDL ワード長 = 150 かつ Simulink ワード長 = 50 の場合、HDL Verifier は、データ幅が 50 ビットで、

sfix50(3)やufix50(3)などのサイズ 3 の次元を持つ Simulink ポートを許可します。HDL ワード長 = 140 かつ Simulink ワード長 = 50 の場合、HDL Verifier は 150 ビットの Simulink を 140 ビットの HDL にパックします。HDL Verifier は最後のワードの最上位 10 ビット (MSB) を無視します。

出力ポート用

HDL Verifier は出力ポートを表すポートのベクトルを作成します。次に例を示します。

HDL ワード長 = 150 かつ Simulink ワード長 = 50 の場合、HDL Verifier はデータ幅が 50 ビットの Simulink ポートを作成します。たとえば、

sfix50(3)またはufix50(3)です。HDL ワード長 = 150 かつ Simulink ワード長 = 60 の場合、HDL Verifier は

sfix60(3)やufix60(3)など、データ幅が 60 の Simulink ポートを作成します。HDL ワードには 150 ビットしかなく、Simulink ポートには 180 ビットが必要なので、30 ビットがパディングまたは符号拡張されます。HDL ワード長 = 140 かつ Simulink ワード長 = 50 の場合、HDL 出力の 50 ビットごとに Simulink ワードとして表されます。最後の Simulink ワードの上位 10 ビットは未使用で、Sign パラメータに従って拡張されます。

Simulink SystemVerilog アンパック配列のサポート

既存の HDL DUT がある場合 — Cosimulation Wizard を使用して、インターフェイス上にアンパックされた配列を含む SystemVerilog DUT をインポートする場合、HDL Verifier は次の規則に従います。

入力ポートの場合、HDL Cosimulation ブロックは Simulink からの行列データを受け入れることができます。

出力ポートの場合、HDL Cosimulation ブロックはフラットなデータ ベクトルを出力します。

HDL Verifier は、配列と行列を列優先の順序で解釈します。詳細については、配列のインデックス - 列優先を参照してください。

たとえば、SystemVerilog DUT が 2 x 5 のアンパック配列の入力ポートと出力ポートを持つこのインターフェイスを定義している場合:

module myDUT

(input logic clk,

input logic clk_en,

input logic[31:0] In1[0:1] [0:4],

output logic[31:0] Out1[0:1] [0:4],

output logic ce_out);これで、int32 [2x5] などの int32 の 10 個の要素を持つ入力を駆動する Simulink テストベンチを作成できます。出力ポートは、10 個の要素のフラット配列 int32 [10x1] にマップされます。

![HDL Cosimulation block showing input port with data type int32[2x5] and output port of type int32(10)](unpackedarray0.png)

HDL DUT を生成する場合 — HDL Workflow Advisor を使用して SystemVerilog DUT を生成する場合、HDL Verifier は DUT インターフェイス上の 1 次元配列 (ベクトル) のみのコシミュレーション テストベンチ モデルを生成できます。

Vivado のアンパック配列のサポート

Vivado シミュレーターはパックされた次元とパックされていない次元を区別できないため、HDL Verifier は最下位の次元をパックされた次元として扱い、残りをパックされていない次元として扱います。

次に例を示します。

SystemVerilog に

Logic [7:0][3:0] dataAとして定義されたポートがある場合、Simulink はそれをデータ型fixdt4の 8 つの要素の配列にマップします。SystemVerilog に

Logic [3:0][7:0] dataB [1:3][4:6]として定義されたポートがある場合、Simulink はそれをデータ型fixdt8の 36 要素 (3*3*4の積) の配列にマップします。

Simulink Verilog および SystemVerilog 列挙型のサポート

既存の HDL DUT がある場合 — Cosimulation Wizard を使用して、インターフェイス上に enum タイプのポートを含む DUT をインポートすると、HDL Verifier はポートを固定小数点ロジック ベクターにマップします。その論理ベクトルのサイズは、enum 型を表すために必要なビット数によって決まります。

たとえば、SystemVerilog DUT が BasicColors 入力ポートと出力ポートを使用してこのインターフェイスを定義している場合、ポートは ufix2 タイプの入力または出力にマップされます。

typedef enum logic [1:0] {

Red,

Yellow,

Blue

} t_BaiscColors;

module scalarEnums

( input t_BasicColors In1,

output t_BasicColors Out1);

HDL DUT を生成する場合 — HDL Workflow Advisor を使用して Verilog または SystemVerilog DUT を生成する場合、HDL Verifier はコシミュレーション テストベンチ モデルを生成し、DUT に一致する Simulink.IntEnumType データ型を使用するように型を変換します。Simulink 列挙の詳細については、列挙型のコードの生成 (Simulink) を参照してください。

VHDL は列挙型をサポートしていません。

参考

Cosimulation Wizard | HDL Cosimulation | hdlverifier.HDLCosimulation