このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

シミュレーションのタイムスケール

シミュレーション時間の表現の概要

シミュレーション時間の表現は、HDL シミュレータと Simulink® では大きく異なります。各アプリケーションには独自のタイミング エンジンがあり、検証ソフトウェアは 2 つのアプリケーション間のシミュレーション時間を同期する必要があります。

HDL シミュレータでは、シミュレーション時間の単位は ティック と呼ばれます。ティックの持続時間は、HDL シミュレータの 解像度制限 によって定義されます。デフォルトの解像度制限は 1 ns ですが、シミュレータによって異なる場合があります。

ModelSim® ユーザー:

現在の ModelSim 解像度制限を確認するには、ModelSim プロンプトで

echo $resolutionまたはreport simulator stateと入力します。ModelSim コマンド ラインで-tオプションを指定するか、ModelSim シミュレート ダイアログ ボックスで別のシミュレータ解像度を選択することで、デフォルトの解像度制限を上書きできます。ModelSim で使用可能な解像度は、fs、ps、ns、us、ms、または sec 単位で 1x、10x、または 100x です。詳細については、ModelSim のドキュメントを参照してください。Xcelium™ ユーザー:

現在の HDL シミュレータの解像度制限を確認するには、HDL シミュレータのプロンプトで「

echo $timescale」と入力します。詳細については、HDL シミュレータのドキュメントを参照してください。Vivado® ユーザー:HDL Cosimulation ブロックマスクを開きます。HDL Time Precision パラメータの値は Block Info タブで確認できます。この値を変更するには、Cosimulation Wizard を開き、Simulation Options ペインで別の HDL time precision パラメータを指定してブロックを再生成する必要があります。

Simulink は、シミュレーション時間を秒単位の倍精度値として保持します。この表現は、連続システムと離散システムの両方のモデリングに対応します。

Simulink と HDL シミュレータのタイミングの関係は、シミュレーションの次の側面に影響します。

シミュレーション合計時間

入力ポートのサンプル時間

出力ポートのサンプル時間

クロック周期

シミュレーションの実行中、Simulink は各中間ステップで現在のシミュレーション時間を HDL シミュレータに伝達します。(中間ステップは Simulink サンプル時間ヒットに対応します。各中間ステップで、入力ポートに新しい値が適用されるか、出力ポートがサンプリングされます。

協調シミュレーション中に HDL シミュレータを Simulink で最新の状態にするには、サンプリングされた Simulink 時間を HDL シミュレータ時間 (ティック) に変換し、計算されたティック数だけ HDL シミュレータを実行できるようにする必要があります。

Simulink と HDL シミュレータのタイミング関係の定義

シミュレーション時間の表現の違いは、HDL Verifier™ インターフェイスを使用して 2 つの方法のいずれかで調整できます。

タイミング関係を手動で定義する(Timescales ペインを使用)

関係を手動で定義する場合は、HDL シミュレーターで Simulink の 1 秒を表すフェムト秒、ピコ秒、ナノ秒、マイクロ秒、ミリ秒、秒、またはティックの数を決定します。

HDL Verifier がタイムスケールを定義できるようにする(Timescales ペインを使用)

ソフトウェアでタイミング関係を定義できるようにすると、ソフトウェアは HDL シミュレータと Simulink 間のタイムスケール係数を、HDL シミュレータの 1 秒 = Simulink の 1 秒にできるだけ近くなるように設定しようとします。この設定が不可能な場合、HDL Verifier は Simulink モデル ポートの信号レートを HDL シミュレータ ティックの可能な限り低い数に設定しようとします。

HDL Verifier でタイミング モードを設定する

HDL Cosimulation ブロック パラメータ ダイアログ ボックスの Timescales ペインは、1 秒の Simulink 時間と HDL シミュレータ時間の量との間の対応を定義します。この HDL シミュレータ時間の量は、次のいずれかの方法で表現できます。

相対的な用語で(つまり、HDL シミュレータのティック数として)。この場合、コシミュレーションは 相対タイミング モード で動作すると言われます。HDL コシミュレーション ブロックは、コシミュレーションの相対タイミング モードをデフォルトにします。相対タイミング モードの詳細については、相対タイミングモード を参照してください。

絶対単位(ミリ秒やナノ秒など)。この場合、コシミュレーションは 絶対タイミング モード で動作すると言われます。絶対タイミング モードの詳細については、絶対タイミングモード を参照してください。

Timescales ペインでは、HDL シミュレータと同等のものを入力するか、HDL Verifier にタイムスケールを計算させることによって、Simulink と HDL シミュレータ間の最適なタイミング関係を選択できます。

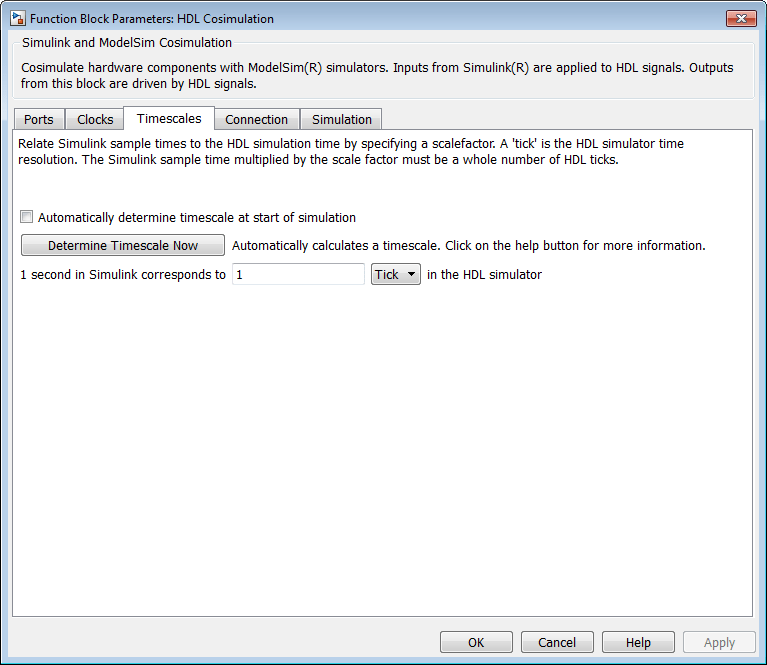

ブロック ダイアログでパラメータを設定するときに、Timescale オプションをクリックしてから Determine Timescale Now をクリックすると、HDL Verifier でタイムスケールを計算するように選択できます (このパラメータは、Vivado の場合は Show Times and Suggest Timescale として表示されます)。また、Automatically determine timescale at start of simulation を選択すると、シミュレーションの開始時に HDL Verifier でタイムスケールを計算するように選択できます。

次の図は、Timescales ペインのデフォルト設定を示しています (示されている例は、ModelSim での使用です)。

タイミング モードを手動で設定するか、Timescales ダイアログ ボックスを使用して設定する手順については、HDL Cosimulation ブロック リファレンスの Timescales ペインを参照してください。

タイミング関係を自動的に指定する

HDL Verifier ソフトウェアでタイミング関係を計算するには:

HDL シミュレータを起動します。HDL Verifier ソフトウェアは、HDL シミュレータが実行されている場合にのみ、HDL シミュレータの解像度制限を取得できます。

HDL Verifier ソフトウェアにタイムスケールをすぐに提案させるか、Simulink シミュレーションの開始時にタイムスケールを計算するかを選択します。

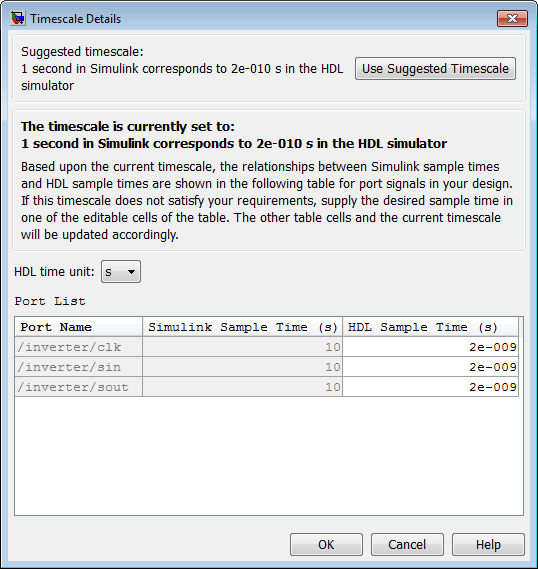

ブロックの設定中に計算を実行するには、[Timescale] タブで [Determine Timescale Now] をクリックします。ソフトウェアは Simulink を HDL シミュレータに接続し、Simulink が HDL シミュレータの解像度を使用して最適なタイムスケールを計算できるようにします。リンクにより、その結果が Timescale Details ダイアログ ボックスに表示されます。

提案されたタイムスケールを受け入れるか、ポート リストを直接変更することができます。

元の計算された設定に戻すには、Use Suggested Timescale をクリックします。

HDL デザイン内のすべてのポートのサンプル時間を表示するには、Show all ports and clocks を選択します。

シミュレーションの開始時に計算を実行するには、Automatically determine timescale at start of simulation を選択し、Apply をクリックします。Simulink でシミュレーションを開始すると、同じ Timescale Details ダイアログ ボックスが表示されます。

結果を表示するには、HDL シミュレータが実行されており、設計がコシミュレーション用にロードされていることを確認してください。シミュレーションを実行する必要はありません。

HDL Verifier ソフトウェアは、スケール係数を計算するときに、HDL コシミュレーション ブロックからのすべてのクロックおよびポート信号レートを分析します。

リンク ソフトウェアは、サンプル レートを秒またはティック単位で返します。

結果が秒単位の場合、リンク ソフトウェアは忠実度 (絶対時間) を優先してタイミングの違いを解決できました。

結果がティック単位の場合、リンク ソフトウェアは効率性 (相対時間) を優先してタイミングの違いを最もうまく解決できました。

Determine Timescale Now または Automatically determine timescale at start of simulation を選択するたびに、インタラクティブな表示が開きます。この表示では、タイムスケールの計算結果が説明されます。リンク ソフトウェアが指定されたサンプル時間のタイムスケールを計算できない場合は、Port List でサンプル時間を調整します。

変更をコミットするには、Apply をクリックします。

制限

HDL Verifier は、フレームベースの信号から自動的に計算されるタイムスケールをサポートしていません。

HDL Verifier ソフトウェアは、Tcl コマンドまたは HDL シミュレータで駆動される信号に基づいてサンプル タイムスケールを自動的に計算することはできません。リンク ソフトウェアはこれらの信号のレートを認識できないため、このような計算を実行できません。

結果を表示するには、HDL シミュレータが実行されており、設計がコシミュレーション用にロードされていることを確認してください。シミュレーションを実行する必要はありません。

相対タイミングモード

相対タイミング モードは、Simulink のシミュレーション時間と HDL シミュレータ間の次の 1 対 1 の対応を定義します。

Simulink の 1 秒 は、HDL シミュレータの N ティック に相当します。ここで、N はスケール係数です。 |

この対応は、HDL シミュレータのタイミング解像度に関係なく保持されます。

次の疑似コードは、Simulink 時間単位が HDL シミュレータのティックに変換される方法を示しています。

InTicks = N * tInSecs

ここで、InTicks は HDL シミュレータの時間 (ティック単位)、tInSecs は Simulink の時間 (秒単位)、N はスケール係数です。

相対タイミングモードの動作

HDL Cosimulation ブロックは、スケール係数が 1 の相対タイミング モードにデフォルト設定されます。したがって、1 Simulink 秒は HDL シミュレータの 1 ティックに相当します。デフォルトの場合:

Simulink の合計シミュレーション時間が

N秒として指定されている場合、HDL シミュレーションは正確にNティック (つまり、デフォルトの解像度制限ではNns) 実行されます。同様に、Simulink が HDL Cosimulation ブロック入力ポートのサンプル時間を Tsi 秒として計算すると、新しい値は Tsi ティックの正確な倍数で HDL 入力ポートに格納されます。出力ポートに明示的に指定されたサンプル時間 Tso 秒がある場合、値は HDL シミュレータから Tso ティックの倍数で読み取られます。

相対タイミングモードの例

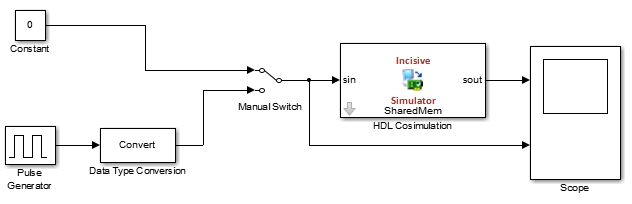

相対タイミング モードの動作を理解するには、次のサンプル モデルのコシミュレーション結果を確認します。

絶対タイミングモード

絶対タイミング モードでは、Simulink と HDL シミュレータ間のタイミング関係を絶対時間単位とスケール係数で定義できます。

| Simulink の 1 秒 は、HDL シミュレータの (N * Tu) 秒 に相当します。ここで、Tu は絶対時間単位 (たとえば、ms、ns など) であり、N はスケール係数です。 |

絶対タイミング モードでは、Simulink 内のすべてのサンプル時間とクロック周期が HDL シミュレータ ティックに量子化されます。次の疑似コードは変換を示しています。

tInTicks = tInSecs * (tScale / tRL)

ここで、

tInTicksは、HDL シミュレータの時間 (ティック単位) です。tInSecsは秒単位の Simulink 時間です。tScaleは、HDL Cosimulation ブロックの Timescales ペインで選択されたタイムスケール設定 (単位とスケール係数) です。tRLは HDL シミュレータの解像度制限です。

たとえば、Timescales ペインの設定が 1 秒で、HDL シミュレータの解像度制限が 1 ns の場合、出力ポートのサンプル時間 12 ns は次のようにティックに変換されます。

tInTicks = 12ns * (1s / 1ns) = 12

絶対タイミングモードの動作

絶対タイミング モードのタイムスケール パラメータを構成するには、Tick を選択するのではなく、Simulink 秒に対応する絶対時間の単位を選択します。

絶対タイミングモードの例

絶対タイミング モードの動作を理解するには、相対タイミングモードの動作 で説明したサンプル モデルをもう一度検討します。モデルが次のように再構成されるとします。

Simulink のシミュレーション パラメータ:

Timescale パラメータ: Simulink 時間の

1 sは HDL シミュレータ時間の1 sに対応します。合計シミュレーション時間:

60e-9 s (60ns)入力ポート (

/inverter/inport) サンプル時間:24e-9 s (24 ns)出力ポート (

/inverter/outport) サンプル時間:12e-9 s (12 ns)クロック (

inverter/clk) 周期:10e-9 s (10 ns)

HDL シミュレータの解像度制限:

1 ns

これらのシミュレーション パラメータを指定すると、Simulink ソフトウェアは HDL シミュレータと 60 ns 間コシミュレーションを実行し、その間に Simulink は 24 ns 間隔で入力をサンプリングし、12 ns 間隔で出力を更新し、10 ns 間隔でクロックを駆動します。

次の図は、コシミュレーション実行後の ModelSim wave ウィンドウを示しています。

タイミングモードの使用に関する考慮事項

タイムスケール モードを設定するときは、次の考慮事項に基づいて設定を選択する必要がある場合があります。

タイミングモードの使用制限

絶対タイミング モードと相対タイミング モードの使用には、次の制限が適用されます。

モデル内の複数の HDL Cosimulation ブロックが HDL シミュレータの単一のインスタンスと通信している場合、すべての HDL Cosimulation ブロックは同じ Timescales ペイン設定を持つ必要があります。

連続したコシミュレーション実行間で HDL Cosimulation ブロックの Timescales ペイン設定を変更する場合は、HDL シミュレーターでシミュレーションを再開する必要があります。

HDL ティックの整数として表現できない Simulink サンプル時間を指定すると、エラーが発生します。

非整数期間

非整数の時間期間を使用する場合、HDL シミュレーターはそのような無限に繰り返される値を表すことができません。したがって、シミュレーターは期間を切り捨てますが、Simulink が値を切り捨てる方法とは異なる方法で切り捨てるため、2 つの期間が一致しなくなります。

次の例は、次のシナリオでタイミング関係を設定する方法を示しています。Simulink で のサンプル期間を使用します。これは、整数以外の時間期間に相当します。

ここで重要な考え方は、Simulink 時間を HDL ティックに常に関連付けることができなければならないということです。HDL ティックは、HDL シミュレータが認識する最も細かいタイム スライスです。ModelSim の場合、デフォルトのティックは 1 ns ですが、1 fs まで精度を上げることができます。

ただし、3 Hz 信号の実際の周期は 333.33333333333... ms であり、これは HDL シミュレータの有効なティック周期ではありません。HDL シミュレーターはそのような数値を切り捨てます。しかし、Simulink は同じ決定を下しません。したがって、2 つの独立したシミュレーターを同期させようとするコシミュレーションでは、何も想定しないでください。代わりに、数値を切り捨てるか四捨五入するかを決める必要があります。

したがって、解決策は、Simulink サンプル時間または HDL サンプル時間 (タイムスケール経由) のいずれかを有効な数値に「スナップ」することです。可能性は無限にありますが、スナップを実行する方法はいくつかあります。

Simulink サンプル時間を 1/3 秒から 0.33333 秒に変更し、コシミュレーション ブロックのタイムスケールを「Simulink の 1 秒 = HDL シミュレータの 1 秒」に設定します。HDL Cosimulation ブロック Clocks ペインでクロックを指定する場合、その周期は 0.33333 秒にする必要があります。

HDL シミュレーターで、Simulink のサンプル時間を 1/3 秒、Simulink のサンプル時間を 1 秒 = 6 ティックに保ちます。

HDL Cosimulation ブロック Clocks ペインでクロックを指定する場合、その周期は 1/3 にする必要があります。簡単に言えば、この仕様は、HDL の時間解像度に関係なく、Simulink に各 Simulink サンプル時間を (1/3*6) = 2 ティックごとに対応させるように指示します。

デフォルトの HDL シミュレータの解像度が 1 ns の場合、HDL のサンプル時間は 2 ns ごとになります。このサンプル時間は、Simulink サンプル時間ごとに、対応する HDL サンプル時間が存在するように機能します。

ただし、Simulink は 1/3 秒周期で考え、HDL は 2 ns 周期で考えます。そのため、デバッグ中に混乱する可能性があります。これを実際の周期(たとえば 5 桁、つまり 333.33 ミリ秒)に一致させたい場合は、次のオプションに従ってください。

HDL シミュレーターで、Simulink サンプル時間を 1/3 秒、Simulink = 0.99999e9 ティックで 1 秒に保ちます。HDL Cosimulation ブロック Clocks ペインでクロックを指定する場合、その周期は 1/3 にする必要があります。

HDL Cosimulation ブロックポートのサンプル時間の設定

一般に、Simulink は HDL Cosimulation ブロックのポートのサンプル時間を次のように処理します。

入力ポートが、順方向伝播に基づいて明示的なサンプル時間を持つ信号に接続されている場合、Simulink はそのレートをその入力ポートに適用します。

入力ポートが明示的なサンプル時間を持たない信号に接続されている場合、Simulink は、モデルのすべての識別された入力ポートのサンプル時間の最小公倍数 (LCM) に等しいサンプル時間を割り当てます。

Simulink は入力ポートのサンプル期間を設定した後、ユーザーが指定した出力サンプル時間をすべての出力ポートに適用します。すべての出力ポートに対してサンプル時間を明示的に定義する必要があります。

相対タイミング モードでコシミュレーション用のモデルを開発する場合は、次のサンプル時間ガイドラインを考慮してください。

HDL Cosimulation ブロックの出力サンプル時間を、HDL シミュレータで定義された解像度制限の整数倍として指定します。ロードされたモデルの解像度制限を確認するには、HDL シミュレータ コマンド report simulator state を使用します。HDL シミュレータの解像度制限が 1 ns で、ブロックの出力サンプル時間を 20 に指定すると、Simulink は 20 ns ごとに HDL シミュレータと対話します。 |