このページは機械翻訳を使用して翻訳されました。元の英語を参照するには、ここをクリックします。

HDL Verifier 入門

HDL Verifier™ を使用すると、システム レベルの設計環境を HDL 設計環境で再利用できます。MATLAB® および Simulink® のゴールデン リファレンス モデルに対して RTL 設計をテストおよび検証し、シミュレータまたはハードウェアで設計をデバッグし、テストベンチと検証用 IP を生成できます。

HDL Verifier を使用すると、HDL シミュレータで実行される RTL デザインと MATLAB および Simulink で実行されるテストベンチを使用して、FPGA、ASIC、および SoC デザインを検証できます。これらのテストベンチを AMD®、Altera®、および Microchip FPGA 開発ボードで再利用して、ハードウェア実装を検証し、内部信号をプローブして設計をデバッグすることができます。また、MATLAB および Simulink から Universal Verification Methodology (UVM) コンポーネントを生成し、 SystemVerilog 検証環境で使用することもできます。これらの機能はすべて、既存の HDL コードおよび HDL Coder™ によって生成されたコードと互換性があります。

チュートリアル

- MATLAB Test ベンチで HDL モジュールを検証する

このチュートリアルでは、MATLAB® を使用して単純な HDL 設計を検証する HDL Verifier™ アプリケーションをセットアップするための基本的な手順について説明します。 - Simulink テストベンチで HDL モジュールを検証する

Simulink を使用して単純な VHDL® モデルを検証する HDL Verifier セッションを設定します。 - MATLAB システムオブジェクトのコシミュレーション Wizard を使い始める

HDL Verifier ™ を使用すると、MATLAB ® または Simulink ® と HDL シミュレータ間のコシミュレーションを設定できます。 - Simulink を使用してレイズド コサイン フィルタ設計を検証する

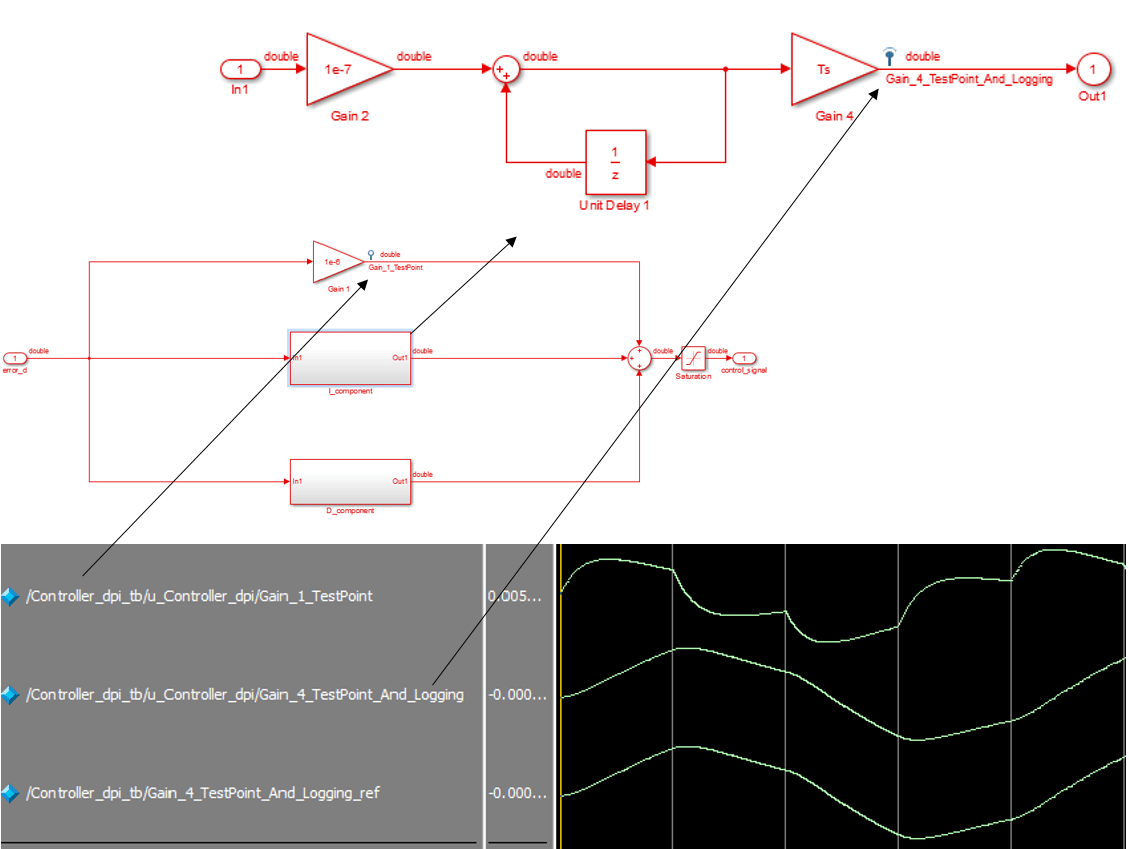

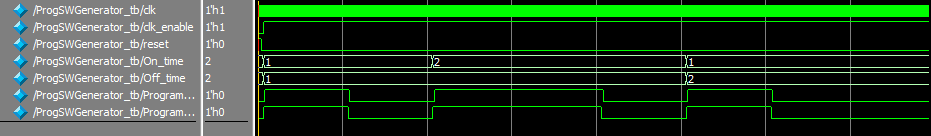

コシミュレーション ウィザードを使用してコシミュレーション用の Simulink モデルを作成する方法について説明します。 - FPGA インザループを使用した PID コントローラーの HDL 実装の検証

この例では、HDL Verifier™ を使用して FPGA インザループ(FIL) アプリケーションを設定する方法を示します。 - 生成された HDL コードのテスト ベンチの選択 (HDL Coder)

生成されたテスト ベンチを選択します。 - HDL ワークフロー アドバイザーを使用したテスト ベンチの生成とコード カバレッジの有効化 (HDL Coder)

HDL ワークフロー アドバイザーを使用して生成された HDL コード用にテスト ベンチとコード カバレッジを生成します。

HDL コシミュレーション

HDLコードのインポート

FPGA インザループ (FIL)

生成された HDL コードを HDL ワークフロー アドバイザーで検証する (HDL Coder ライセンスが必要)

HDL検証について

- HDL コシミュレーション

HDL Verifier ソフトウェアは、MATLAB 関数、MATLAB System object™、および Simulink ブロックのライブラリで構成されており、これらはすべて HDL シミュレータと MATLAB または Simulink 間の通信リンクを確立します。

- FPGA検証

HDL Verifier は、Simulink または MATLAB および HDL Coder と連携し、サポートされている FPGA 開発環境を使用して、自動的に生成された HDL コードを FPGA に実装できるように準備します。

- FPGA Debug

HDL Verifier provides FPGA data capture and AXI manager features for debugging and testing implementations on FPGA or SoC device from MATLAB or Simulink.

- TLM コンポーネント生成

HDL Verifier を使用すると、商用仮想プラットフォームを含む、あらゆる OSCI 互換 TLM 2.0 環境で実行できる SystemC トランザクション レベル モデル (TLM) を作成できます。

- SystemVerilog DPI コンポーネントの生成

HDL Verifier は Simulink Coder™ または MATLAB Coder と連携して、サブシステムをダイレクト プログラミング インターフェイス (DPI) を備えたSystemVerilogコンポーネント内に生成された C コードとしてエクスポートします。

注目の例

ビデオ

HDL Verifier の概要

HDL Verifier を使用して、FPGA、ASIC、SoC の Verilog® および VHDL 設計をテストおよび検証します。HDL シミュレータとのコシミュレーションを使用して、MATLAB または Simulink で実行されるテストベンチで RTL を検証します。同じテストベンチを FPGA および SoC 開発ボードで使用して、ハードウェアでの HDL 実装を検証します。