このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

コシミュレーションを使用した HDL と Simulink のコード カバレッジの比較

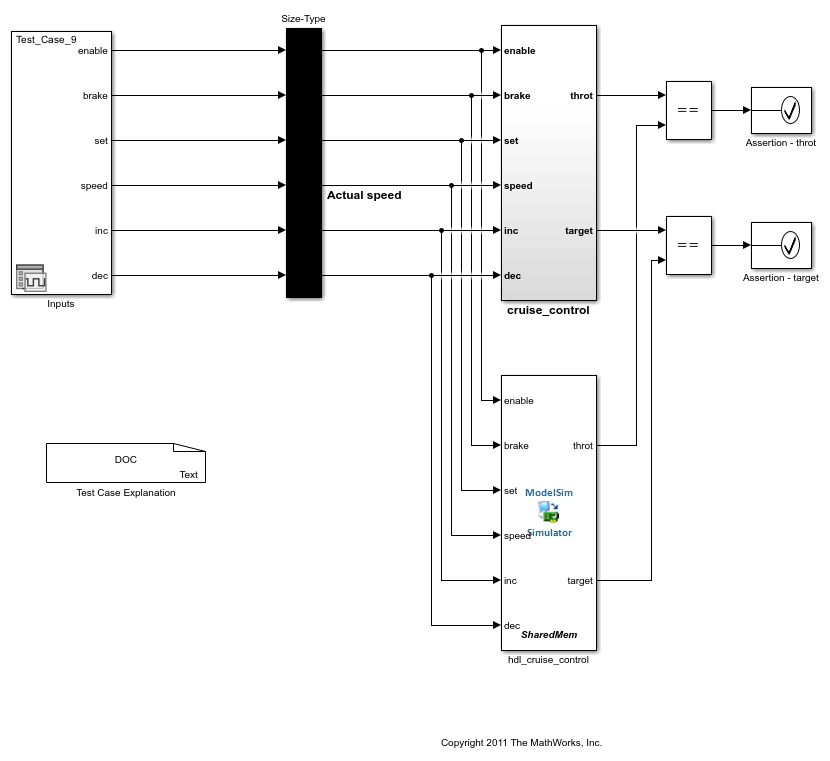

この例では、Simulink ® と HDL シミュレータを使用して、HDL クルーズ コントローラー設計の完全なコード カバレッジを実現する方法を示します。

はじめに

このモデルに関連付けられた HDL コードは、クルーズ コントローラーの Simulink 動作モデルから HDL Coder ™ を介して生成されます。HDL コシミュレーション ブロックの出力を元の動作ブロックの出力と比較することで、HDL コードの正確性を検証するためのテストベンチ モデルが提供されます。テストベンチ モデル内のテストケースは、完全なモデル カバレッジを実現するために、元の動作モデルから Simulink Design Verifier ™ を通じて生成されます。この例では、自動的に生成されたテストケースでも完全な HDL コード カバレッジが達成されることがわかります。この例を実行するために Simulink Design Verifier をインストールする必要はありません。

Simulinkモデルを開く

ModelSim または QuestaSim を使用している場合は、モデル cruise_control_modelsim.slx が開いている必要があります。Xcelium を使用している場合は、ModelSim モデルを閉じて、モデル cruise_control_incisive.slx を開きます。

コード カバレッジ機能は ModelSim PE のオプション機能であることに注意してください。この例を実行するには、ModelSim のバージョンに適切なコード カバレッジ ライセンスがあることを確認してください。

% For ModelSim: modelName = 'cruise_control_modelsim'; open_system(modelName);

% For Xcelium: modelName = 'cruise_control_incisive'; open_system(modelName);

HDL シミュレーションでのクロック、リセット、クロック イネーブルの設定

クロック、リセット、およびクロック イネーブル信号は、Simulink シミュレーションの一部ではありません。コシミュレーション ブロック マスクの [シミュレーション] タブにある [事前シミュレーション Tcl コマンド] を使用して、それらのドライバーを定義します。また、入力データ値と出力データ値が交換される前に HDL がリセットから正常に抜け出すように、「コシミュレーションの開始前に HDL シミュレータを実行する時間」も設定します。

ModelSimの場合:

Xcelium の場合:

HDL での結果の波形:

Tcl の force コマンドは、制御信号の波形を生成するために使用されます。

クロック周期は10ns

クロック イネーブル信号は 37 ns でアクティブになります。

リセット信号は 0 ~ 27 ns でアサートされます。

HDL 信号は HDL クロックの立ち上がりエッジで値を変更するため、競合状態を回避するには、コシミュレーションの開始時間を HDL クロックの立ち下がりエッジに合わせる必要があります。したがって、このパラメーターの値は 10 ns クロック周期の整数倍である必要があります。

また、リセット後も HDL デザインを実行しますが、clk_enable によって有効になる最初のアクティブ クロック エッジの前で停止します。これは、シミュレーションの開始直後に内部状態を更新する動作ブロックと一致するようにするためです。

上記の考慮事項に基づいて、「コシミュレーションを開始する前に HDL シミュレータを実行する時間」オプションは 40 ns に設定されています。各テストケースを実行すると、最初に HDL シミュレータに「事前シミュレーション Tcl コマンド」が適用されます。次に、HDL シミュレーターは、コシミュレーションが開始する前に、リセット、クロック、および clk_enable 信号を適用するために時間を 40 ns 進めます。

コシミュレーション用のHDLシミュレータを起動

Modelsimの場合:

% Commands to compile and invoke Modelsim with code coverage enabled. tclCmds = { 'vlib work',... % Create ModelSim library 'vcom +cover cruise_hdlsrc/PI_Controller.vhd',... % Compile VHDL code with code coverage enabled 'vcom +cover cruise_hdlsrc/Controller.vhd',... % Compile VHDL code with code coverage enabled 'vsimulink -coverage work.Controller',... % Load simulation 'puts "Ready for cosimulation..."',... }; % Now we launch the HDL simulator and wait for it to be ready. vsim('tclstart',tclCmds); disp('Waiting for HDL simulator to start ...'); processid = pingHdlSim(240); disp('HDL simulator is ready to cosimulate.');

Xcelium の場合:

% Commands to compile and invoke Xcelium with code coverage enabled. tclCmds = { 'exec xmvhdl -64bit -v93 cruise_hdlsrc/PI_Controller.vhd',... % Compile VHDL code 'exec xmvhdl -64bit -v93 cruise_hdlsrc/Controller.vhd',... % Compile VHDL code 'exec xmelab -64bit -coverage all -vhdl_time_precision 1ns -access +wc Controller',... % Elaborate design with coverage enabled 'hdlsimulink -covoverwrite Controller',... % Load simulation 'puts "Ready for cosimulation..."',... }; % Now we launch the HDL simulator and wait for it to be ready. nclaunch('tclstart',tclCmds,'runmode','CLI'); disp('Waiting for HDL simulator to start ...'); processid = pingHdlSim(240); disp('HDL simulator is ready to cosimulate.');

シミュレーションを実行

テストベンチ モデルには 9 つのテストケースがあります。この例では、すべてのテストケースでこのモデルを実行し、コード カバレッジの結果を生成します。各コシミュレーション セッションが終了した後、各シミュレーションの開始時に HDL 信号が適切にリセットされるため、HDL シミュレーターを再起動する必要はありません。各シミュレーションの後には、HDL シミュレータが次の反復の前にカバレッジ結果を更新するための時間を確保するために、短い一時停止が追加されます。

% Run the cosimulation for k = 1:9 get_param([modelName '/Inputs'],'ActiveScenario'); % get ActiveScenario parameter for changing test scenarios set_param([modelName '/Inputs'],'ActiveScenario',['Test_Case_' num2str(k)]) % set a Test case sim(modelName); % Run simulation pause(5); % pause for writing coverage to database end

コードカバレッジの結果を観察する

HDL シミュレーターは、すべてのテストケースを反復処理するにつれてカバレッジを蓄積します。シミュレーションが終了すると、100% のコード カバレッジが達成されます。

ModelSimの場合:カバレッジの結果は、UI の「カバレッジ」タブで確認できます。

Xcelium の場合:カバレッジ結果をダンプし、「imc」ツールを使用して結果を視覚化します。

% Dump and visualize the coverage results tclHdlSim('coverage -dump test'); system('imc -gui -load test &');