このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA インザループを使用した PID コントローラーの HDL 実装の検証

この例では、HDL Verifier™ を使用して FPGA インザループ(FIL) アプリケーションを設定する方法を示します。

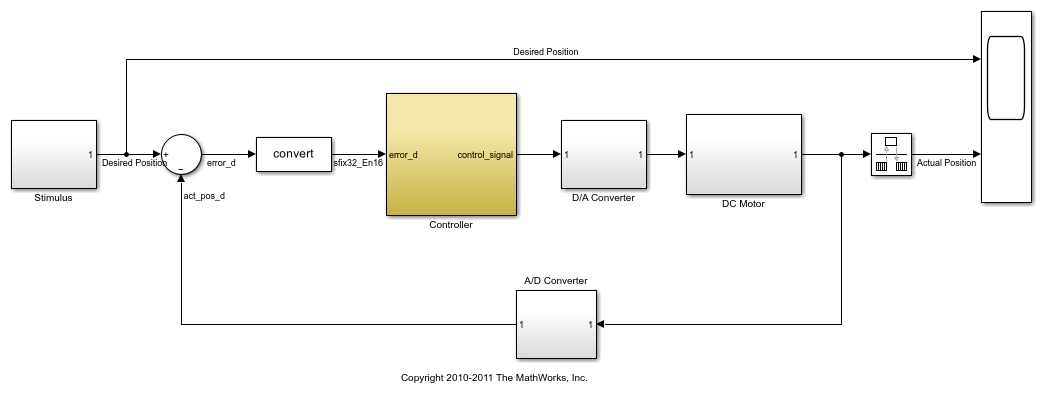

このアプリケーションは、Simulink ® と FPGA 開発ボードを使用して、比例積分微分 (PID) コントローラーの HDL 実装を検証します。この例では、Simulink はモーターの目的の位置を生成し、この PID コントローラーによって制御されるモーターをシミュレートします。

要件と前提条件

リストされている MathWorks 製品以外に、次のような要件があります。

FPGA検証要件 にリストされているサポートされているバージョンの FPGA 設計ソフトウェア (AMD® ISE® 設計スイート、AMD Vivado® 設計スイート、Intel® Quartus® II 設計ソフトウェア、または Microchip Libero® SoC 設計ソフトウェア)。

サポートされている FPGA 開発ボードの 1 つ。サポートされているハードウェアについては、FPGA検証でサポートされているFPGAデバイス を参照してください。

イーサネットを使用した接続の場合:ホスト コンピュータにインストールされたギガビット イーサネット アダプター、ギガビット イーサネット クロスオーバー ケーブル。

JTAGを使用した接続の場合:Intel FPGA ボード用の USB Blaster I または II ケーブルとドライバー。AMD FPGA ボード用の Digilent® JTAG ケーブルとドライバー。

PCI Expressを使用した接続の場合:ホスト コンピュータのPCI Expressスロットにインストールされた FPGA ボード。

必要条件:

MATLAB ® および FPGA 設計ソフトウェアは、コンピューターにローカルにインストールすることも、ネットワークにアクセス可能なデバイスにインストールすることもできます。ネットワークからソフトウェアを使用する場合は、FPGA 開発ボードにプライベート ネットワークを提供するために、コンピューターに 2 番目のネットワーク アダプターをインストールする必要があります。ネットワーク アダプターのインストール方法については、コンピューターのハードウェアおよびネットワーク ガイドを参照してください。

FPGA開発ボードのセットアップ

シミュレーションにPCI Express接続を使用している場合は、この手順と手順 2 をスキップしてください。PCI Express接続をまだ設定していない場合は、サポート パッケージ インストール ソフトウェアを使用して、 PCI Express のセットアップをガイドします。

FPGA 開発ボードをセットアップするには、次の手順に従います。

電源スイッチが OFF のままになっていることを確認してください。

AC 電源コードを電源プラグに接続します。電源アダプタ ケーブルを FPGA 開発ボードに差し込みます。

クロスオーバー イーサネット ケーブルを使用して、FPGA 開発ボード上のイーサネット コネクタをコンピューターのイーサネット アダプタに直接接続します。

JTAG ダウンロード ケーブルを使用して、FPGA 開発ボードをコンピューターに接続します。

特別な設定が必要な Microchip PolarFire を除き、FPGA 開発ボード上のすべてのジャンパーが工場出荷時のデフォルト位置にあることを確認します。Microchip Polarfire 評価キットのインストールを参照してください。

ホストコンピュータとボードの接続を設定する

シミュレーションに JTAG 接続を使用している場合は、この手順をスキップしてください。イーサネットに接続するには、この例を実行するために、コンピューターにギガビット イーサネット ネットワーク アダプターが搭載されている必要があります。

Windows® の場合は、次の手順を実行します。

コントロール パネルを開きます。

検索バーに「ネットワーク接続の表示」と入力します。検索結果から ネットワーク接続の表示 を選択します。

FPGA 開発ボードへの接続アイコンを右クリックし、ポップアップ メニューから [プロパティ] を選択します。

この接続は次の項目を使用しますの下で、インターネット プロトコル バージョン 4 (TCP/IPv4)を選択し、プロパティをクリックします。

次の IP アドレスを使用する: を選択します。IP アドレス を 192.168.0.1 に設定します。このアドレスがネットワーク上の別のコンピューターで使用されている場合は、このサブネット上の使用可能な IP アドレス (192.168.0.100 など) に変更します。これはホスト コンピュータのアドレスです。サブネット マスク を 255.255.255.0 に設定します。TCP/IP プロパティは次の図のようになるはずです。

Linux®の場合:

ifconfig コマンドを使用してローカル アドレスを設定します。以下に例を示します。

% ifconfig eth1 192.168.0.1

この例では、eth1 は Linux コンピュータ上の 2 番目のイーサネット アダプタです。システムをチェックして、どのイーサネット アダプタが FPGA 開発ボードに接続されているかを確認します。上記のコマンドは、ローカル IP アドレスを 192.168.0.1 に設定します。このアドレスがネットワーク上の別のコンピューターで使用されている場合は、このサブネット上の使用可能な IP アドレス (192.168.0.100 など) に変更します。

サンプルリソースを準備する

1. FPGA設計ソフトウェアのセットアップ

FPGA インザループを使用する前に、FPGA 設計ソフトウェアにアクセスするためのシステム環境を設定します。関数 hdlsetuptoolpath を使用して、ISE、Vivado、Quartus、または Libero SoC 設計ソフトウェアを現在の MATLAB セッションのシステム パスに追加できます。サポートされている FPGA 設計ソフトウェアのバージョンについては、FPGA検証要件 を参照してください。各ツールのコマンドラインの例を以下に示します。異なる場合は、実際の実行可能ファイルに置き換えてください。

ISE 設計ソフトウェアを使用する AMD FPGA ボードの場合は、次を実行します。

hdlsetuptoolpath('ToolName','Xilinx ISE','ToolPath','C:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\ise.exe');

Vivado 設計ソフトウェアを使用する AMD FPGA ボードの場合は、次を実行します。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2023.1\bin\vivado.bat');

Intel ボードの場合は、次を実行します。

hdlsetuptoolpath('ToolName','Altera Quartus II','ToolPath','C:\altera\22.1.1\quartus\bin\quartus.exe');

Microchip ボードの場合は、次を実行します。

hdlsetuptoolpath('ToolName','Microchip Libero SoC','ToolPath','C:\Microsemi\Libero_SoC_v23.2\Designer\bin\libero.exe');

2. fil_pid モデルを開きます。

このモデルには、基本的な Simulink ブロックで実装された固定小数点 PID コントローラーが含まれています。このモデルには、この PID コントローラによって制御される DC モーター モデルと、入力刺激としての目的の DC モーターの位置も含まれています。

今すぐこのモデルを実行し、スコープ内で目的のモーターの位置と実際のモーターの位置を観察します。

FPGAインザループ(FIL)ウィザードを起動する

FPGA インザループ ウィザードを起動するには、Simulink ツールストリップの アプリ タブを選択し、HDL Verifier をクリックします。このアクション、HDL Verifier タブが Simulink ツールストリップに追加されます。次に、HDL Verifier モード セクションで、FPGA-in-the-loop を選択します。FIL ブロックの生成 セクションで HDL ファイルのインポート をクリックします。

あるいは、MATLAB コマンド プロンプトで filWizard コマンドを入力することもできます。

filWizard

FILウィザードでハードウェアオプションを指定する

FPGA 開発ボードの FIL オプションを設定します。

1. ウィザードが FIL Simulink ブロックを生成するか、FILSimulation MATLAB システム オブジェクトを生成するかを指定します。この例では、FIL シミュレーション Simulink に Simulink を選択します。

2. ボード名では、ホストコンピューターに接続されている FPGA 開発ボードを選択します。ボードがリストにない場合は、次のいずれかのオプションを選択します。

「さらにボードを入手...」をクリックして、FPGA ボード サポート パッケージをダウンロードします (このオプションを選択すると、サポート パッケージ インストーラーが起動します)。

「カスタム ボードの作成...」を選択すると、特定の FPGA ボード用の FPGA ボード定義ファイルが作成されます (このオプションを選択すると、新しい FPGA ボード マネージャーが起動します)。

3. シミュレーションする接続を選択します。使用可能な接続方法は、イーサネットと JTAG です。すべてのボードが両方の接続方法をサポートしているわけではありません。

4. イーサネット接続のみ:ネットワーク アダプターのセットアップ時にコンピューターの IP アドレスを 192.168.0.x 以外のサブネットに変更した場合、またはデフォルトのボード IP アドレス 192.168.0.2 が別のデバイスで使用されている場合は、[詳細オプション] を展開し、次のガイドラインに従って [ボードの IP アドレス] を変更します。

サブネット アドレスは、通常、ボードの IP アドレスの最初の 3 バイトですが、これがホスト IP アドレスのものと一致していなければなりません。

ボードの IP アドレスの最終バイトは、ホスト IP アドレスの最終バイトと異なっていなければなりません。

ボードの IP アドレスは、他のコンピューターの IP アドレスと競合しないものを使用しなければなりません。

たとえば、ホスト IP アドレスが 192.168.8.2 の場合、192.168.8.3 が使用可能であればそれを使用できます。ボードの MAC アドレス を変更しないでください。

FPGA 上の BRAM を使用して Ethernet パケットをバッファリングするには、FPGA でのデータ バッファリングを有効にする を選択します。

5. オプション:DUT クロック周波数をデフォルト (25 MHz) から変更する場合は、詳細オプション を展開し、FPGA システム クロック周波数 (MHz) を変更できます。

6. 続行するには、次へ をクリックします。

FILウィザードでHDLファイルを指定する

FPGA に実装する HDL 設計を指定します。

1. [追加] をクリックし、「サンプル リソースの準備」で作成したディレクトリを参照します。

2. pid_hdlsrc ディレクトリで次の HDL ファイルを選択します。

コントローラー.vhd

D_コンポーネント.vhd

I_コンポーネント.vhd

これらは、FPGA ボード上で検証される HDL 設計ファイルです。

3. ソース ファイル テーブルで、ファイル Controller.vhd の行のチェック ボックスをオンにして、この HDL ファイルに最上位レベルの HDL モジュールが含まれていることを指定します。

FIL ウィザードは、選択した HDL ファイルの名前 (この場合は Controller) を Top-level module name フィールドに自動的に入力します。この例では、最上位モジュール名はファイル名と一致するため、変更する必要はありません。トップレベル モジュール名とファイル名が一致しない場合は、このダイアログでトップレベル モジュール名を手動で修正します。

続行するには、次へ をクリックします。

FILウィザードでI/Oポートを確認する

FIL ウィザードは、Controller.vhd 内の最上位 HDL モジュール コントローラーを解析してすべての I/O ポートを取得し、それらを DUT I/O ポート テーブルに表示します。パーサーは、ポート名を確認して可能なポート タイプを自動的に判別し、これらの信号を [ポート タイプ] の下に表示します。

1. ポートのリストを確認します。パーサーが特定のポートに対して誤ったポート タイプを割り当てた場合は、手動で信号を変更できます。同期設計の場合は、クロック、リセット、またはクロック イネーブル信号を指定します。この例では、FIL ウィザードが自動的にテーブルを正しく入力します。

2. 続行するには、次へ をクリックします。

FILウィザードで出力データ型を設定する

1. HDL 出力 control_signal の Data Type を Fixedpoint に、Sign を Signed に、Fraction Length を 28 に変更します。これにより、生成された FIL ブロックは、FPGA テスト対象デザイン (DUT) の出力信号を正しいデータ型に設定します。

2. 続行するには、次へ をクリックします。

FILウィザードのビルドオプションを確認する

1. 出力ファイルのフォルダーを指定します。この例では、現在のディレクトリの下の Controller_fil という名前のサブフォルダーであるデフォルト オプションを使用します。

概要には、FPGA プロジェクト ファイルと FPGA プログラミング ファイルの場所が表示されます。高度な操作にはこれら 2 つのファイルが必要になる場合があります。

2. ビルド プロセスを開始するには、ビルド をクリックします。

ビルド プロセス中に、次のアクションが実行されます。

次の図に示すように、Controller という名前の FIL ブロックが生成され、モデルに挿入されます。

モデル生成後、FIL ウィザードはコマンド ウィンドウを開き、FPGA 設計ソフトウェアが合成、フィット、配置配線、タイミング解析、および FPGA プログラミング ファイルの生成を実行します。

FPGA 設計ソフトウェア プロセスが終了すると、コマンド ライン ウィンドウに、ウィンドウを閉じてもよいことを知らせるメッセージが表示されます。ウィンドウを閉じて次の手順に進みます。

モデルの設定

fil_pid モデルで、Controller サブシステムを新しいモデルで生成された FIL ブロックに置き換えます。変更された fil_pid モデルは次の図のようになります。

FPGAをプログラムする

1. FPGA開発ボードの電源をONに切り替えます。

2. fil_pid モデル内の FIL ブロックをダブルクリックして、ブロック マスクを開きます。

3. 開いたブロック マスクで、読み込みをクリックします。

ボードが JTAG ケーブルを介してホスト コンピューターに正しく接続されている場合は、FPGA プログラミング ファイルが正常にロードされたことを示すメッセージ ウィンドウが表示されます。このダイアログを閉じるには、[OK] をクリックします。

4. イーサネット接続のみ:pingテストを通じて、FPGA ボードがホスト コンピューターに正しく接続されているかどうかをテストできます。コマンドライン ウィンドウを起動し、次のコマンドを入力します。

C:\MyTests> ping 192.168.0.2

ネットワーク アダプターのセットアップ時にボードの IP アドレスを変更した場合は、192.168.0.2 をボードの IP アドレスに置き換えます。ギガビット イーサネット接続が適切に設定されている場合は、FPGA 開発ボードからの ping 応答が表示されます。

FIL ブロックのパラメーターを確認する

1. FIL ブロック マスクで、信号属性 タブをクリックします。

2. HDL 信号 control_signal の データ型 が fixdt(1,32,28) であることを確認します。そうでない場合は変更してください。

3. ブロック マスクを閉じるには、OK をクリックします。

FILを実行する

1. fil_pid モデルのシミュレーションを開始します。

2. シミュレーションが完了したら、スコープでモーターの希望位置と実際の位置の波形を表示します。FIL シミュレーションの結果は、サンプル リソースの準備でシミュレートした Simulink 参照モデルの結果と一致する必要があることに注意してください。