このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

MATLAB システムオブジェクトのコシミュレーション Wizard を使い始める

HDL Verifier ™ を使用すると、MATLAB ® または Simulink ® と HDL シミュレータ間のコシミュレーションを設定できます。コシミュレーション ウィザードは、HDL コードを入力として受け取り、コシミュレーション ブロックまたは System object ™ を出力として生成するグラフィカル ユーザー インターフェイス (GUI) です。System object は MATLAB 内で HDL のコシミュレーションを可能にし、ブロックは Simulink 内で HDL のコシミュレーションを可能にします。

このサンプル デザインは、Verilog® で記述されたサイズ 8 の高速フーリエ変換 (FFT) です。FFT は、信号の周波数分布を生成するためにデジタル信号処理アプリケーションでよく使用されます。

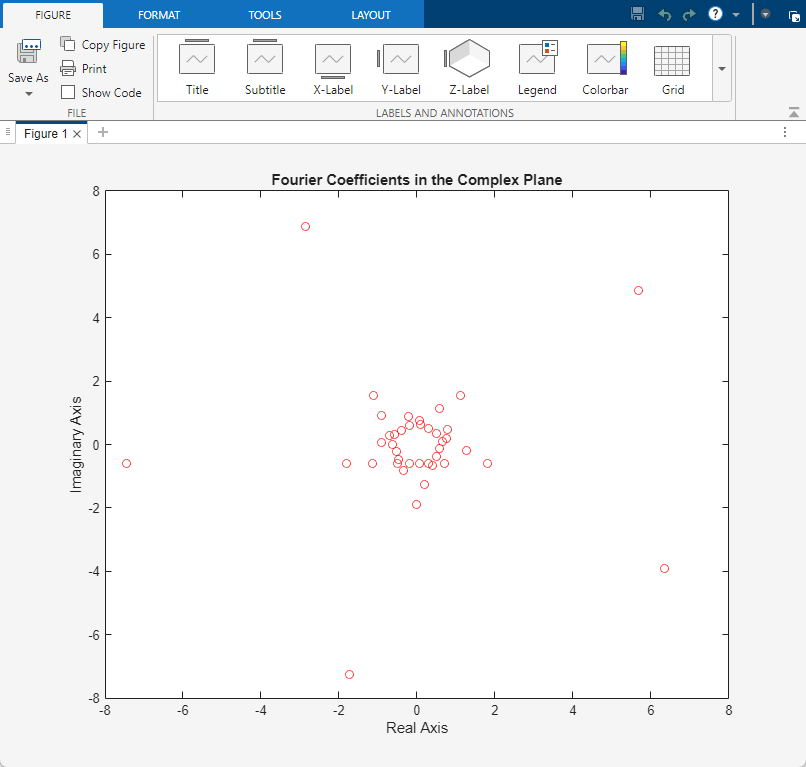

この FFT の正確性を検証するために、MATLAB System object テストベンチが提供されています。このテストベンチは、テスト対象の HDL 設計 (DUT) への周期的な正弦波入力を生成し、複素平面にフーリエ係数をプロットします。

コシミュレーションウィザードは、Verilog ファイルを入力として受け取ります。また、各ステップでコシミュレーションを設定するための HDL コードに関連するその他の入力も収集します。例の最後に、コシミュレーションウィザードは、構成された HDLコシミュレーションSystem object をインスタンス化する MATLAB スクリプト、HDL 設計をコンパイルする MATLAB スクリプト、およびコシミュレーション用の HDL シミュレータを起動する MATLAB スクリプトを生成します。

この例では、MATLAB System object と次の HDL シミュレータのいずれかを使用して、レジスタ転送レベル (RTL) 設計を共同シミュレーションし、検証します。

AMD®のVivado®シミュレータ

Siemens EDA の ModelSim™ または Questa™

Cadence の Xcelium®

Synopsys® の VCS®

1. コシミュレーションウィザードを起動

MATLAB でこのコマンドを実行して、 コシミュレーション Wizard ツールを起動します。

cosimWizard

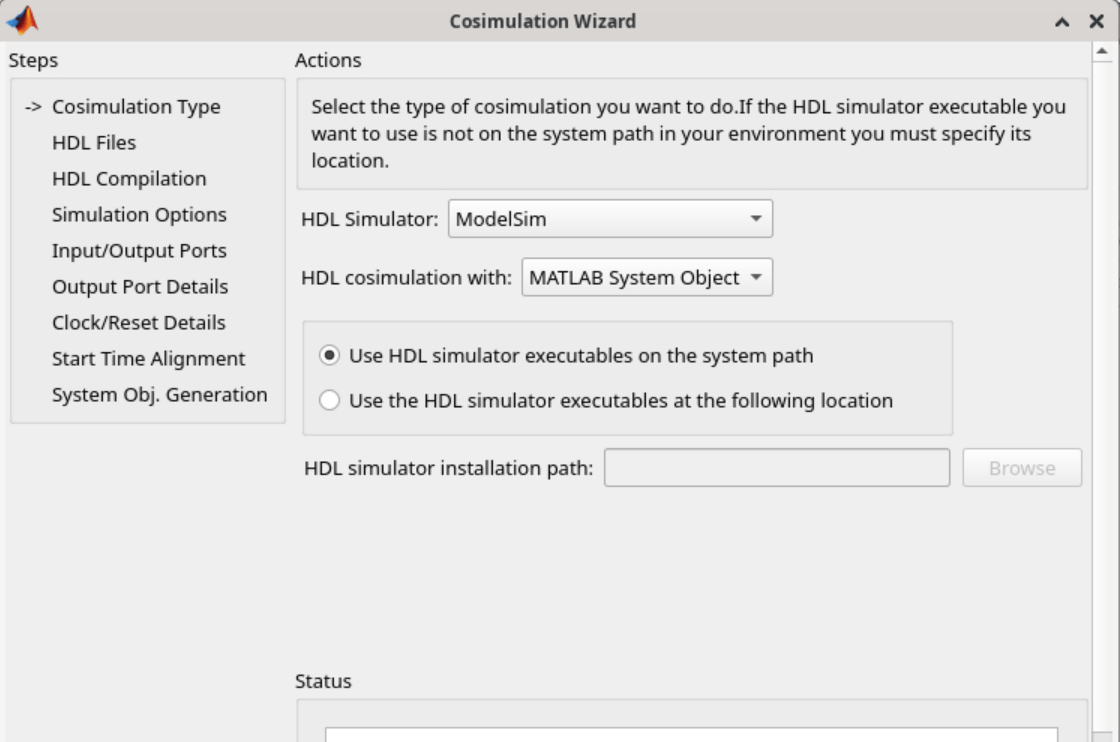

2. コシミュレーションタイプを指定する

「コシミュレーションタイプ」ページで、次の手順を実行します。

a.ModelSim を使用している場合は、HDL シミュレータ を ModelSim に設定します。

Xcelium を使用している場合は、HDL シミュレータ を Xcelium に設定します。

Vivado シミュレータを使用している場合は、HDL シミュレータ を Vivado Simulator に設定します。

VCS を使用している場合は、HDL シミュレータ を Synopsys VCS に設定します。

b.HDLコシミュレーション を MATLAB System Object に設定します。

c.HDL シミュレータ実行ファイルがシステム パス上に表示される場合は、デフォルトの システム パス上の HDL シミュレータ実行ファイルを使用する オプションを変更しないでください。これらの実行ファイルがパス上に表示されない場合は、HDL シミュレータのパスを指定します。

d.[Next] をクリックします。

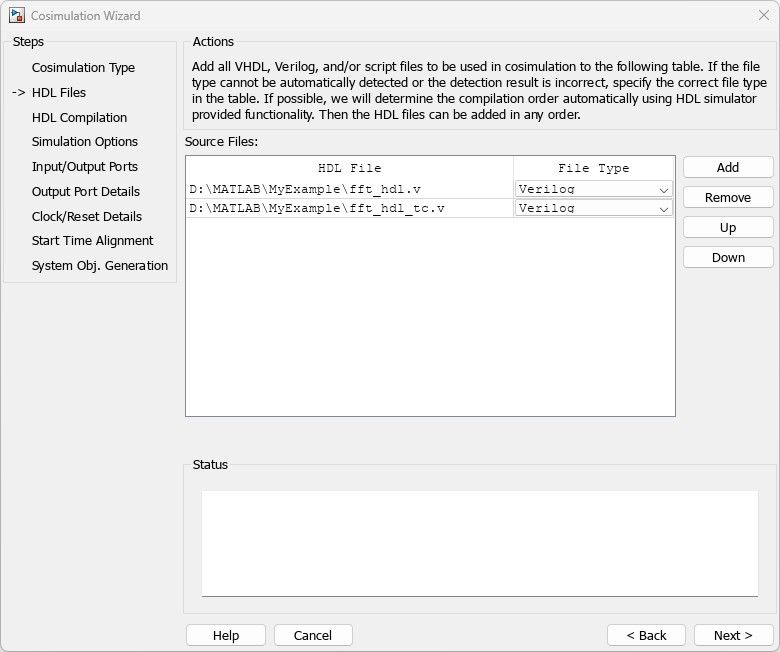

3. HDLファイルを選択

HDL ファイル ページで、次の手順を実行します。

a.ファイル リストに HDL ファイルを追加します。

ModelSim、Xcelium、および Vivado シミュレーターの場合

追加 をクリックし、サンプル フォルダー内の Verilog ファイル fft_hdl.v と fft_hdl_tc.v を選択します。

ファイル リスト内のファイルを確認して、ファイルの種類が正しく識別されていることを確認します。

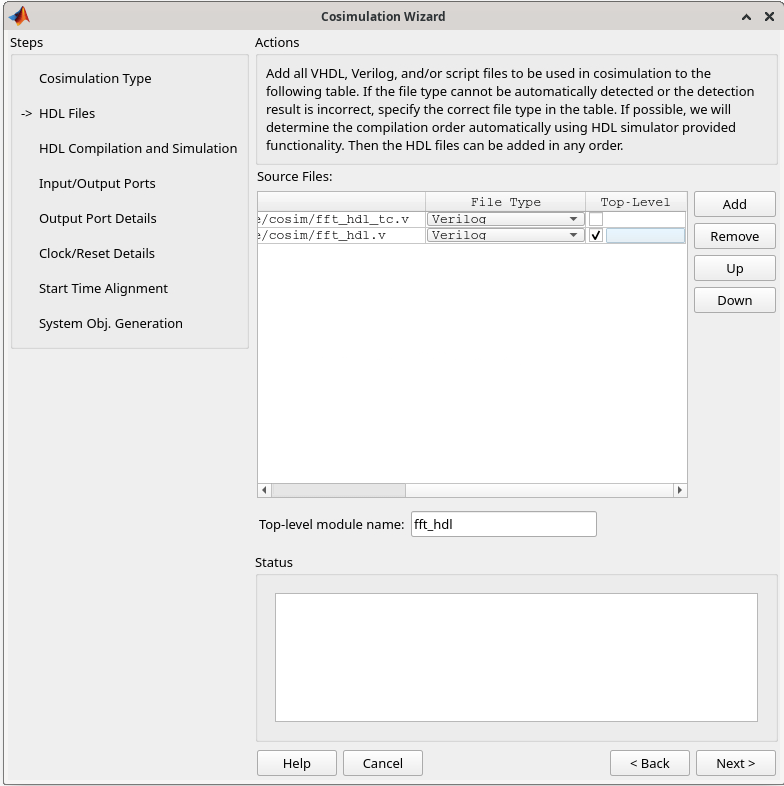

Synopsys VCS の場合

追加 をクリックし、サンプル フォルダー内の Verilog ファイル fft_hdl.v と fft_hdl_tc.v を選択します。

fft_hdl.v を トップレベル モジュールとして選択します。

b.[Next] をクリックします。

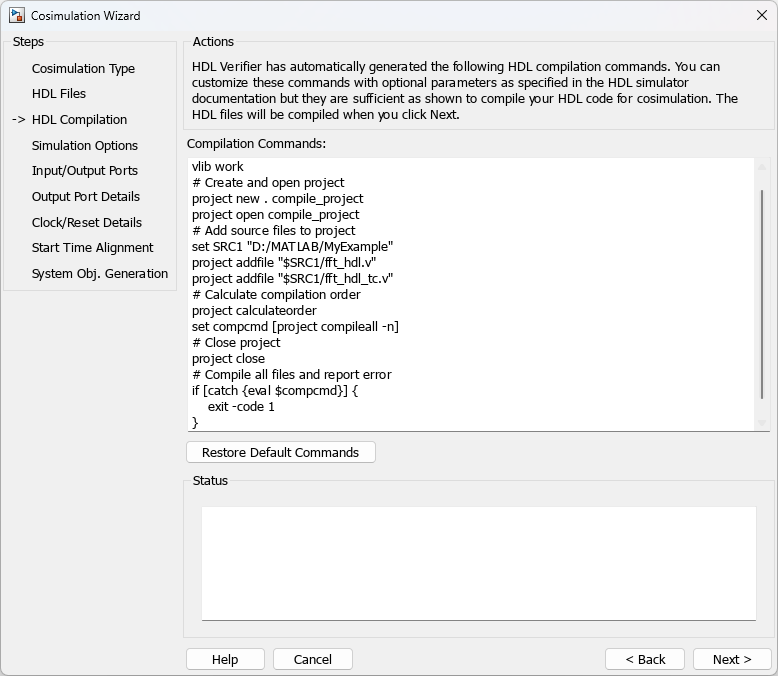

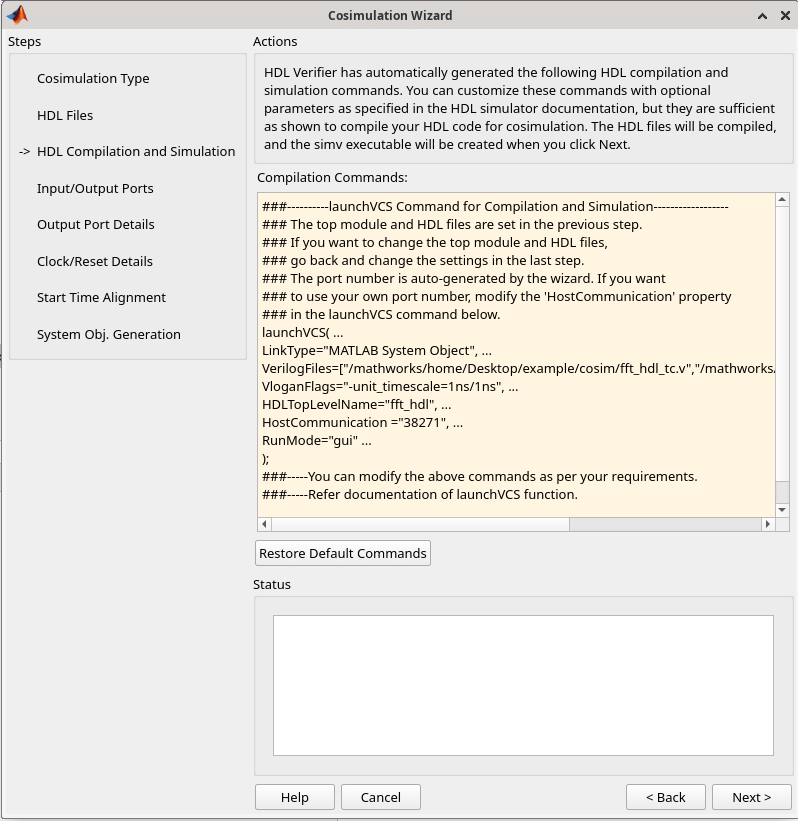

4. HDLコンパイルコマンドを指定する

コシミュレーションウィザードでは、コンパイル コマンド ウィンドウにデフォルトのコマンドが一覧表示されます。この例では、これらのコマンドを変更する必要はありません。

ModelSim のコンパイル コマンドは次のとおりです。

VCS の場合、コンパイルとシミュレーションの手順が結合されます。Synopsys VCS のコンパイルおよびシミュレーション コマンドを以下に示します。

[Next] をクリックします。MATLAB コンソールにコンパイル ログが表示されます。コンパイル中にエラーが発生した場合、そのエラーはステータス領域に表示されます。次の手順に進む前にエラーを修正してください。

5. コシミュレーション用のHDLモジュールを選択する

この手順は Synopsys VCS には適用されません。

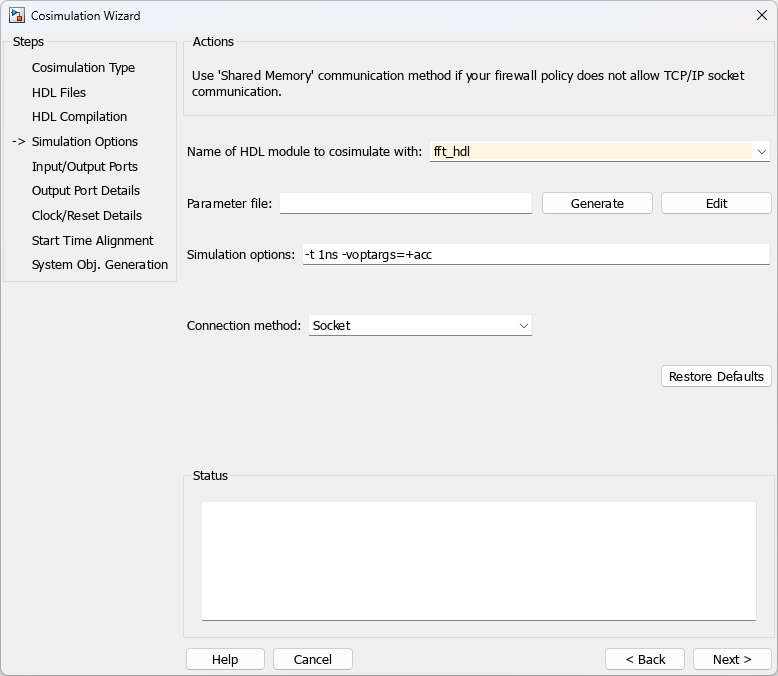

シミュレーション オプション ページで、次の手順を実行します。

a.コシミュレーションの HDL モジュールまたはエンティティの名前を指定します。

ModelSim および Xcelium 向け

リストからfft_hdlを選択します。このモジュールは、コシミュレーションに使用する Verilog モジュールです。リストに fft_hdl が表示されない場合は、ファイル名を手動で入力します。

ModelSim のシミュレーション オプションは次のとおりです。

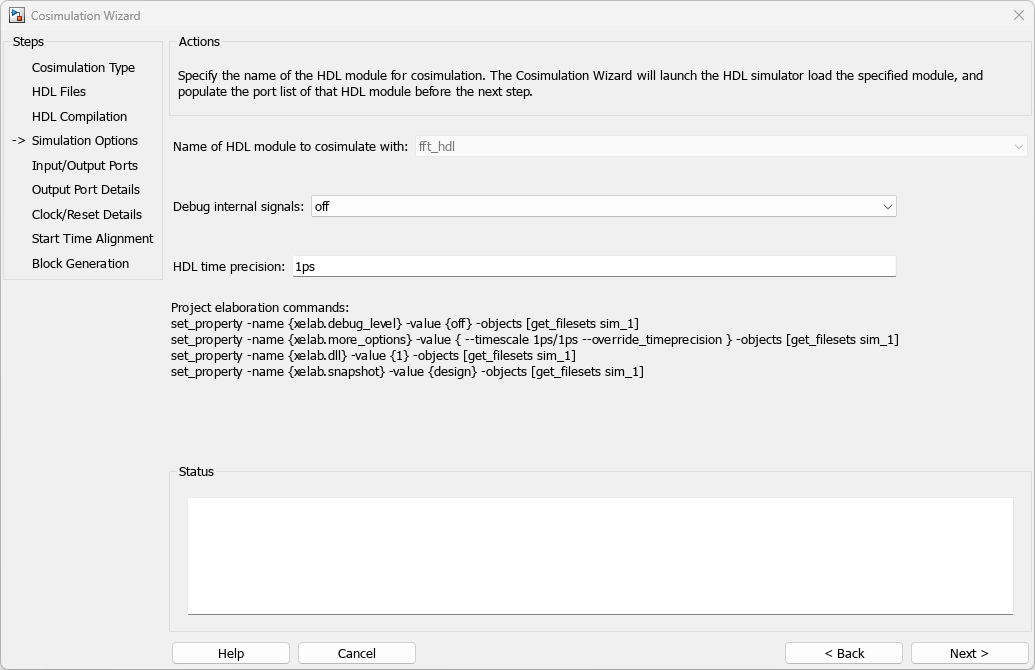

Vivado シミュレータの場合

Vivado シミュレータの場合、Verilog モジュールの名前がデフォルトで選択されます。Vivado シミュレータのシミュレーション オプションは次のとおりです。

b.[Next] をクリックします。コシミュレーションウィザードは、指定された HDL モジュールとシミュレーション オプションを使用して、バックグラウンド コンソールで HDL シミュレーターを起動します。ウィザードが HDL シミュレーターを正常に起動すると、ウィザードは Verilog モデル fft_hdl に入力ポートと出力ポートを設定し、次のステップでそれらを表示します。

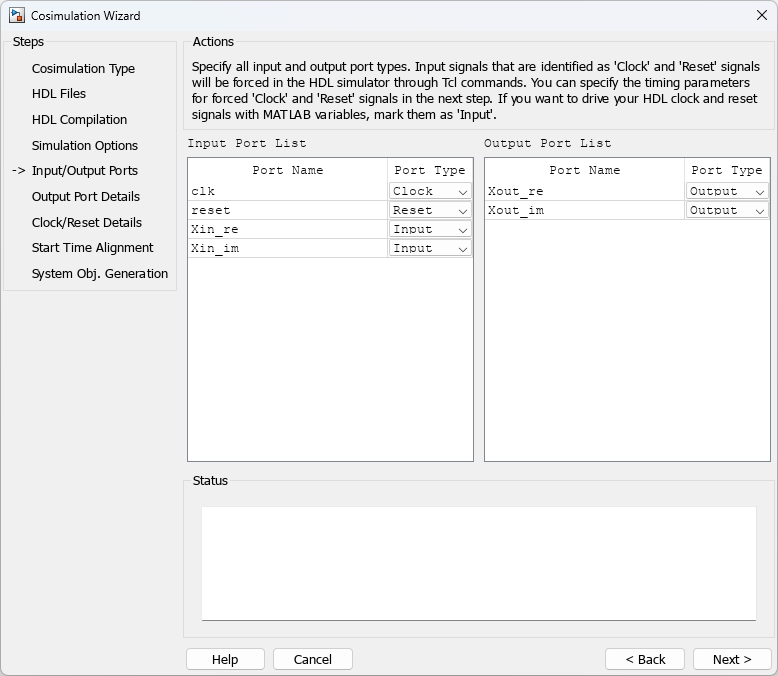

6. 入力/出力ポートの種類を指定する

このステップでは、コシミュレーションウィザードに、それぞれ fft_hdl の入力ポートと出力ポートを含む 2 つのテーブルが表示されます。

コシミュレーションウィザードは、各ポートのポート タイプを正しく識別しようとします。ウィザードがポートを誤って識別した場合は、これらのテーブルを使用してポート タイプを変更できます。

入力ポートには、

Clock、Reset、Input、またはUnusedを選択できます。HDL Verifier は、コシミュレーション中にInputとマークされた入力ポートのみを MATLAB に接続します。HDL Verifier は、コシミュレーション中に

Outputとマークされた出力ポートを MATLAB に接続します。リンク ソフトウェアと MATLAB は、コシミュレーション中にUnusedとマークされた出力ポートを無視します。ClockおよびResetとして識別される信号のパラメーターは、後の手順で変更できます。

この例では、デフォルトのポート タイプを受け入れて、次へ をクリックします。

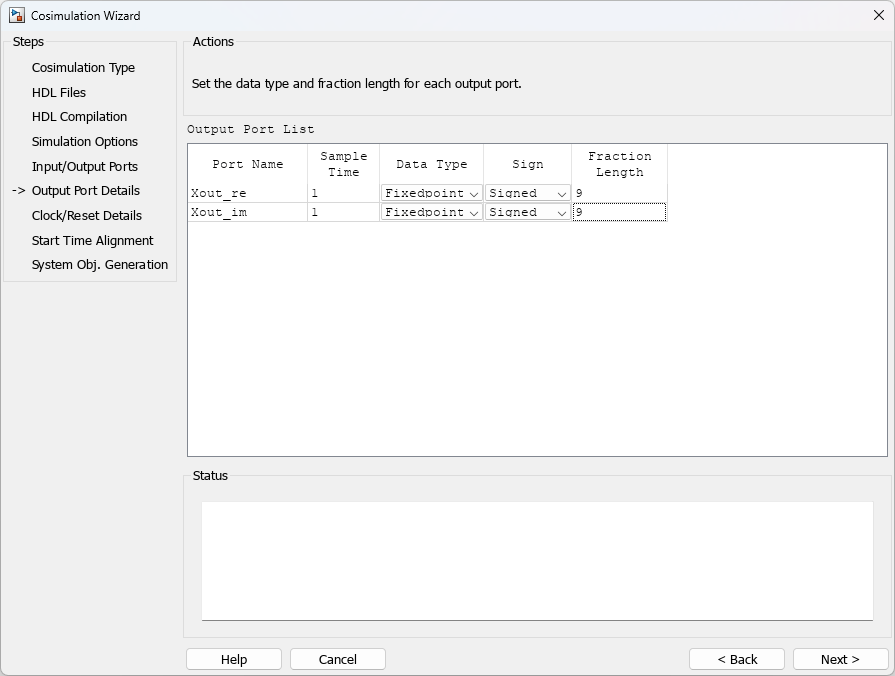

7. 出力ポートの詳細を指定する

この例では、HDL FFT 出力は符号付きで、長さは 13 ビット、小数部の長さは 9 ビットです。出力ポートの詳細ページで、次の手順を実行します。

a.HdlCosimulation System object を使用する場合、サンプル時間 は変更できず、常に 1 に固定されることに注意してください。

b.両方の出力の データ型 を Fixedpoint に設定します。

c.両方の入力の Sign を Signed に設定します。

d.両方の出力の Fraction Length を 9 に設定します。

e.[Next] をクリックします。

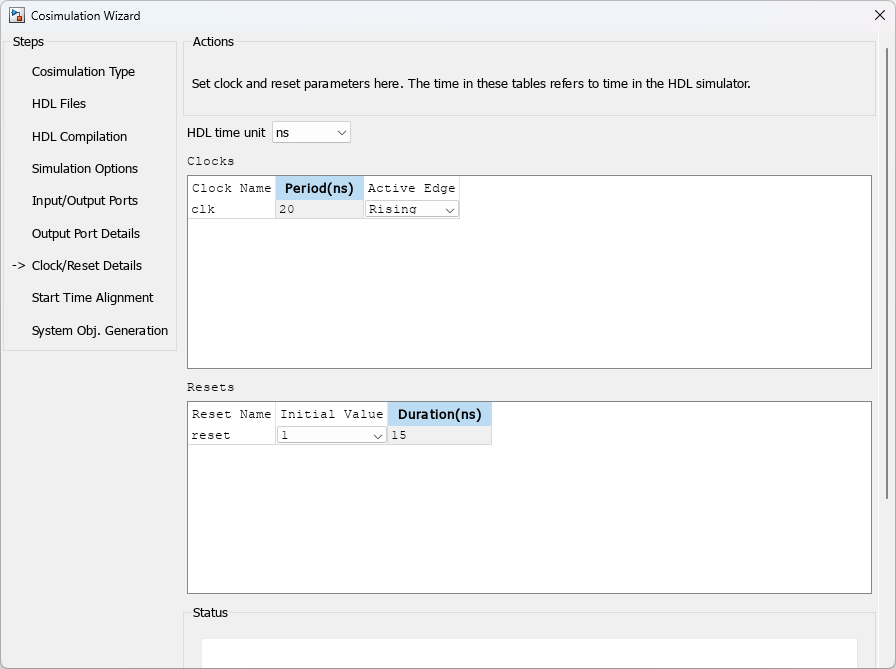

8. クロックの設定と詳細のリセット

クロック周期(ns)を20に設定します。Verilog コードは、リセットが同期しており、アクティブな値が 1 であることを示します。クロックの立ち上がりエッジによってトリガーされ、1 ns の時点で HDL 設計全体をリセットできます。リセット信号には 15 ns の持続時間を使用します。「クロック/リセットの詳細」ページで、次の手順を実行します。

a.クロック周期を 20 に設定します。

b.アクティブエッジを Rising に設定します。

c.リセット初期値を1に設定します。

d.リセット信号の持続時間を 15 に設定します。

[Next] をクリックします。

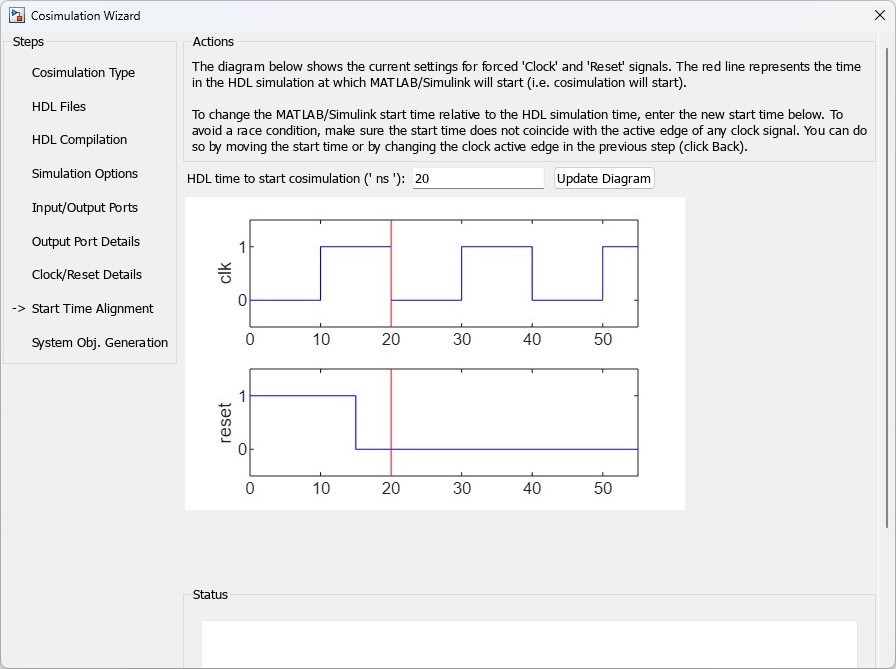

9. 開始時間の調整を確認する

「開始時間の調整」ページには、クロック信号とリセット信号の波形のプロットが表示されます。コシミュレーションウィザードは、コシミュレーションを開始する HDL 時間を赤い線で示します。開始時間は、System object が HDL シミュレータから最初の入力サンプルを取得する時間でもあります。クロックのアクティブ エッジは立ち上がりエッジです。したがって、HDL シミュレータの 20 ns の時点で、FFT の登録出力は安定します。競合状態は存在せず、コシミュレーションを開始するデフォルトの HDL 時間 (20 ns) は正しいです。

[Next] をクリックします。

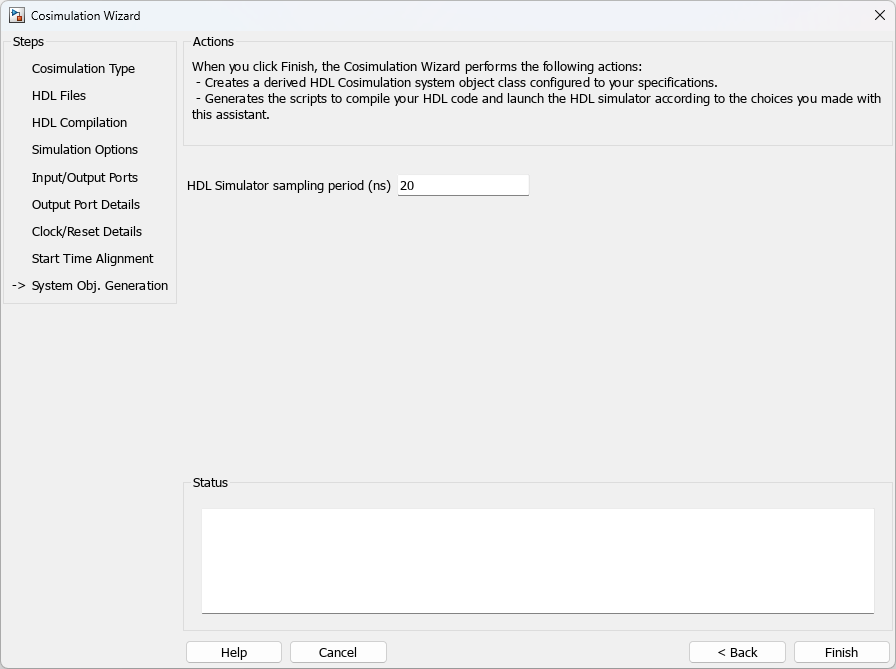

10. システムオブジェクトの生成

コシミュレーションウィザードがスクリプトを生成する前に、HDL シミュレータのサンプリング期間を変更するオプションがあります。サンプリング期間は、HDL シミュレーターでステップ イン MATLAB の各呼び出し間で経過する時間を決定します。サンプリング周期は通常、クロック周期と等しくなります。入力と出力がフレーム ベース (サンプル ベースではなく) であるかどうかも指定できます。

[完了] をクリックして、コシミュレーションウィザード セッションを完了します。

11. HDL設計を検証するためのテストベンチを作成する

この例では、例に付属するテストベンチ スクリプト fft_tb.m を使用できます。

コシミュレーションウィザードで [完了] をクリックすると、アプリケーションによって現在のディレクトリに 3 つの MATLAB スクリプトが生成されます。

ModelSim、Xcelium、Synopsys VCS 向け

compile_hdl_design_fft_hdl.m:HDL 設計をコンパイルします。

launch_hdl_simulator_fft_hdl.m:MATLAB System object サーバーを起動し、HDL シミュレーターを起動します。

hdlcosim_fft_hdl.m:HdlCosimulation System object を作成します。

Vivado シミュレータの場合

hdlverifier_compile.m:HDL デザインをコンパイルします。

hdlverifier_gendll_fft_hdl.m:System object の動作に統合された HDL 設計およびシミュレーション カーネルを含むコンパイル済み共有ライブラリを作成します。

hdlcosim_fft_hdl.m:HdlCosimulation System object を作成します。

Verilog ファイルと同じディレクトリにあるファイル fft_tb.m と hdlcosim_fft_hdl.m を開き、HdlCosimulation System object 呼び出しを確認します。hdlcosim_fft_hdl.m には HdlCosimulation のインスタンス化が含まれており、fft_tb.m には MATLAB System object テストベンチが含まれています。このテストベンチを使用して、対応する HdlCosimulation System object の HDL 設計を検証します。

12. コシミュレーションを実行してHDL設計を検証する

ModelSim、Xcelium、Synopsys VCS 向け

スクリプト compile_hdl_design_fft_hdl.m. を実行して HDL デザインをコンパイルします。

スクリプト launch_hdl_simulator_fft_hdl.m を実行して HDL シミュレータを起動します。

HDL シミュレータの準備ができたら、MATLAB に戻り、スクリプト fft_tb.m を実行してシミュレーションを開始します。

Vivado シミュレータの場合

スクリプト fft_tb.m を実行してシミュレーションを開始します。

テストベンチのプロットから結果を確認します。プロットには複素平面上のフーリエ係数が表示されます。