このページは前リリースの情報です。該当の英語のページはこのリリースで削除されています。

FPGA インザループを使用したデジタルアップコンバータの検証

この例では、FPGA インザループシミュレーションを使用して、Filter Design HDL Coder™ で生成されたデジタル アップコンバーター設計を検証する方法を示します。

要件

この例に必要なツール:

FPGA設計ソフトウェア

サポートされている FPGA 開発ボードおよびアクセサリの 1 つ (この例では ML403 ボードはサポートされていません)。サポートされているハードウェアの詳細については、FPGA検証でサポートされるFPGAデバイス を参照してください。

イーサネットを使用した接続の場合:ホストコンピュータにインストールされたギガビットイーサネットアダプタ、ギガビットイーサネットクロスオーバーケーブル

JTAGを使用した接続の場合:USB Blaster I または II、USB Blaster ドライバーを備えた JTAG ケーブル

PCI Express®を使用した接続の場合:ホスト コンピュータの PCI Express スロットにインストールされた FPGA ボード。

DUC のカスケード フィルターを作成する

デジタル アップコンバータ (DUC) は、デジタル ベースバンド信号をパスバンド信号に変換するデジタル回路です。DUC は 3 つのフィルタリング ステージで構成されます。各ステージでは、ローパス補間フィルタを使用して入力信号をフィルタリングし、その後にサンプル レートを変更します。この例では、DUC は、HDL デジタル アップコンバータ (DUC) の例で説明されているように、2 つの FIR 補間フィルタと 1 つの CIC 補間フィルタのカスケードです。

1. 2 つの FIR フィルターと CIC フィルターを作成します。

pfir = [0.0007 0.0021 -0.0002 -0.0025 -0.0027 0.0013 0.0049 0.0032 ... -0.0034 -0.0074 -0.0031 0.0060 0.0099 0.0029 -0.0089 -0.0129 ... -0.0032 0.0124 0.0177 0.0040 -0.0182 -0.0255 -0.0047 0.0287 ... 0.0390 0.0049 -0.0509 -0.0699 -0.0046 0.1349 0.2776 0.3378 ... 0.2776 0.1349 -0.0046 -0.0699 -0.0509 0.0049 0.0390 0.0287 ... -0.0047 -0.0255 -0.0182 0.0040 0.0177 0.0124 -0.0032 -0.0129 ... -0.0089 0.0029 0.0099 0.0060 -0.0031 -0.0074 -0.0034 0.0032 ... 0.0049 0.0013 -0.0027 -0.0025 -0.0002 0.0021 0.0007 ];

hpfir = dsp.FIRInterpolator(2, pfir); hpfir.FullPrecisionOverride = false; hpfir.CoefficientsDataType = 'Custom'; hpfir.CustomCoefficientsDataType = numerictype([],16); hpfir.ProductDataType = 'Custom'; hpfir.CustomProductDataType = numerictype([],31,31); hpfir.AccumulatorDataType = 'Custom'; hpfir.CustomAccumulatorDataType = numerictype([],16,15); hpfir.OutputDataType = 'Custom'; hpfir.CustomOutputDataType = numerictype([],16,15); hpfir.RoundingMethod = 'Nearest';

cfir = [-0.0007 -0.0009 0.0039 0.0120 0.0063 -0.0267 -0.0592 -0.0237 ... 0.1147 0.2895 0.3701 0.2895 0.1147 -0.0237 -0.0592 -0.0267 ... 0.0063 0.0120 0.0039 -0.0009 -0.0007];

hcfir = dsp.FIRInterpolator(2, cfir); hcfir.FullPrecisionOverride = false; hcfir.CoefficientsDataType = 'Custom'; hcfir.CustomCoefficientsDataType = numerictype([],16); hcfir.ProductDataType = 'Custom'; hcfir.CustomProductDataType = numerictype([],31,31); hcfir.AccumulatorDataType = 'Custom'; hcfir.CustomAccumulatorDataType = numerictype([],16,15); hcfir.OutputDataType = 'Custom'; hcfir.CustomOutputDataType = numerictype([],16,15); hcfir.RoundingMethod = 'Nearest';

hcic = dsp.CICInterpolator(32, 1, 5);

hcic.FixedPointDataType = 'Minimum section word lengths';

hcic.OutputWordLength = 20;

2. これらのフィルターを使用してカスケード フィルターを作成します。

hduc = dsp.FilterCascade(hpfir, hcfir, hcic);

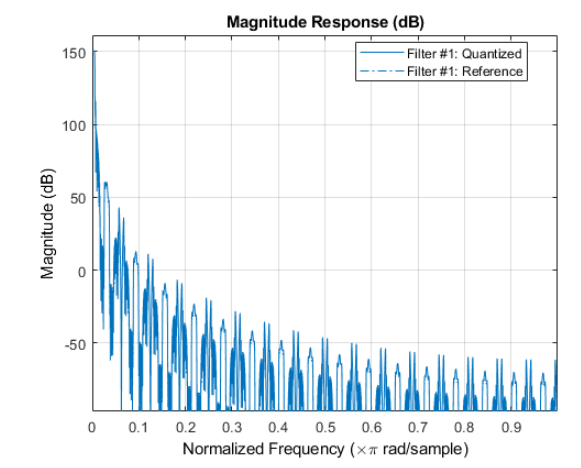

カスケード フィルタの周波数応答を次の図に示します。

fvtool(hduc,'Arithmetic','fixed');

HDL コードの生成

カスケード フィルターの準備ができたら、プロパティ 'AddPipelineRegisters' を 'on' に設定して、Filter Design HDL Coder 関数 generatehdl を使用して DUC の HDL コードを生成します。

generatehdl(hduc, 'Name', 'hdlduc', 'AddPipelineRegisters', 'on', 'InputDataType', numerictype(1,16,15));

このオプションは、フィルター ステージ間にパイプライン レジスタを挿入し、生成されたフィルターをより高いクロック周波数で合成できるようにします。

Filter Design HDL Coder がない場合は、現在のディレクトリにある事前に生成された HDL ファイルを使用できます。

FPGA設計ソフトウェアのセットアップ

FPGA インザループを使用する前に、FPGA 設計ソフトウェアにアクセスするためのシステム環境が適切に設定されていることを確認してください。関数 hdlsetuptoolpath を使用して、現在の MATLAB セッションのシステム パスに FPGA 設計ソフトウェアを追加できます。

FPGAインザループの構成と構築

FIL ウィザードは、FPGA インザループの構築に必要な設定をガイドします。次のコマンドでウィザードを起動します。

filWizard

1. ハードウェア オプションで、ホスト コンピューターに接続されている FPGA 開発ボードを選択します。必要に応じて、「詳細オプション」でボードの IP と MAC アドレスをカスタマイズすることもできます。続行するには「*次へ」をクリックします。

2. [ソース ファイル] で、[参照] を使用して、DUC 用に生成された次の HDL ファイルをソース ファイル テーブルに追加します。

hdlduc.vhd hdlduc_stage1.vhd hdlduc_stage2.vhd hdlduc_stage3.vhd

hdlduc.vhd の横にある最上位のチェックボックスを選択します。続行するには「*次へ」をクリックします。

3. DUT I/O ポートでは、ポート名、方向、幅、ポート タイプなどの入力ポートと出力ポートの情報が HDL ファイルから自動的に生成されます。クロックやデータなどのポート タイプはポート名に基づいて生成されます。必要に応じて選択を変更できます。この例では、生成されたポート タイプは正しいので、[次へ] をクリックできます。

4. ビルド オプションで、FIL 出力ファイルのフォルダーを指定します。この例ではデフォルト値を使用できます。ビルドをクリックします。ビルドをクリックすると、FIL ウィザードによって FPGA インザループ シミュレーションに必要なすべてのファイルが生成され、次のアクションが実行されます。

新しいSimulink®モデルでFILブロックを生成します

FPGAプロジェクトをコンパイルし、FPGAプログラミングファイルを生成するためのコマンドラインウィンドウを開きます。

FPGA プロジェクトのコンパイル プロセスには数分かかります。プロセスが完了すると、コマンド ライン ウィンドウを閉じるように求められます。今すぐこのウィンドウを閉じてください。

FILブロックを構成する

FPGA インザループ シミュレーションを準備するには、以下の手順に従って FIL ブロックを構成します。

1. モデルを開くボタンを開いてテストベンチ モデルを開き、生成された FIL ブロックをモデルにコピーします。

2. FIL ブロックをダブルクリックしてブロック マスクを開きます。生成されたプログラミング ファイルを使用して FPGA をプログラムするには、ロード をクリックします。

3. ランタイム オプションで、オーバークロック係数 を 128 に変更します。これは、入力値が変化する前に、FPGA クロックによって入力値が 128 回サンプリングされることを指定します。

4. FIL ブロック マスクで、[信号属性] タブをクリックします。動作フィルタ ブロックのデータ型と一致するように、filter_out のデータ型を fixdt(1,20,-1) に変更します。

5. ブロックマスクを閉じるには、OK をクリックします。

生成されたフィルターを確認する

この例では、FPGA 上で実行される生成されたフィルターを動作フィルター ブロックと比較します。生成されたフィルターの HDL レイテンシに合わせて、動作フィルターの出力に遅延が追加されます。

シミュレーションを実行します。動作フィルタ ブロック、FIL ブロックからの出力波形と誤差マージンを観察します。ビヘイビア フィルタ ブロックにはパイプライン レジスタがないため、ビヘイビア フィルタ ブロックの出力と FIL ブロックの出力にはわずかな違いがあります。これらのエラーは誤差範囲内です。

これで例は終了です。