このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

Simulink 向け HDL ワークフロー アドバイザーによる FIL シミュレーション

手順 1: HDLワークフローアドバイザーを起動する

HDL ワークフロー アドバイザーを呼び出すための手順に従います。HDL ワークフロー アドバイザーのご利用の前に (HDL Coder)を参照してください。

メモ

HDL ワークフロー アドバイザーを使用して HDL コードを生成するには、HDL Coder™ ライセンスが必要です。

手順 2: 目標と目標頻度を設定する

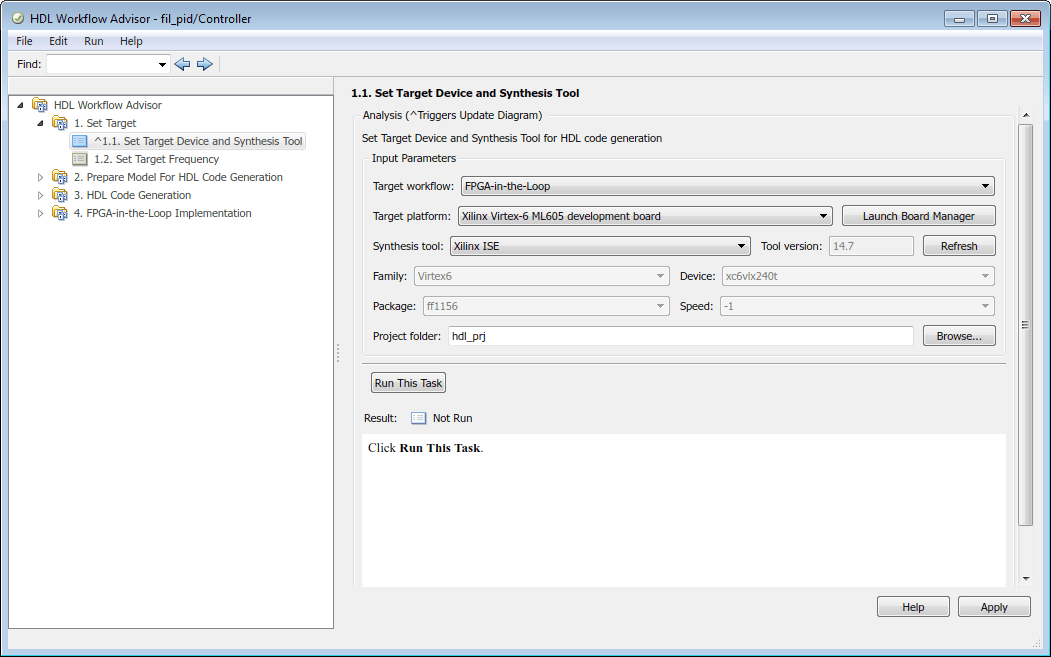

ステップ 1 の Set Target で、1.1 Set Target Device and Synthesis Tool をクリックして、次の操作を行います。

ターゲット ワークフロー のプルダウンリストから

FPGA インザループを選択します。ターゲット プラットフォーム の下で、プルダウン リストから開発ボードを選択します。ファミリ、デバイス、パッケージ、および Speed は、HDL ワークフロー アドバイザーによって入力されます。HDL Verifier™ FPGA ボード サポート パッケージをまだダウンロードしていない場合は、

Get more boardsを選択してください。FPGA ボード サポート パッケージをダウンロードしたら、この手順に戻ります。プロジェクト フォルダー の場合は、プロジェクト ファイルを保存するフォルダー名を入力します。デフォルトは、現在の作業フォルダーの下の

hdl_prjです。

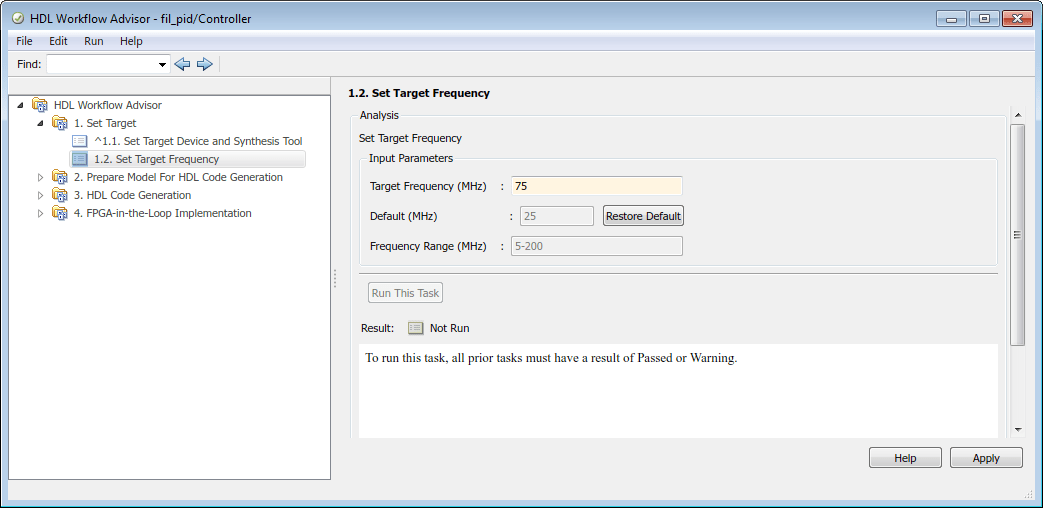

ステップ 1.1 で FIL ターゲットを選択した後、1.2 Set Target Frequency をクリックします。

FPGA に実装されたデザインのクロック速度に合わせて ターゲット周波数 (MHz) を設定します。使用可能な周波数の範囲は、周波数範囲 (MHz)パラメーターに表示されます。Intel® ボードおよび AMD® ボードの場合、ワークフロー アドバイザーは要求された周波数を、要求されたボードで可能な周波数と比較します。要求された周波数がこのボードでは不可能な場合、ワークフロー アドバイザーはエラーを返し、代替周波数を提案します。AMD Vivado® 対応ボード、または PCI Express® 対応ボードの場合、ワークフロー アドバイザーは周波数をチェックできません。合成ツールは要求された周波数を最大限に利用しようとしますが、指定された周波数が達成できなかった場合は別の周波数を選択する場合があります。デフォルトは

25MHz です。

手順 3: HDLコード生成用のモデルの準備

ステップ 2 (HDL コード生成に対するモデルを準備) では、[HDL コード生成に対するモデルを準備] の概要 (HDL Coder) で説明されているようにステップ 2.1 を実行します。

さらに、ステップ 2.2 FPGA インザループ互換性の確認 を実行して、モデルが FIL と互換性があることを確認します。

メモ

HDL モジュールにクロック イネーブル付きのブラック ボックスが含まれている場合は、Minimize clock enable 構成パラメーターをクリアする必要があります。詳細については、クロック イネーブルの最小化 (HDL Coder)を参照してください。

手順 4: HDL コード生成

ステップ 3 (HDL コード生成) では、[HDL コード生成] の概要 (HDL Coder) で説明されているように、ステップ 3.1 と 3.2 を実行します。

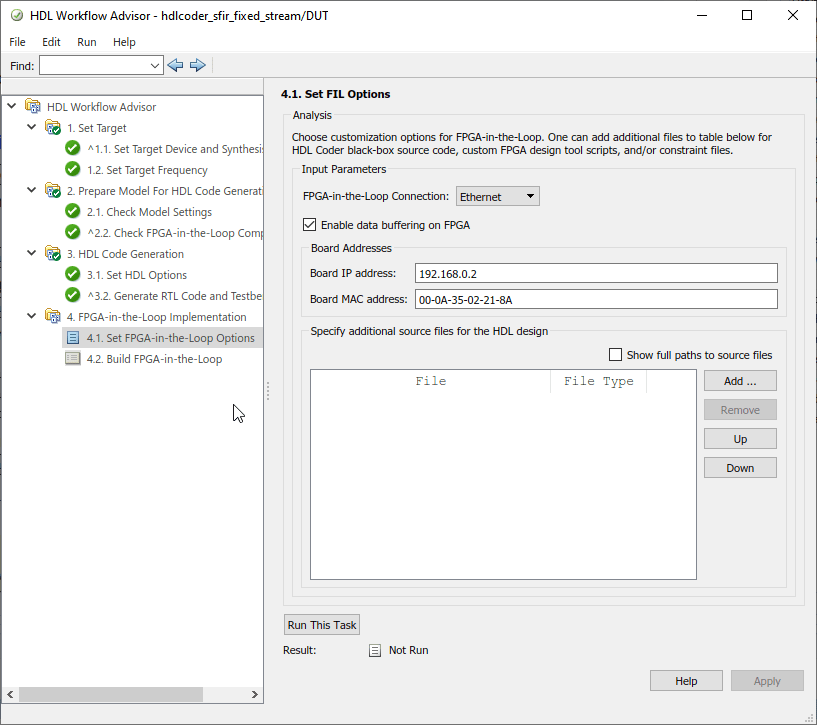

手順 5: FPGA インザループのオプションの設定

ステップ 4.1 で、Set FPGA-in-the-Loop Options は必要に応じて次のオプションを変更します。

FPGA インザループの接続:FIL シミュレーションの接続方法を選択します。ドロップダウン メニューのオプションは、選択したターゲット ボードでサポートされる接続方法に応じて更新されます。ターゲット ボードと HDL Verifier で接続がサポートされている場合、

[イーサネット]、[JTAG]、[PCI Express]、または[USB Ethernet]を選択できます。MATLAB/FPGA 同期モード:データを MATLAB® と DUT の間でストリーミングするためのモードを選択します。ターゲット ボードと FIL の接続でサポートされている場合、次のモードのいずれかを選択できます。

ロックステップ — このモードでは、FPGA の DUT が MATLAB とロックステップで動作します。これが既定のオプションであり、FIL シミュレーションでは暗黙的にこのモードになります。

フリーラン FPGA — このモードでは、FPGA の DUT が MATLAB と非同期に実行されます。ハードウェア クロックは FPGA 自体の内部で連続的に動作します。

メモ

このモードは、MATLAB System object™ で FIL を使用する場合にのみ機能します。FIL を Simulink® ブロックで使用する場合は機能しません。

これらのモードの詳細については、What Is Free-Running FPGA-in-the-Loop?を参照してください。

ホスト インターフェイス スクリプトの生成:このオプションを選択すると、ホスト インターフェイス スクリプト

gs_が生成されます。ここで、DUTName_interface_fil.mDUTNamefilObjオブジェクトを作成します。インターフェイス スクリプトには、ハードウェアに接続して FPGA をプログラムする MATLAB コマンド、およびハードウェアでのアルゴリズムの実行時にアルゴリズムとデータを交換する方法を示した例が含まれます。FPGA でのデータ バッファリングを有効化:このオプションを選択すると、シミュレーションのパフォーマンスが向上します。選択した場合、FIL で FPGA の BRAM が利用され、イーサネット パケットがフレームベースの処理モードでバッファリングされます。このパラメーターは、BRAM リソースが十分でない設計の場合はオフにしてください。イーサネット接続でのみ利用できます。

ボード アドレス:

FPGA ボードのイーサネット接続を選択する場合、必要に応じてボードの IP アドレスと MAC アドレスを調整できます。ボードに処理ユニットが含まれている場合は、ガイド付きハードウェアセットアップ を使用して SD カードを構成します。

オプション 説明 ボード IP アドレス ボードの IP アドレスがデフォルトの IP アドレス (192.168.0.2) でない場合は、このオプションを使用して IP アドレスを設定します。

デフォルトのボード IP アドレス (192.168.0.2) が別のデバイスで使用されている場合、または別のサブネットが必要な場合は、次のガイドラインに従ってボード IP アドレスを変更します。

サブネット アドレス (通常はボード IP アドレスの最初の 3 バイト) は、ホスト IP アドレスのサブネットと同じである必要があります。

ボードの IP アドレスの最後のバイトは、ホストの IP アドレスの最後のバイトと異なる必要があります。

ボードの IP アドレスは、他のコンピューターの IP アドレスと競合しないものを使用しなければなりません。

たとえば、ホスト IP アドレスが 192.168.8.2 の場合、192.168.8.3 が使用可能であれば、使用できます。

ボード MAC アドレス ほとんどの場合、ボードの MAC アドレスを変更する必要はありません。複数の FPGA 開発ボードを 1 台のホスト コンピューターに接続する場合は、追加ボードのボード MAC アドレスを変更して、各アドレスが一意になるようにします。各ボードごとに個別の NIC が必要です。

ボードの MAC アドレスを変更するには、[ボード MAC アドレス] フィールドをクリックします。コンピューターに接続されている他のデバイスに属しているアドレスとは異なるアドレスを指定します。特定の FPGA 開発ボードのボード MAC アドレスを取得するには、ボードに貼られているラベルを参照するか、製品ドキュメンテーションを参照してください。

HDL 設計の追加ソース ファイルの指定:

追加 を使用して、DUT の追加ソース ファイルを指定します。ソース ファイルへの完全なパスを (オプションで) 表示するには、ソース ファイルへの絶対パスを表示する というタイトルのボックスをオンにします。HDL ワークフロー アドバイザーは、ソース ファイルの種類を識別しようとします。ファイルの種類が正しくない場合は、ファイル タイプ ドロップダウン リストから選択して変更できます。

FIL オプション

手順 6: Set DUT I/O Ports

この手順は、フリーラン FPGA モードを選択した場合にのみ有効になります。

ステップ 4.2 の Set DUT I/O Ports では、HDL ワークフロー アドバイザーが最上位ファイルから DUT の入力ポートと出力ポートを解析します。それぞれの端子タイプは HDL 端子名から推定されます。端子タイプを検証し、必要に応じて変更します。

ステップ7:FPGAプログラミングファイル、FILモデル、ホストインターフェーススクリプトを生成する

ステップ 4.3 (ロックステップ モードの場合は 4.2) で、FPGA インザループのビルド をクリックし、このタスクを実行 をクリックします。

ビルド プロセス中に、次のアクションが実行されます。

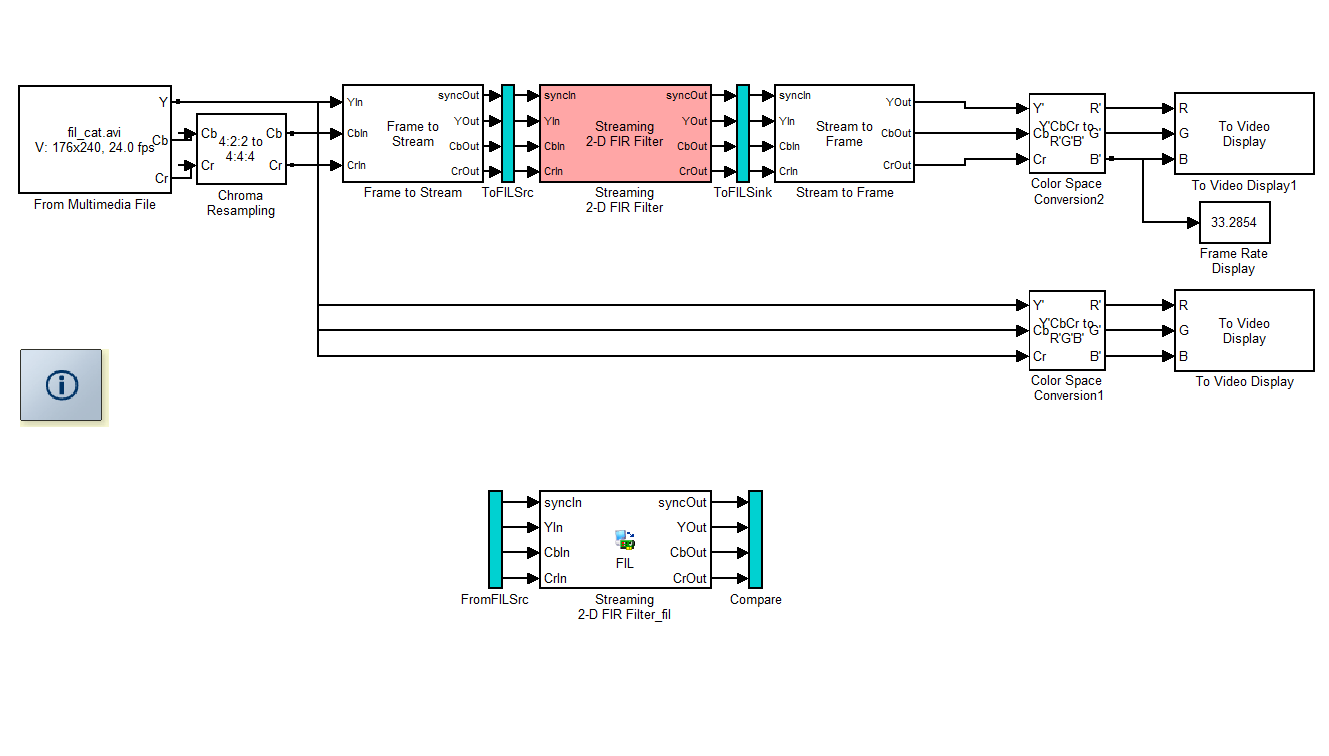

ロックステップ モードのみ - HDL ワークフロー アドバイザーは、最上位モジュールにちなんで名付けられた FIL ブロックを生成し、それを新しいモデルに配置します。次の図は、FIL ブロックを含む新しいモデルの例を示しています。

メモ

フリーランニング FIL の場合、HDL ワークフロー アドバイザーは Simulink 検証モデルを生成しません。このモードは、FIL を MATLAB System object と共に使用する場合にのみ機能するためです。FIL を Simulink ブロックで使用する場合は機能しません。

新しいモデルが生成されると、HDL ワークフロー アドバイザーはコマンド ウィンドウを開きます。

このウィンドウでは、FPGA 設計ソフトウェアが合成、フィット、PAR、および FPGA プログラミング ファイルの生成を実行します。

プロセスが完了すると、コマンド ウィンドウにウィンドウを閉じるように求めるメッセージが表示されます。

ロックステップ モードのみ - HDL ワークフロー アドバイザーは、生成された FIL ブロックの周囲にテストベンチ モデルを構築します。

手順 4.1 で ホスト インターフェイス スクリプトの生成 オプションを選択した場合、HDL ワークフロー アドバイザーは MATLAB から FPGA とインターフェイスするためのホスト インターフェイス スクリプトを生成します。

ステップ7:プログラミングファイルをFPGAにロードする

FPGA 開発ボードが、ボード製造元のドキュメントの指示に従ってセットアップされ、電源がオンになっており、マシンに接続されていることを確認します。次に、以下の手順を実行して FPGA をプログラムします。

Simulink モデル内の FIL ブロックをダブルクリックして、ブロック マスクを開きます。

メイン タブで、Load をクリックしてプログラミング ファイルを FPGA にダウンロードします。

サブシステムの大きさに応じて、ロード プロセスには数分かかる場合があります。非常に大規模なサブシステムの場合、プロセスには 1 時間以上かかることがあります。

あるいは、生成されたホスト インターフェイス スクリプト gs_ を使用して FPGA をプログラムすることもできます。DUTName_interface_fil.m

さらなるトラブルシューティングのヒントについては、プログラミングファイルをFPGAにロードする を参照してください。

ステップ8:シミュレーションの実行

Simulink の シミュレーション タブで、Run をクリックします。FIL シミュレーションの結果は、Simulink リファレンス モデルまたは元の HDL コードの結果と一致する必要があります。

メモ

初期化について: Simulink は毎回時間 0 から開始します。つまり、Simulink 内の RAM はゼロに初期化されます。しかし、ハードウェアではこれは当てはまりません。設計に RAM が含まれている場合、最初のシミュレーションは Simulink と一致しますが、それ以降の実行は一致しない可能性があります。

回避策としては、シミュレーションを再実行する前に FPGA ビットストリームを再ロードします。これを行うには、FIL ブロック マスクで Load をクリックします。