このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FIL Simulation

Simulink の FPGA ハードウェア上で HDL コードをシミュレートする

ライブラリ:

Generated

説明

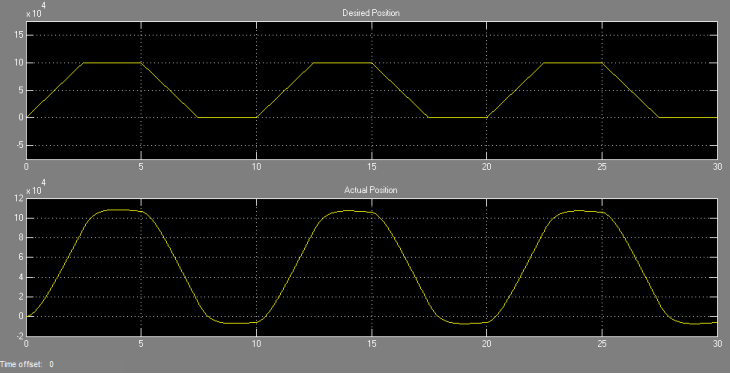

生成された FPGA インザループ (FIL) シミュレーション ブロックは、FPGA と Simulink® モデル間の通信インターフェイスです。ハードウェアをシミュレーション ループに統合し、他のブロックと同様にシミュレーションに参加できるようにします。

FPGA-in-the-Loop Wizard を使用して既存の HDL コードから FIL Simulation ブロックを生成することも、HDL ワークフロー アドバイザーを使用して HDL コードとそれに付随する FIL Simulation ブロックを生成することもできます。HDL コードを生成するには、HDL Coder™ ライセンスが必要です。

生成とシミュレーションのワークフローについては、FILウィザードによるブロック生成 を参照してください。FIL シミュレーション中に問題が発生した場合は、問題の診断については FIL のトラブルシューティング を参照してください。

FIL Simulation ブロックは、通常、アクセラレータ、またはラピッド アクセラレータ シミュレーション モードで実行されているモデルで使用できます。FIL Simulationパラメーターはどのシミュレーション モードでも調整できません。これらのモードの詳細については、アクセラレータ モードの動作 (Simulink) を参照してください。

例

端子

ブロックのポートは、FPGA 上で実行されている HDL デザインのインターフェースに対応します。FIL Simulation ブロックが Simulink に返す信号のデータ型を設定できます。

入力

出力

パラメーター

バージョン履歴

R2012b で導入