このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA インザループを使用した通信システムシミュレーションの高速化

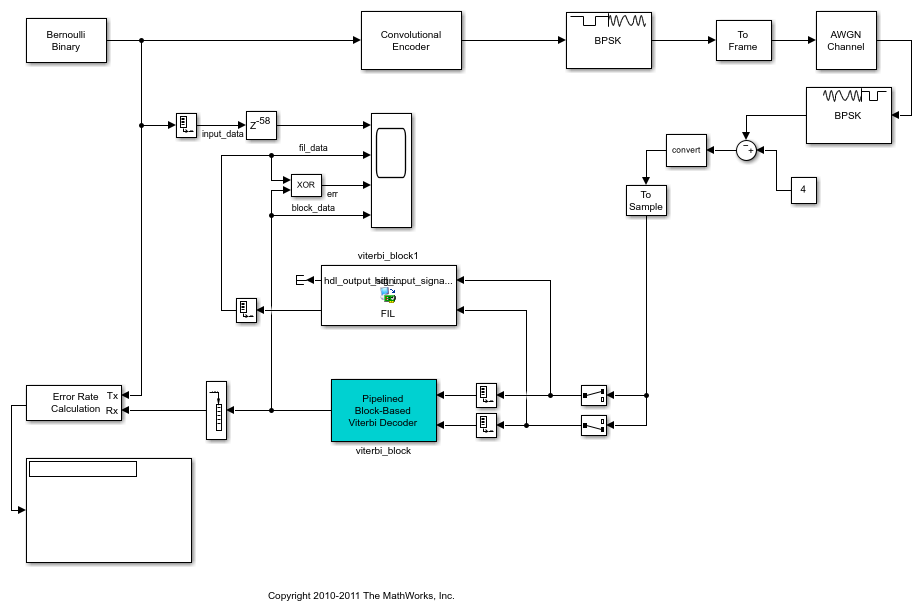

この例では、FPGA インザループ (FIL) シミュレーションを使用して、通信システムの一部を高速化します。アプリケーションは、Viterbi アルゴリズムを使用して、BPSK 変調され、AWGN チャネルを介して送信され、その後復調された畳み込みエンコードされたランダム ストリームをデコードします。サンプルごとのアプローチを使用すると、通常の Simulink® シミュレーションよりも若干の高速化が実現されますが、「フレームとして処理」オプションを使用すると、さらに高速化が実現されます。

要件と前提条件

この例を実行するために必要なツール:

FPGA検証要件 にサポートされているバージョンがリストされている FPGA 設計ソフトウェア (Xilinx® ISE® 設計スイート、Xilinx Vivado® 設計スイート、Intel® Quartus® II 設計ソフトウェア、または Microchip Libero® SoC 設計ソフトウェア)。

サポートされている FPGA 開発ボードの 1 つ。サポートされているハードウェアについては、FPGA検証でサポートされているFPGAデバイス を参照してください。

イーサネットを使用した接続の場合:ホストコンピュータにインストールされたギガビットイーサネットアダプタ、ギガビットイーサネットクロスオーバーケーブル

JTAGを使用した接続の場合:Intel FPGA ボード用の USB Blaster I または II ケーブルとドライバー。Xilinx FPGA ボード用の Digilent® JTAG ケーブルとドライバー。

PCI Express®を使用した接続の場合:ホスト コンピュータの PCI Express スロットにインストールされた FPGA ボード。

USBイーサネットを使用した接続の場合:ターゲット ボードと互換性のある USB 3.0 または 2.0 ケーブル。

インストーラーがサポート パッケージのインストールを完了すると、ハードウェア ボードとの通信を確立するプロセスをガイドします。選択したハードウェア ボードと接続タイプのセットアップ プロセスを完了します。セットアップ手順の詳細については、ガイド付きハードウェアセットアップ を参照してください。

1. Simulink モデルを開いて実行する

モデルを開きます。処理するデータ量が多いため、FIL なしではシミュレーションに約 9 秒かかります。この例では、FIL を使用して次の手順でシミュレーション速度を向上させます。

2. HDL コードの生成

このステップには HDL Coder™ が必要です。HDL Coder がない場合は、現在のディレクトリにある事前に生成された HDL ファイルを使用できます。

コピーしたファイルを使用する場合は、手順 3 に直接進みます。

次の手順を実行して、Viterbi ブロック サブシステムの HDL コードを生成します。

a.viterbi_block1 というラベルの付いた既存の FIL ブロックを右クリックします。コード生成のこのブロックを削除するには、コメントアウト をクリックします。

b.[モデル化] タブで [モデル設定] をクリックします。

d. HDL コード生成 ペインをクリックし、hdlcoderviterbi_for_fil/viterbi_block が選択されていることを確認します。

e.[生成] をクリックします。

あるいは、MATLAB プロンプトで次のコマンドを入力して HDL コードを生成することもできます。

makehdl('hdlcoderviterbi_for_fil/viterbi_block')

3. FPGA設計ソフトウェア環境の設定

FIL を使用する前に、FPGA 設計ソフトウェアにアクセスするためのシステム環境が適切に設定されていることを確認してください。関数 hdlsetuptoolpath を使用して、現在の MATLAB セッションのシステム パスに FPGA 設計ソフトウェアを追加できます。以下に各ツールのコマンドラインの例を示します。異なる場合は、実際の実行可能ファイルに置き換えてください。

ISE 設計ソフトウェアを使用する Xilinx FPGA ボードの場合は、次を実行します。

hdlsetuptoolpath('ToolName','Xilinx ISE','ToolPath','C:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\ise.exe');

Vivado 設計ソフトウェアを使用する Xilinx FPGA ボードの場合は、次を実行します。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2020.2\bin\vivado.bat');

Intel ボードの場合は、次を実行します。

hdlsetuptoolpath('ToolName','Altera Quartus II','ToolPath','C:\altera\20.1.1\quartus\bin\quartus.exe');

Microchip ボードの場合は、次を実行します。

hdlsetuptoolpath('ToolName','Microchip Libero SoC','ToolPath','C:\Microsemi\Libero_SoC_v12.0\Designer\bin\libero.exe');

4. FILウィザードを実行する

FIL ウィザードを起動するには、MATLAB プロンプトで次のコマンドを入力します。

filWizard;

4.1 FILウィザードでハードウェアオプションを指定する

FPGA 開発ボードの FIL オプションを設定します。

1. ウィザードが FIL Simulink ブロックを生成するか、FIL シミュレーション MATLAB System object™ を生成するかを指定します。この例では、FIL シミュレーション セクションで、Simulink を選択します。

2. ボード名では、ホストコンピュータに接続されている FPGA 開発ボードを選択します。ボードがリストにない場合は、次のいずれかのオプションを選択します。

Get more boards...をクリックして FPGA ボード サポート パッケージをダウンロードします (このオプションによりサポート パッケージ インストーラーが起動します)。Create custom board...は、FPGA ボード用の FPGA ボード定義ファイルを作成します (このオプションは、新しい FPGA ボード ウィザードを起動します)。

3. シミュレーションの接続を選択します。使用可能な接続方法は、JTAG、イーサネット、PCIe、USB イーサネットです。すべてのボードがすべての接続方法をサポートしているわけではありません。サポートされているボードと接続方法の完全なリストについては、FPGA検証でサポートされているFPGAデバイス を参照してください。

4.USBイーサネット接続のみ:Zynq ボード上の USB コントローラーは、ホストまたはデバイスとして機能できます。FIL ワークフローに使用される DTB は、それを USB イーサネット デバイスとして構成します。ボードが USB ポートを使用してホスト コンピューターに接続されると、Mathworks USB Ethernet/RNDIS Gadget という名前のネットワーク アダプターとして列挙されます。ホスト上のこのネットワーク アダプターの構成は、Zynq ボード上で実行される DHCP サービスを使用して自動化されます。

5. [次へ] をクリックして続行します。

4.2 ソースファイル

a.Viterbi Block サブシステム用に以前に生成されたすべての HDL ソース ファイルを追加します。

b.最上位ファイルとしてファイル viterbi_block.vhd を選択します。これらのオプションを表示するには、FIL ウィザード ウィンドウを広くする必要がある場合があります。

c. デフォルトのトップレベルモジュール名として viterbi_block が入力されていることに注意してください。[次へ] をクリックして続行します。

d. [次へ] をクリックして続行します。

4.3 DUT I/O ポート

ポートリストを確認します。パーサーが特定のポートに対して誤ったポート タイプを割り当てた場合は、手動で信号を変更できます。[次へ] をクリックして続行します。

4.4 ビルドオプション

a.出力フォルダを選択します。

b.ビルド をクリックして、FIL ブロックとプログラミング ファイルをビルドします。

ビルド プロセス中に、次のアクションが実行されます。

新しいモデルで viterbi_block という名前の FIL ブロックが生成されます。

新しいモデルが生成されると、FIL ウィザードはコマンド ウィンドウを開き、FPGA 設計ソフトウェアが合成、マッピング、配置配線、タイミング解析、FPGA プログラミング ファイルの生成を実行します。このブロックの場合、これらの手順には約 20 分かかります。

FPGA 設計ソフトウェア プロセスが終了すると、コマンド ウィンドウにウィンドウを閉じることができることを通知するメッセージが表示されます。

5. FIL のオープンで完全な Simulink モデル

a.hdlcoderviterbi_for_fil.slx を開きます。

b.以前生成した FIL ブロックをこのモデルにコピーします。viterbi_block1 を新しい FIL ブロックに置き換えます。元のブロックでは入力が右側にあることに注意してください。FIL ブロックの入力を右側に配置するには、ブロックを右クリックし、[書式] > [ブロックの反転] を選択します。

6. FILブロックを構成する

a.モデル内の FIL ブロックをダブルクリックして、ブロック マスクを開きます。

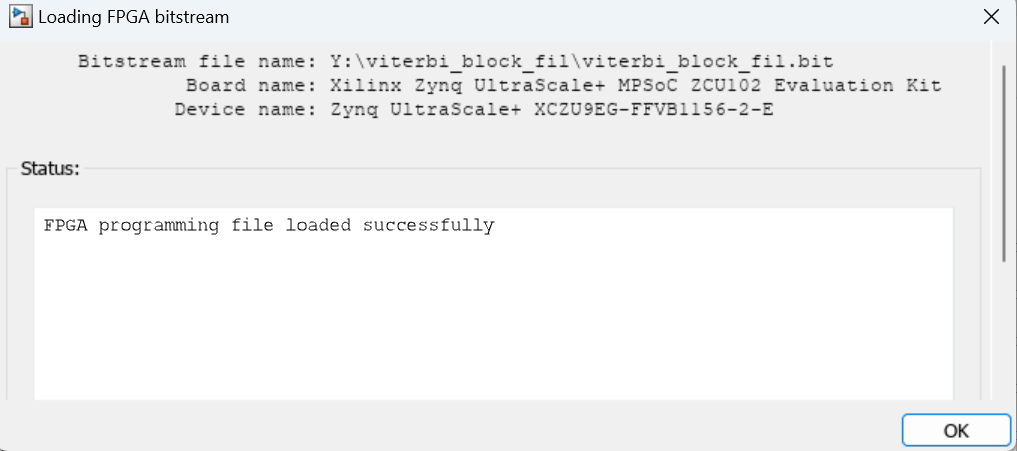

b.[ロード]をクリックします。

FPGA ボードをプログラムするには、JTAG ケーブルを使用します。Zynq ボードをプログラムするには、JTAG 接続には JTAG ケーブル、イーサネット接続にはイーサネット ケーブル、USB イーサネット接続には USB ケーブルを使用します。ボードが正しくセットアップされている場合、FPGA プログラミング ファイルが正常にロードされたことを示すメッセージ ウィンドウが表示されます。このダイアログを閉じるには、[OK] をクリックします。

c. ブロックマスクを閉じるには、OK をクリックします。

7. FILシミュレーションを実行する

a.FIL ブロックのみでシミュレーションを実行するには、hdlcoderviterbi_for_fil/viterbi_block のコメントを解除します。このアクションを実行するには、ブロックを右クリックし、コメントアウト を選択します。

b.シミュレーションを 20480 秒間実行し、パフォーマンスを観察します。

FrameSize = 1;

tic;

sim('hdlcoderviterbi_for_fil');

fs1 = toc

フレーム サイズをより大きな数値に設定してみてください。この例では、フレーム サイズは 1024 バイトに設定されています。

FrameSize = 1024;

tic;

sim('hdlcoderviterbi_for_fil');

fs2 = toc

Windows での Xilinx Zynq UltraScale+ MPSoC ZCU102 評価キットの USB イーサネットのテストでは、FrameSize = 1 の場合、シミュレーション時間は約 232 秒でした。ただし、フレーム サイズを 1024 に増やすと、シミュレーション時間は約 4.5 秒に短縮され、FIL なしの Simulink でのシミュレーション時間のほぼ半分になりました。FrameSize = 1024 の場合、この特定のボードとシステムでは約 50 倍の速度向上が得られます。他のボードや通信システムではさらに高速になる場合があることに注意してください。

speedup = fs1 / fs2

設計の FIL 部分にブロックを追加し、Simulink スコープとディスプレイの使用を最小限に抑えることで、さらに高速化を実現できます。

これで、FPGA インザループを使用した通信システムシミュレーションの高速化の例は終了です。