このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FIL ウィザードによるシステムオブジェクトの生成

手順 1: FPGA設計ソフトウェアツールのセットアップ

手順 2: FILウィザードを起動

FPGA-in-the-Loop Wizardを開きます。

MATLAB コマンド ウィンドウで、次のように入力します。

>> filWizard

以前のセッションを復元するには、次のコマンドを使用します。

filWizard('./Subsystem_fil/Subsystem_fil.mat')手順 3: システムオブジェクトの FIL オプションを設定する

(このページは FIL System object™ 用です。Simulink® ブロック FIL オプションについては、手順 3: FILブロックのFILオプションを設定する を参照してください。

FIL Options ページ内:

FIL Simulation with:

MATLAB System Objectを選択します。Board Name: FPGA 開発ボードを選択します。HDL Verifier™ FPGA ボード サポート パッケージをまだダウンロードしていない場合は、FPGAボードサポートパッケージをダウンロード を参照してください。(ボードがリストに表示されない場合は、サポート パッケージをまだダウンロードしていません)。自分でカスタムボードを定義する予定の場合は、FPGA ボードのカスタマイズ を参照してください。

FPGA-in-the-Loop Connection:FILシミュレーションの接続方法。ドロップダウン メニューのオプションは、選択したターゲット ボードでサポートされている接続方法に応じて更新されます。ターゲット ボードと HDL Verifier が接続をサポートしている場合は、

Ethernet、JTAG、PCI Express、またはUSB Ethernetを選択できます。Advanced Options:

イーサネット接続を選択すると、必要に応じてボードの IP アドレスと MAC アドレスを調整できます。

オプション 手順 ボード IP アドレス ボードの IP アドレスがデフォルトの IP アドレス (192.168.0.2) でない場合は、このオプションを使用して IP アドレスを設定します。

デフォルトのボード IP アドレス (192.168.0.2) が別のデバイスで使用されている場合、または別のサブネットが必要な場合は、次のガイドラインに従ってボード IP アドレスを変更します。

サブネット アドレス (通常はボード IP アドレスの最初の 3 バイト) は、ホスト IP アドレスのサブネットと同じである必要があります。

ボード IP アドレスの最後のバイトは、ホスト IP アドレスの最後のバイトと異なる必要があります。

ボードの IP アドレスは、他のコンピューターの IP アドレスと競合しないものを使用しなければなりません。

たとえば、ホスト IP アドレスが 192.168.8.2 の場合、192.168.8.3 が使用可能であれば、使用できます。

ボード MAC アドレス ほとんどの場合、ボードの MAC アドレスを変更する必要はありません。複数の FPGA 開発ボードを 1 台のホスト コンピューターに接続する場合は、追加ボードのボード MAC アドレスを変更して、各アドレスが一意になるようにします。ボードごとに個別の NIC が必要です。

ボードの MAC アドレスを変更するには、[ボード MAC アドレス] フィールドをクリックします。コンピューターに接続されている他のデバイスに属しているアドレスとは異なるアドレスを指定します。特定の FPGA 開発ボードのボード MAC アドレスを取得するには、ボードに貼られているラベルを参照するか、製品ドキュメンテーションを参照してください。

FPGA system clock frequency (MHz):ターゲットクロック周波数を入力します。Intel ボードおよび Xilinx ISE 対応ボードの場合、

filWizardは要求された周波数を要求されたボードで可能な周波数と比較します。要求された周波数がこのボードで利用できない場合は、filWizardはエラーを返し、別の周波数を提案します。Xilinx Vivado 対応ボード、または PCI Express® 対応ボードの場合、filWizardは周波数をチェックできません。合成ツールは要求された周波数で最善の努力をしますが、指定された周波数が達成できなかった場合は別の周波数を選択することがあります。デフォルトは25MHz です。Enable data buffering on FPGA:シミュレーションのパフォーマンスを向上させるには、このオプションを選択します。選択すると、FIL は FPGA 上の BRAM を使用して、フレームベースの処理モードでイーサネット パケットをバッファリングします。設計で BRAM リソースが不足している場合は、このパラメータをクリアします。イーサネット接続のみ使用可能です。

[Next] をクリックします。

手順 4: システムオブジェクトのHDLソースファイルを追加する

(このページは FIL System object 用です。Simulink ブロック HDL ソース ファイルについては、手順 4: FILブロックのHDLソースファイルを追加する を参照してください。

Source Files ページ内:

FPGA でコシミュレーションする HDL 設計を指定します。これらのファイルは、FPGA ボード上で検証される HDL 設計ファイルです。

Add をクリックしてソース ファイルを指定します。ファイル選択ダイアログボックスを使用してファイルを選択します。

FIL ウィザードはソース ファイルの種類を識別しようとします。ファイルの種類が期待したものと異なる場合は、File Type ドロップダウン リストから選択して変更できます。許容されるファイルの種類は次のとおりです:

VHDL®

Verilog®

ネットリスト

Tcl スクリプト

制約

その他

「その他」とは、以下のものを指します。

Intel の場合、

Otherとして指定されたファイルは FPGA プロジェクトに追加されますが、生成されたブロックには影響しません。たとえば、readmeファイルにコメントをいくつか入れて、このファイル リストに含めることができます。Xilinx の場合、

Otherとして指定されたファイルは、Xilinx ISE で受け入れられる任意のファイルになります。ISE はファイル拡張子を見て、このファイルの使用方法を決定します。たとえば、リストにfoo.vhdを追加し、それをOtherとして指定すると、ISE はファイルを VHDL ファイルとして扱います。

最上位 HDL ファイルが含まれるファイルを指定します。

Top-level というタイトルの列にある最上位 HDL モジュールを含む HDL ファイルの行のボックスをオンにします。FIL ウィザードは、選択した HDL ファイルの名前を Top-level module name フィールドに自動的に入力します。トップレベル モジュール名とファイル名が一致しない場合は、このダイアログ ボックスでトップレベル モジュール名を手動で変更できます。続行する前に、最上位モジュール名を指定します。

(オプション) ソース ファイルへの完全なパスを表示するには、Show full paths to source files というタイトルのボックスをオンにします。

[Next] をクリックします。

手順 5: システムオブジェクトのDUT I/Oポートを検証する

(このページは、System object を持つ FIL 用です。Simulink については、手順 5: FILブロックのDUT I/Oポートを検証する を参照してください。

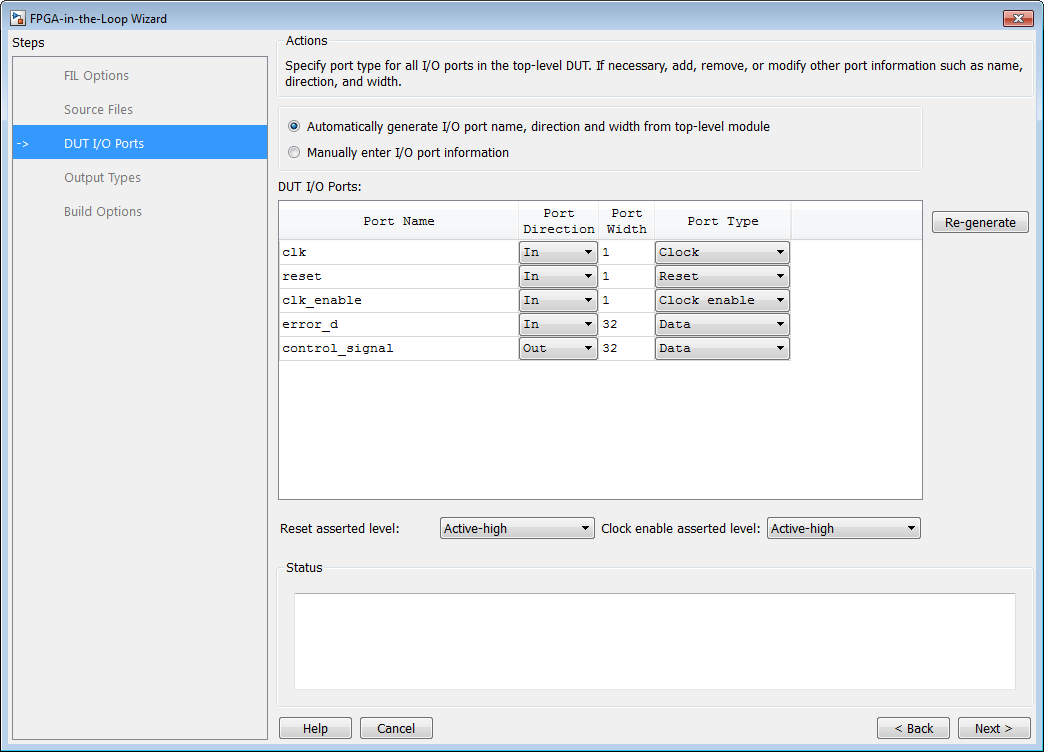

DUT I/O Ports ページ内:

ポートリストを確認します。FIL ウィザードは、トップレベルの HDL モジュールを解析してすべての I/O ポートを取得し、それらを DUT I/O ポート テーブルに表示します。パーサーはポート名からポート タイプを判別しようとします。ウィザードは、これらの信号を「ポート タイプ」の下に表示されます。

すべての入力/出力/リセット ポート/クロックが期待どおりにマッピングされていることを確認します。パーサーがポートに誤ったポート タイプを割り当てた場合は、手動で信号を変更できます。同期設計の場合は、クロック、リセット、または必要に応じてクロック有効化信号を指定します。このテーブルで指定されるポート タイプは、HDL コードと同じである必要があります。少なくとも 1 つの出力ポートが必要です。

信号を追加または削除するには、Manually enter port information を選択します。

Regenerate をクリックすると、元のポート定義 (HDL コードから) を含むテーブルが再ロードされます。

[Next] をクリックします。

手順 6: システムオブジェクトの出力タイプを指定する

(このページは FIL System object 用です。Simulink ブロック出力タイプについては、手順 6: FILブロックの出力タイプを指定する を参照してください。

Output Types ページ内:

出力データ型を指定します。ウィザードはデータ型を割り当てます。出力データ型が予想と異なる場合は、手動で型を変更します。

選択:

Fixedpoint整数Logical

データ型は指定されたビット幅によって異なります。

出力タイプを

Signed、Unsigned、またはFraction Lengthに指定できます。[Next] をクリックします。

手順 7: システムオブジェクトのビルドオプションを指定する

(このページは FIL System object 用です。Simulink については、手順 7: FILブロックのビルドオプションを指定する を参照してください。

Build Options ページ内:

出力ファイルのフォルダーを指定します。デフォルトのオプションを使用できます。通常、デフォルトは、現在のフォルダーの下にある、最上位モジュールにちなんで名付けられたサブフォルダーです。

Summary は、ISE プロジェクト ファイルと FPGA プログラミング ファイルの場所を表示します。FIL ブロック マスクの高度な操作には、これら 2 つのファイルが必要になる場合があります。

手順 8: ビルドを開始

Build をクリックして FIL System object の生成を開始します。

FIL ウィザードは次のファイルを生成します。

./フォルダーには、toplevel_fil/toplevel_programFPGA.mtoplevelは HDL トップレベルの名前です。このファイルには、FPGA プログラミング ファイルを FPGA にダウンロードするためのコードが含まれています。function toplevel_programFPGA %Load the bitstream in the FPGA filProgramFPGA('Xilinx', '/dir/mybitstream.bit', 1); endtoplevel_fil.mtoplevelは HDL トップレベルの名前です。このファイルには、hdlverifier.FILSimulationから派生したクラス定義が含まれており、プライベート プロパティを初期化します。このファイルは現在のフォルダにあります。以下は、

fft8という名前の DUT から FIL ウィザードを使用して生成されたクラス定義ファイルのサンプルです。classdef fft8_fil < hdlverifier.FILSimulation % fft8_fil is a filWizard generated class used for FPGA-In-the-Loop % simulation with the 'fft8' DUT. % fft8_fil connects MATLAB with a FPGA and cosimulate with it by % writing inputs in the FPGA and reading outputs from the FPGA. % % MYFIL = fft8_fil % % FIL syntax: % % [out1, out2, ...] = MYFIL(in1, in2, ...) connect to the FPGA, % write in1, in2, ... to the FPGA and read out1, out2, ... from % the FPGA % % fft8_fil methods: % % release - Allow property value and input characteristics changes, and % release connection to FPGA board % clone - Create fft8_fil object with same property values % isLocked - Locked status (logical) % programFPGA - Load the programming file in the FPGA % % fft8_fil properties: % % DUTName - DUT top level name % InputSignals - Input paths in the HDL code % InputBitWidths - Width in bit of the inputs % OutputSignals - Output paths in the HDL code % OutputBitWidths - Width in bit of the outputs % OutputDataTypes - Data type of the outputs % OutputSigned - Sign of the outputs % OutputFractionLengths - Fraction lengths of the outputs % OutputDownsampling - Downsampling factor and phase of the outputs % OverclockingFactor - Overclocking factor of the hardware % SourceFrameSize - Frame size of the source (only for HDL source block) % Connection - Parameters for the connection with the board % FPGAVendor - Name of the FPGA chip vendor % FPGABoard - Name of the FPGA board % FPGAProgrammingFile - Path of the Programming file for the FPGA % ScanChainPosition - Position of the FPGA in the JTAG scan chain % % File Name: fft8_fil.m % Created: 26-Apr-2012 18:18:06 % % Generated by FIL Wizard properties (Nontunable) DUTName = 'fft8'; end methods function obj = fft8_fil %THE FOLLOWING PROTECTED PROPERTIES ARE SPECIFIC TO THE HW DUT %AND MUST NOT BE EDITED (RERUN THE FIL WIZARD TO CHANGE THEM) obj.InputSignals = char('Xin_re','Xin_im'); obj.InputBitWidths = [10,10]; obj.OutputSignals = char('Xout_re','Xout_im'); obj.OutputBitWidths = [13,13]; obj.Connection = char('UDP','192.168.0.2','00-0A-35-02-21-8A'); obj.FPGAVendor = 'Xilinx'; obj.FPGABoard = 'XUP Atlys Spartan-6 development board'; obj.ScanChainPosition = 1 ; %THE FOLLOWING PUBLIC PROPERTIES ARE RELATED TO THE SIMULATION %AND CAN BE EDITED WITHOUT RERUNING THE FIL WIZARD obj.OutputSigned = [true,true]; obj.OutputDataTypes = char('fixedpoint','fixedpoint'); obj.OutputFractionLengths = [9,9]; obj.OutputDownsampling = [1,0]; obj.OverclockingFactor = 1; obj.SourceFramieSize = 1; obj.FPGAProgrammingFile = 'S:\MATLAB\demo\fft8_fil\fft8_fil.bit'; end end end

FIL ウィザードはコマンド ウィンドウを開きます。

このウィンドウでは、FPGA 設計ソフトウェアが合成、フィット、PAR、FPGA プログラミング ファイルの生成を実行します。

プロセスが完了すると、コマンド ウィンドウにウィンドウを閉じるように求めるメッセージが表示されます。

ステップ9:統合とシミュレーション

システムオブジェクトの作成

FIL ウィザードを使用して派生したクラス定義ファイルからカスタム FILSimulation System object を作成します。このコード スニペットは、クラスのインスタンスを作成し、すべてのプロパティを初期化します。

MYFIL = toplevel_fil

HDL ワークフロー アドバイザーから FIL System object を生成した場合、設定を調整する必要はほとんどありません。FIL ウィザードを使用して FIL System object を生成した場合は、いくつかの設定を調整する必要があります。次のいずれかの方法を使用して、書き込み可能なプロパティを調整できます。

set メソッドを使用してプロパティを変更します。

MYFIL.set('FPGAProgrammingFile','c:\work\filfiles')プロパティを直接設定します。

MYFIL.FPGAProgrammingFile='c:\work\filfiles'

toplevel_fil.m.mファイルを編集する場合、以前にワークスペースでオブジェクトをインスタンス化していた場合は、再度インスタンス化します。

オブジェクトのプロパティの詳細については、hdlverifier.FILSimulation を参照してください。

プログラミングファイルをFPGAにロードする

FPGA は、programFPGA 関数、または FIL System object の programFPGA メソッドのいずれかを使用してプログラムできます。ガイド付きハードウェアセットアップ をまだ実行していない場合は、プログラミング ファイルをロードする前に実行してください。

programFPGA関数:./toplevel_fil/toplevel_programFPGA

programFPGAメソッド:MYFIL.programFPGA

MYFILはFILSimulationオブジェクトのインスタンスです。

シミュレーションの実行

MATLAB コードで System object を呼び出します。

通常どおりに MATLAB コードを実行します。開始する前に必ず ガイド付きハードウェアセットアップ を実行してください。

オブジェクトへの最初の呼び出しにより、FPGA ボードとの通信が確立されます。