このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Enabled Subsystem

外部入力によって実行がイネーブルになるサブシステム

ライブラリ:

Simulink /

Ports & Subsystems

HDL Coder /

Ports & Subsystems

説明

Enabled Subsystem ブロックは、信号に正の値が含まれている場合に外部信号に基づいて実行される Subsystem ブロックです。Enabled Subsystem は、Enable 端子の外部信号が負から正の方向にゼロを横切ったときに実行されます。

Enabled Subsystem ブロックは、Enable ブロックを Subsystem ブロック内に配置することで構成されます。Enabled Subsystem の実行は、Enabled Subsystem ブロックの Enable 端子によって制御されます。

Enabled Subsystem ブロックを使用して以下をモデル化します。

サブシステム内のブロックの実行における不連続性。たとえば、条件付き実行サブシステムを使ったカウンター内のカウンター回路は、サブシステムが有効な間はインクリメントしますが、サブシステムが無効になるとその出力を保留します。

Enable 端子で正の制御信号を受け取ったときに実行される複数の Enabled Subsystem。例については、Enabled Subsystem を使用した制御アルゴリズムの実装、Enabled Subsystem のブロック状態と出力の制御、および信号のマージを参照してください。

例

Enabled Subsystem を使用した制御アルゴリズムの実装

この例では、Enabled Subsystem を使用してバイナリ論理信号に基づく制御アルゴリズムを実装する方法を示します。Enabled Subsystem は、バイナリ信号が正の値であり制御アルゴリズムを実装する場合に実行されます。この例では、スーパーツイスティング制御アルゴリズムを使用して、不安定な動的システムを安定させます。スーパーツイスティング アルゴリズムは、ロバスト性能でよく知られているスライディング モード制御手法の 1 つです。

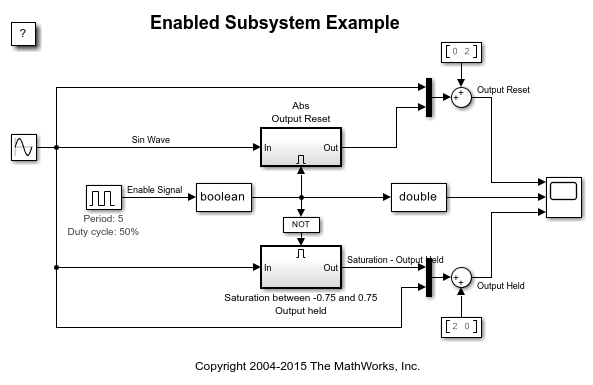

Enabled Subsystem のブロック状態と出力の制御

この例では、Enabled Subsystem ブロック内のブロックの状態を、Subsystem が無効化されたときにリセットまたは保持する方法と、Subsystem の出力を制御する方法を示します。この例では、離散制御信号と連続制御信号の両方について、状態と出力値の構成の 4 つの異なる組み合わせを見ていきます。Enabled Subsystem が無効化されたとき、次のような組み合わせが使用可能です。

条件付き実行サブシステムを使ったカウンター

この例では、Enabled Subsystem および Triggered Subsystem を使用してカウンターを実装する方法を示します。この例では、モデル sldemo_counters がタンクへの水の流れを制御し、オーバーフローの発生回数をカウンターでカウントします。タンクの水位が 30 秒以上にわたって 8 メートル以上になるとオーバーフローが発生します。

クラッチ ロックアップ モデルの作成

この例では、Simulink® を使用して回転クラッチ システムをモデル化およびシミュレーションする方法を示します。ロックアップ時にシステム ダイナミクスにおいてトポロジーが変化するため、クラッチ システムのモデル化は困難ですが、この例題では、Enabled Subsystem がこのような問題をいかに簡単に処理できるかを示します。クラッチ シミュレーションの作成において重要な Simulink モデル化概念を採用する方法を説明します。設計者は、動的に変化する可能性がある強い不連続性と制約を伴う多くのモデルにこうした概念を適用できます。

端子

入力

Subsystem ブロックへの信号入力。スカラー、ベクトルまたは行列として指定します。Inport ブロックをサブシステム内に配置することで、Subsystem ブロックへの外部入力端子が追加されます。端子ラベルは Inport ブロックの名前と一致します。

ローカル環境から信号を受信するには、Inport ブロックを使用します。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus | image

サブシステム内の Enable ブロックは、Subsystem ブロックに外部入力端子を追加し、ブロックを Enabled Subsystem ブロックにします。

データ型: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

出力

Subsystem ブロックからの信号出力。スカラー、ベクトルまたは行列として返されます。Outport ブロックをサブシステム内に配置することで、Subsystem ブロックへの外部出力端子が追加されます。端子ラベルは Outport ブロックの名前と一致します。

信号をローカル環境に送信するには、Outport ブロックを使用します。

データ型: half | single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | bus | image

パラメーター

ブロック パラメーターを対話形式で編集するには、プロパティ インスペクターを使用します。Simulink® ツールストリップから、[シミュレーション] タブの [準備] ギャラリーで [プロパティ インスペクター] を選択します。

メイン

Subsystem ブロック アイコンに端子ラベルを表示する方法を選択します。

なし— 端子ラベルを表示しません。FromPortIcon— 対応する端子アイコン上に信号名が表示される場合、Subsystem ブロック上に信号名を表示します。それ以外の場合は、端子のブロック名、またはブロック名が既定の名前の場合は端子番号を表示します。FromPortBlockName— Subsystem ブロック上に対応する端子のブロック名を表示します。SignalName— 端子に接続されている信号に名前が付いている場合、Subsystem ブロック上の信号の名前を表示します。それ以外の場合は、対応する端子のブロック名を表示します。

Subsystem ブロックでの端子ラベルの編集については、Edit Port Labels on Subsystem Blocksを参照してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | ShowPortLabels |

| 値: | 'FromPortIcon' (既定値) | 'FromPortBlockName' | 'SignalName' | 'none' |

サブシステムの内容へのユーザー アクセスを制御します。

ReadWrite— サブシステムの内容を開き、修正することができます。ReadOnly— サブシステムを開くことはできますが、修正することはできません。サブシステムがブロック ライブラリに存在する場合、サブシステムへのリンクを作成して開くことができます。また、サブシステムのローカル コピーを作成して変更することはできますが、アクセス許可や元のライブラリ インスタンスの内容を変更することはできません。NoReadOrWrite— サブシステムを開くことも修正することもできません。サブシステムがライブラリに存在する場合、モデルにあるサブシステムのリンクを作成することはできますが、サブシステムを開いたり、アクセス許可を変更したり、サブシステムのローカル コピーを作成したりすることはできません。

[読み取り/書き込みアクセス許可] パラメーターが [NoReadOrWrite] に設定されているサブシステムの内容を表示しようとしても、応答はありません。たとえば、そのようなサブシステムをダブルクリックしても、サブシステムは開かれず、メッセージも表示されません。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | Permissions |

| 値: | 'ReadWrite' (既定値) | 'ReadOnly' | 'NoReadOrWrite' |

サブシステムの実行中にエラーが発生した場合に呼び出される関数名を入力します。

2 つの引数が関数に渡されます。その引数は、サブシステムのハンドルと、エラー タイプを指定する文字ベクトルです。関数が指定されていない場合、サブシステムの実行によってエラーが発生すると、一般的なエラー メッセージが表示されます。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | ErrorFcn |

| 値: | '' (既定値) | function name in quotes |

| データ型: | char | string |

このサブシステムによって参照されるワークスペース変数名を解決するかどうかを選択します。

詳細については、記号の解釈および記号関連付けプロセスを参照してください。

すべて— ブロック パラメーター値と Simulink データ オブジェクト (Simulink.Signalオブジェクトなど) の指定に使用されるワークスペース変数など、このサブシステムが使用するワークスペース変数のすべての名前を解決します。ExplicitOnly— ブロックのパラメーター値、データ ストア メモリ (ここにはブロックは存在しません)、信号、"must resolve" というマークの付いた状態を指定するために使用されるワークスペース変数名だけを解決します。なし— ワークスペース変数名を解決しません。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | PermitHierarchicalResolution |

| 値: | 'All' (既定値) | 'ExplicitOnly' | 'None' |

再初期化イベント端子を表示するには、このパラメーターを選択します。端子を削除するには、このパラメーターの選択を解除します。

依存関係

このパラメーターを有効にするには、[Atomic サブシステムとして扱う] をオンにします。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | ShowSubsystemReinitializePorts |

| 値: | 'off' (既定値) | 'on' |

Atomic Subsystem を含むすべての人為的な代数ループを解消しようとします。

off— Atomic Subsystem を含むすべての人為的な代数ループを解消しません。on— Atomic Subsystem を含むすべての人為的な代数ループを解消しようとします。

依存関係

このパラメーターを有効にするには、[Atomic サブシステムとして扱う] をオンにします。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | MinAlgLoopOccurrences |

| 値: | 'off' (既定値) | 'on' |

コード生成

[コード生成] タブのパラメーターには、Simulink Coder™ または Embedded Coder® のライセンスが必要です。

atomic (非バーチャル) サブシステムに対して生成されるコード形式を選択します。

自動— モデル内に存在するサブシステムのインスタンスのタイプと数に基づいて、最適な形式が選択されます。インライン— 無条件にサブシステムがインライン化されます。再利用できない関数— [ファイル名オプション] が[自動]に設定されている場合、個々の関数がモデル ファイル内にパッケージ化されます。[ファイル名オプション] が別のファイル名を使用する[サブシステム名を使用]、[関数名を使用]、または[ユーザー指定]に設定されている場合、個々の関数が別々のファイルにパッケージ化されます。このように設定されたサブシステムは、関数インターフェイスパラメーターの設定に基づく引数をもつ関数を生成します。生成された関数とファイルには、それぞれ関数名およびファイル名 (拡張子なし)パラメーターを使用して名前を付けることができます。これらの関数は再呼び出し可能ではありません。

再利用可能な関数— モデルが複数のサブシステムのインスタンスを含む場合、サブシステムのコードの再利用を可能にする引数をもつ関数が生成されます。このオプションは、参照モデル全体にわたりサブシステムの複数のインスタンスを含むモデル参照階層の生成コードで、サブシステム コードの再利用を可能とする引数をもつ関数も生成します。この場合、サブシステムはライブラリに含まれていなければなりません。

詳細については、以下を参照してください。

個別のサブシステムのコードと実行可能ファイルの生成 (Simulink Coder)

インライン化されたサブシステム コードの生成 (Simulink Coder)

サブシステム コードを別々の関数およびファイルとして生成 (Simulink Coder)

モデル間で共有されるライブラリ サブシステムからの再利用可能なコードの生成 (Simulink Coder)

既定値はブロックの構成によって異なります。たとえば、Subsystem ブロックの既定値は [自動] です。CodeReuseSubsystem ブロックの既定値は [再利用可能な関数] です。

ヒント

サブシステムの複数のインスタンスを 1 つの再利用が可能な関数として表す場合、それぞれ

自動または[再利用可能な関数]として指定できます。それらのどちらか一方を使用するのが最適です。両方を使用すると、各指定につき 1 つずつ、2 つの再利用可能な関数が作成されます。これらの選択の結果は、再利用が不可能な場合にのみ異なります。[自動]を選択しても、サブシステム コードの関数やファイル名は制御できません。[再利用可能な関数]と自動のオプションは両方とも、サブシステムのインスタンスが複数存在するかどうかと、コードが再利用可能かどうかを判定しようとします。再利用が不可能な場合、以下のように各オプションの動作はそれぞれ異なります。[自動]はインライン化されたコードを生成し、インライン化が禁止されている場合は、サブシステムのインスタンスごとに別の関数を生成します。[再利用可能な関数]はモデル内のサブシステムのインスタンスごとに、引数をもつ別の関数を生成します。

生成コードがソース管理下にある場合に

[再利用可能な関数]を選択する場合は、[ファイル名オプション] を[サブシステム名を使用]、[関数名を使用]、[ユーザー指定]のいずれかに設定してください。この設定を行わないと、モデルを変更するたびにコード ファイルの名前が変更され、ファイルのソース管理ができません。[自動]または[インライン]以外のオプションとモデル コンフィギュレーション パラメーター [状態] を選択した場合、コード ジェネレーターは出力メソッドと更新メソッドを別々に生成します。コード ジェネレーターでは、[コード生成およびシミュレーション用に出力メソッドと更新メソッドを結合] の指定は考慮されません。

依存関係

このパラメーターではコード生成のために Simulink Coder のライセンスが必要です。

このパラメーターを有効にするには、[Atomic サブシステムとして扱う] をオンにします。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWSystemCode |

| 値: | 'Auto' | 'Inline' | 'Nonreusable function' | 'Reusable function' |

サブシステム用に生成される関数に名前を付ける方法を選択します。

Embedded Coder ライセンスをお持ちの場合、コンフィギュレーション パラメーターの [コード生成] 、 [識別子] ペインのオプションで関数名を制御できます。

自動— 既定の名前付けの規則、model_subsystem()modelはモデルの名前であり、subsystemはサブシステムの名前、または、コードが再使用される場合に同一のものの名前です。[関数のパッケージ化] パラメーターに

[再利用可能な関数]を選択し、モデル参照階層に再利用可能なサブシステムのインスタンスが複数含まれている場合に、サブシステムで再利用可能なコードを生成するには、[関数名オプション] を[自動]に設定しなければなりません。サブシステム名を使用— 関数名にサブシステム名を使用します。既定では、関数名は命名規則model_subsystemサブシステムがライブラリ ブロックにあり、そのサブシステムのパラメーター関数のパッケージ化が

[再利用可能な関数]に設定されている場合、[サブシステム名を使用]オプションを設定すると、コード ジェネレーターはそのサブシステムの関数名とファイル名に対してライブラリ ブロックの名前を使用します。ユーザー指定— [関数名] フィールドが有効になります。有効な C または C++ 関数名 (固有でなければならない) を入力します。

詳細については、サブシステム コードを別々の関数およびファイルとして生成 (Simulink Coder)を参照してください。

既定値はブロックの構成によって異なります。たとえば、Subsystem ブロックの既定値は [自動] です。CodeReuseSubsystem ブロックの既定値は [サブシステム名を使用] です。

依存関係

このパラメーターには Simulink Coder のライセンスが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]または[再利用可能な関数]に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWFcnNameOpts |

| 値: | 'Auto' | 'Use subsystem name' | 'User specified' |

サブシステム コードに対して、一意で有効な C または C++ 関数名を指定します。

Simulink Coder コード ジェネレーターで自動生成された名前を割り当てたり、サブシステム名を使用したりする代わりに、関数に特定の名前を割り当てるには、このパラメーターを使用します。詳細については、サブシステム コードを別々の関数およびファイルとして生成 (Simulink Coder)を参照してください。

依存関係

このパラメーターには Simulink Coder のライセンスが必要です。

このパラメーターを有効にするには、[関数名オプション] を

[ユーザー指定]に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWFcnName |

| 値: | '' (既定値) | function name in quotes |

| データ型: | char | string |

サブシステムに対して生成される関数の個々のファイルに名前を付ける方法を選択します。

自動— サブシステムの構成およびモデルにあるインスタンスの数によって、[自動]は異なる結果を返します。コード ジェネレーターがサブシステムに個別のファイルを "生成しない" 場合、サブシステムの親システムから生成されたコード モジュール内で、サブシステム コードが生成されます。サブシステムの親がモデル自体の場合、サブシステム コードは

model.cmodel.cpp[関数のパッケージ化] パラメーターに

[再利用可能な関数]を選択し、生成コードがソース管理下にある場合、[ファイル名オプション] に[自動]以外の値を指定することを検討してください。これにより、関係のないモデル変更によって生成されたファイル名が変更されるのを防止できます。これは、ソース管理を使用して構成を管理する場合に問題となる点です。[関数のパッケージ化] パラメーターに

[再利用可能な関数]を選択し、モデル参照階層に再利用可能なサブシステムのインスタンスが複数含まれている場合に、サブシステムで再利用可能なコードを生成するには、[ファイル名オプション] を[自動]に設定しなければなりません。

サブシステム名を使用— コード ジェネレーターは、サブシステム (またはライブラリ ブロック) 名をファイル名として使用して、別のファイルを生成します。[ファイル名オプション] を

[サブシステム名を使用]に設定すると、モデルに Model ブロックが含まれている場合、またはモデルのモデル参照ターゲットが生成されている場合に、サブシステムのファイル名はマングルされます。これらの状況で、サブシステムのファイル名はモデル名を前置したサブシステムの名前で構成されます。関数名を使用— コード ジェネレーターは [関数名オプション] により指定される関数名をファイル名として使用します。ユーザー指定— このオプションは [ファイル名 (拡張子なし)] テキスト入力フィールドを有効にします。コード ジェネレーターは入力された名前をファイル名として使用します。任意のファイル名を入力しますが、.cや.cpp(などの) 拡張子は含めないでください。このファイル名は一意である必要はありません。サブシステムのソース ファイル名は一意である必要はありませんが、循環的な依存状態になるような一意でない名前を付けることは避けなければなりません。たとえば、

sys_a.hにはsys_b.hが含まれ、sys_b.hにはsys_c.hが含まれ、sys_c.hにはsys_a.hが含まれます。

既定値はブロックの構成によって異なります。たとえば、Subsystem ブロックの既定値は [自動] です。CodeReuseSubsystem ブロックの既定値は [関数名を使用] です。

依存関係

このパラメーターには Simulink Coder のライセンスが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]または[再利用可能な関数]に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWFileNameOpts |

| 値: | 'Auto' | 'Use subsystem name' | 'Use function name' | 'User specified' |

指定するファイル名は、一意である必要はありません。ただし、循環的な依存状態になるような一意でない名前を付けることは避けてください。たとえば、sys_a.h には sys_b.h が含まれ、sys_b.h には sys_c.h が含まれ、sys_c.h には sys_a.h が含まれます。

詳細については、サブシステム コードを別々の関数およびファイルとして生成 (Simulink Coder)を参照してください。

依存関係

このパラメーターには Simulink Coder のライセンスが必要です。

このパラメーターを有効にするには、[ファイル名オプション] を

[ユーザー指定]に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWFileName |

| 値: | '' (既定値) | filename in quotes |

| データ型: | char | string |

生成される関数で引数を使用する方法を選択します。

void_void— 引数をもたない関数を生成し、グローバル変数でデータを渡します。以下に例を示します。void subsystem_function(void)

引数を許可 (最適化)— グローバル変数でデータを渡さずに引数を使用する関数を生成します。これを指定すると、グローバル RAM が節約されます。このオプションにより、コード サイズが削減され、実行速度が改善されます。また、コード ジェネレーターによりさらなる最適化が有効になります。以下に例を示します。void subsystem_function(real_T rtu_In1, real_T rtu_In2, real_T *rty_Out1)場合によっては、最適化されたコードの生成時に、コード ジェネレーターが引数をもつ関数を生成しない可能性があります。

引数を許可 (グラフィカル インターフェイスとの一致)— Subsystem グラフィカル ブロック インターフェイスに一致する引数を使用する関数インターフェイスを生成します。生成される関数インターフェイスは予測可能であり変更されません。予測可能なインターフェイスは、デバッグやコードのテスト、外部アプリケーションとの統合において有用である可能性があります。たとえば、モデルに 2 つの Inport ブロックと 2 つの Outport ブロックがある場合、生成される関数インターフェイスは次のようになります。void subsystem_function(real_T rtu_In1, real_T rtu_In2, real_T *rty_Out1, real_T *rty_Out2)

詳細については、以下を参照してください。

Reduce Global Variables in Nonreusable Subsystem Functions (Embedded Coder)

Generate Predictable Function Interface to Match Graphical Block Interface (Embedded Coder)

非バーチャル サブシステムのモジュラー関数コードの生成 (Embedded Coder)

依存関係

このパラメーターには Embedded Coder のライセンスと ERT ベースのシステム ターゲット ファイルが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | FunctionInterfaceSpec |

| 値: | 'void_void' (既定値) | 'Allow arguments (Optimized)' | 'Allow arguments (Match graphical interface)' |

Atomic Subsystem 用の内部データが親モデルから分離され、サブシステムに所有されているサブシステムの関数コードを生成します。

off— Atomic Subsystem 用の内部データが親モデルから分離され、サブシステムに所有されているサブシステムの関数コードを生成しません。on— Atomic Subsystem 用の内部データが親モデルから分離され、サブシステムに所有されているサブシステムの関数コードを生成します。サブシステムのデータ構造は、親モデルのデータ構造とは別に宣言されます。個別のデータをもつサブシステムは、独自のブロック I/O とDWorkデータ構造対をもちます。結果として、サブシステムに対して生成されたコードの方が、追跡とテストが容易になります。また、データを分離すると、データが複数のデータ構造に分割されるため、モデル全体のデータ構造の最大サイズが小さくなる傾向があります。

Atomic Subsystem の modular function コードを生成する方法の詳細は、非バーチャル サブシステムのモジュラー関数コードの生成 (Embedded Coder)を参照してください。

Atomic Subsystem にメモリ セクションを適用する方法の詳細は、Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder)を参照してください。

依存関係

このパラメーターには Embedded Coder のライセンスと ERT ベースのシステム ターゲット ファイルが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | FunctionWithSeparateData |

| 値: | 'off' (既定値) | 'on' |

サブシステムの初期化および終了関数へのメモリ セクションの適用方法を選択します。

モデルから継承— ルート モデルのメモリ セクションをサブシステムの関数コードに適用します。既定の設定— 任意のモデルレベルの仕様を無効にして、サブシステムのシステム コードにメモリ セクションを適用しません。モデルのメモリ セクションの 1 つをサブシステムに適用します。

ヒント

入力可能な値は、モデル コンフィギュレーションに対してメモリ セクションのどのようなパッケージを設定しているのかによって異なります。Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder)およびモデル コンフィギュレーション パラメーター: コード生成 (Simulink Coder)を参照してください。

パッケージを使用してモデルを構成していない場合、使用可能な値は

[モデルから継承]のみです。そうでない場合、このリストには[既定の設定]と、モデルのパッケージに含まれているすべてのメモリ セクションが表示されます。これらのオプションは、指定されたサブシステム モデルのメモリ セクションの設定を無効にする場合に利用できます。Atomic Subsystem にメモリ セクションを適用する方法の詳細は、Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder)を参照してください。

依存関係

このパラメーターには Embedded Coder のライセンスと ERT ベースのシステム ターゲット ファイルが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]または[再利用可能な関数]に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWMemSecFuncInitTerm |

| 値: | 'Inherit from model' (既定値) | 'Default' | model memory section in quotes |

Embedded Coder におけるサブシステムの実行関数へのメモリ セクションの適用方法を選択します。

モデルから継承— ルート モデルのメモリ セクションをサブシステムの関数コードに適用します。既定の設定— 任意のモデルレベルの仕様を無効にして、サブシステムのシステム コードにメモリ セクションを適用しません。モデルのメモリ セクションの 1 つをサブシステムに適用します。

ヒント

入力可能な値は、モデル コンフィギュレーションに対してメモリ セクションのどのようなパッケージを設定しているのかによって異なります。Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder)およびモデル コンフィギュレーション パラメーター: コード生成 (Simulink Coder)を参照してください。

パッケージを使用してモデルを構成していない場合、使用可能な値は

[モデルから継承]のみです。そうでない場合、このリストには[既定の設定]と、モデルのパッケージに含まれているすべてのメモリ セクションが表示されます。これらのオプションは、指定されたサブシステム モデルのメモリ セクションの設定を無効にする場合に利用できます。Atomic Subsystem にメモリ セクションを適用する方法の詳細は、Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder)を参照してください。

依存関係

このパラメーターには Embedded Coder のライセンスと ERT ベースのシステム ターゲット ファイルが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]または[再利用可能な関数]に設定します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWMemSecFuncExecute |

| 値: | 'Inherit from model' (既定値) | 'Default' | model memory section in quotes |

サブシステムの定数へのメモリ セクションの適用方法を選択します。

モデルから継承— ルート モデルのメモリ セクションをサブシステム データに適用します。既定の設定— 任意のモデル レベルの仕様を無効にして、サブシステムのデータにメモリ セクションを適用しません。モデルのメモリ セクションの 1 つをサブシステムに適用します。

ヒント

指定したメモリ セクションが、生成されたコードの対応するグローバル データ構造体に適用されます。Atomic サブシステムに対して生成されるグローバル データ構造体の基本情報については、標準のデータ構造体 (Simulink Coder)を参照してください。

入力可能な値は、モデル コンフィギュレーションに対してメモリ セクションのどのようなパッケージを設定しているのかによって異なります。Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder)を参照してください。

パッケージを使用してモデルを構成していない場合、使用可能な値は

[モデルから継承]のみです。そうでない場合、このリストには[既定の設定]と、モデルのパッケージに含まれているすべてのメモリ セクションが表示されます。これらのオプションは、指定されたサブシステム モデルのメモリ セクションの設定を無効にする場合に利用できます。Atomic Subsystem にメモリ セクションを適用する方法の詳細は、Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder)を参照してください。

依存関係

このパラメーターには Embedded Coder のライセンスと ERT ベースのシステム ターゲット ファイルが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]に設定し、[別々のデータをもつ関数] パラメーターを選択します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWMemSecDataConstants |

| 値: | 'Inherit from model' (既定値) | 'Default' | model memory section in quotes |

サブシステムの内部データへのメモリ セクションの適用方法を選択します。

モデルから継承— ルート モデルのメモリ セクションをサブシステム データに適用します。既定の設定— 任意のモデル レベルの仕様を無効にして、サブシステムのデータにメモリ セクションを適用しません。モデルのメモリ セクションの 1 つをサブシステムに適用します。

ヒント

指定したメモリ セクションが、生成されたコードの対応するグローバル データ構造体に適用されます。Atomic サブシステムに対して生成されるグローバル データ構造体の基本情報については、標準のデータ構造体 (Simulink Coder)を参照してください。

入力可能な値は、モデル コンフィギュレーションに対してメモリ セクションのどのようなパッケージを設定しているのかによって異なります。Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder)を参照してください。

パッケージを使用してモデルを構成していない場合、使用可能な値は

[モデルから継承]のみです。そうでない場合、このリストには[既定の設定]と、モデルのパッケージに含まれているすべてのメモリ セクションが表示されます。これらのオプションは、指定されたサブシステム モデルのメモリ セクションの設定を無効にする場合に利用できます。Atomic Subsystem にメモリ セクションを適用する方法の詳細は、Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder)を参照してください。

依存関係

このパラメーターには Embedded Coder のライセンスと ERT ベースのシステム ターゲット ファイルが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]に設定し、[別々のデータをもつ関数] パラメーターを選択します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWMemSecDataInternal |

| 値: | 'Inherit from model' (既定値) | 'Default' | model memory section in quotes |

サブシステムのパラメーターへのメモリ セクションの適用方法を選択します。

モデルから継承— ルート モデルのメモリ セクションをサブシステムの関数コードに適用します。既定の設定— 任意のモデルレベルの仕様を無効にして、サブシステムのシステム コードにメモリ セクションを適用しません。モデルのメモリ セクションの 1 つをサブシステムに適用します。

ヒント

指定したメモリ セクションが、生成されたコードの対応するグローバル データ構造体に適用されます。Atomic サブシステムに対して生成されるグローバル データ構造体の基本情報については、標準のデータ構造体 (Simulink Coder)を参照してください。

入力可能な値は、モデル コンフィギュレーションに対してメモリ セクションのどのようなパッケージを設定しているのかによって異なります。Control Data and Function Placement in Memory by Inserting Pragmas (Embedded Coder)を参照してください。

パッケージを使用してモデルを構成していない場合、使用可能な値は

[モデルから継承]のみです。そうでない場合、このリストには[既定の設定]と、モデルのパッケージに含まれているすべてのメモリ セクションが表示されます。これらのオプションは、指定されたサブシステム モデルのメモリ セクションの設定を無効にする場合に利用できます。Atomic Subsystem にメモリ セクションを適用する方法の詳細は、Override Default Memory Placement for Subsystem Functions and Data (Embedded Coder)を参照してください。

依存関係

このパラメーターには Embedded Coder のライセンスと ERT ベースのシステム ターゲット ファイルが必要です。

このパラメーターを有効にするには、[関数のパッケージ化] を

[再利用できない関数]に設定し、[別々のデータをもつ関数] パラメーターを選択します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | RTWMemSecDataParameters |

| 値: | 'Inherit from model' (既定値) | 'Default' | model memory section in quotes |

サブシステム参照

参照するサブシステム ファイルを指定します。サブシステム参照の詳細については、モデルでの参照サブシステムの作成と使用を参照してください。

依存関係

このパラメーターにアクセスするには、[サブシステム参照] セクションで [変換] をクリックします。

サブシステムを参照サブシステムに変換する方法の詳細については、Convert Between Subsystems and Referenced Subsystemsを参照してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

| パラメーター: | ReferencedSubsystem |

| 値: | '' (既定値) | subsystem filename in quotes |

| データ型: | char | string |

ブロックの特性

拡張機能

実際のコード生成のサポートは、ブロックの実装に依存します。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

HDL コード生成をターゲットとするモデルで Enabled Subsystem を使用する場合、以下を検討することをお勧めします。

合成結果が Simulink の結果と一致するためには、イネーブル端子が FPGA で登録されたロジックによって (同期クロックを使用して) 駆動されなければなりません。

Enabled Subsystem 出力信号に単位遅延を含めます。こうすることで、コード ジェネレーターによって余分なバイパス レジスタが HDL コード内に挿入されることを回避できます。

Enabled Subsystem は以下の方法で合成結果に影響する可能性があります。

システム クロックの速度がわずかに低下する場合がある。

Enabled Subsystem インスタンスの数とサブシステムあたりの出力端子の数に対応して、生成コードでより多くのリソースが使用される。

| アーキテクチャ | 説明 |

|---|---|

Module (既定値) | サブシステムとそのサブシステム内のブロックのコードを生成します。 |

BlackBox | ブラック ボックス インターフェイスを生成します。生成された HDL コードには、サブシステムの入力/出力端子定義のみ含まれます。したがって、モデル内のサブシステムを使用して、手動作成された既存の HDL コードへのインターフェイスを生成できます。 サブシステムのブラックボックス インターフェイスの生成は、クロック信号を使用しない Model ブロック インターフェイスの生成と似ています。 |

| 生成されたコードからサブシステムを削除します。シミュレーションでサブシステムを使用できますが、HDL コード内では "ノーオペレーション" として扱います。 |

| 一般 | |

|---|---|

| AdaptivePipelining | 合成ツール、ターゲット周波数、乗算器の語長に基づくパイプラインの自動挿入。既定の設定は |

| BalanceDelays | あるパスに新しい遅延が導入されたことを検出し、それに一致する遅延を他のパスに挿入します。既定の設定は |

| ClockRatePipelining | パイプライン レジスタを低速のデータ レートではなく高速のクロック レートで挿入します。既定の設定は |

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| DistributedPipelining | パイプライン レジスタの分散、またはレジスタのリタイミング。既定の設定は |

| DSPStyle | 乗算器のマッピングの合成属性。既定の設定は |

| FlattenHierarchy | 生成された HDL コードからサブシステム階層を削除します。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| SharingFactor | 単一の共有リソースにマッピングされる、機能的に等価なリソースの数。既定の設定は 0 です。リソース共有 (HDL Coder)も参照してください。 |

| StreamingFactor | 時間多重化されてシリアルのスカラー データ パスに変換される、パラレル データ パスの数、またはベクトルの数。既定値は 0 であり、パラレル データ パスがそのまま実装されます。ストリーミング (HDL Coder)も参照してください。 |

ターゲット仕様

このブロックは DUT にできないため、[ターゲット仕様] タブのブロック プロパティ設定は無視されます。

HDL Coder は、次の条件を満たす Enabled Subsystem の HDL コード生成をサポートします。

Enabled Subsystem は DUT でない。

サブシステムのトリガー "および" 有効化が "どちらも" 行われていない。

イネーブル信号はスカラーである。

イネーブル信号の入力データ型は boolean である。

サブシステムの出力がバスの場合、出力端子の [初期条件] は 0 にする必要があります。

Enabled Subsystem のすべての入力および出力 (イネーブル信号も含め) が同じレートで実行される。

Enable ブロックの [出力端子の表示] パラメーターが

[オフ]に設定されている。Enable ブロックの [イネーブル時の状態] パラメーターが

[保持]に設定されている (つまり、イネーブル時に Enable ブロックは状態をリセットしない)。Enabled Subsystem の出力端子の [ディセーブル時の出力] パラメーターが

[保持]に設定されている (つまり、ディセーブル時に Enabled Subsystem は出力値をリセットしない)。DUT に以下のブロックが含まれている場合、

RAMArchitectureがWithClockEnableに設定されている。Dual Port RAM

Simple Dual Port RAM

Single Port RAM

Enabled Subsystem に以下のブロックが含まれていない。

CIC Decimation

CIC Interpolation

FIR Decimation

FIR Interpolation

Downsample

Upsample

HDL FIFO

HDL Cosimulation ブロック (HDL Verifier™)

Rate Transition

NR Polar Encoder および NR Polar Decoder (Wireless HDL Toolbox™)

hdlcoder_remove_redundant_logic のモデル例では、HDL コード生成で Enabled Subsystem を使用する方法を示します。例を開くには、次のように入力します。

openExample('hdlcoder/RemoveRedundantLogicGeneratedHDLCodeExample',... 'supportingFile','hdlcoder_remove_redundant_logic');

PLC コード生成

Simulink® PLC Coder™ を使用して構造化テキスト コードを生成します。

実際のデータ型のサポートは、ブロックの実装に依存します。

バージョン履歴

R2006a より前に導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)