モデルの解析と結果の表示

解析モードを選択し、解析オプションを設定し、解析を実行し、結果を表示する

設計モデルの妥当性を確認するには、Simulink® Design Verifier™ を使用します。モデルを更新する際に反復して解析を行い、潜在的なバグを回避します。まず、解析用にモデルを構成し、解析のために互換性をチェックし、テスト生成、プロパティ証明、設計エラー検出などの適切な解析モードを選択することで、検証の目的を達成します。パラメーター コンフィギュレーションを調整すると、各パラメーター範囲が解析に与える影響を確認することができます。解析を繰り返す場合、過去に生成したモデル表現を再利用することで、時間とリソースを節約することができます。

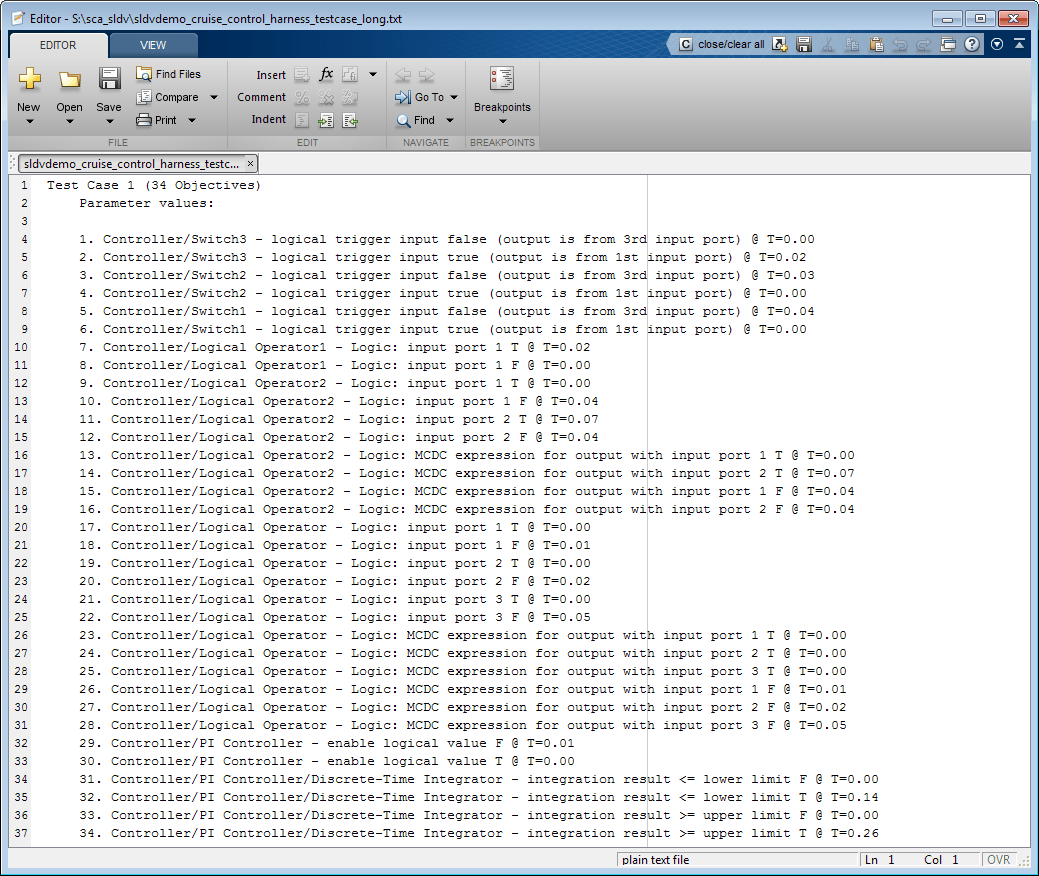

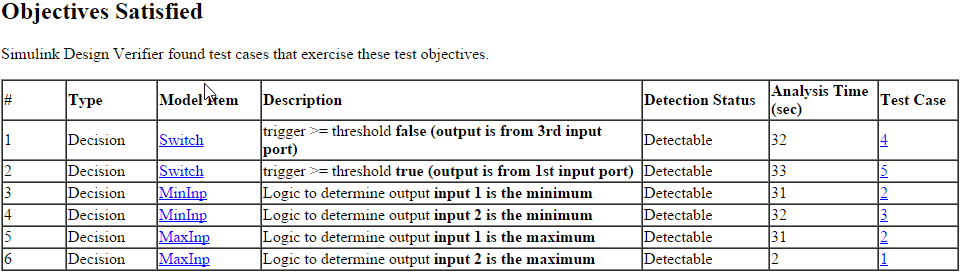

解析の実行後は、レポートを生成して、さらなるカスタム解析やレポート作成を行うための sldvData 構造体を含む MAT ファイルにアクセスできます。解析結果の詳細については、データ ファイルの解析結果の表示と解釈を参照してください。また、結果の概要に示されたオブジェクティブを解釈することもできますが、モデルの複雑度、サポートされていない機能、解析の制約により不完全な結果や未決定の結果がもたらされる場合があることに注意してください。

関数

トピック

モデル解析の基礎

- モデルの解析と結果の解釈

Simulink Design Verifier の解析の基礎を確認する。 - モデル検証の解析モードについて

Simulink Design Verifier の機能を説明する単純なモデルを解析します。

- モデルの解析オプションの構成

[コンフィギュレーション パラメーター] ダイアログ ボックスで、Simulink Design Verifier オプションを指定する。 - 解析のためのモデルの互換性チェック

モデルが Simulink Design Verifier と互換性があるかどうかをチェックします。 - モデル表現のオプションの構成

Simulink Design Verifier が解析に使用するモデル表現のオプションの設定方法について説明する。 - 自動スタブによる非互換性処理

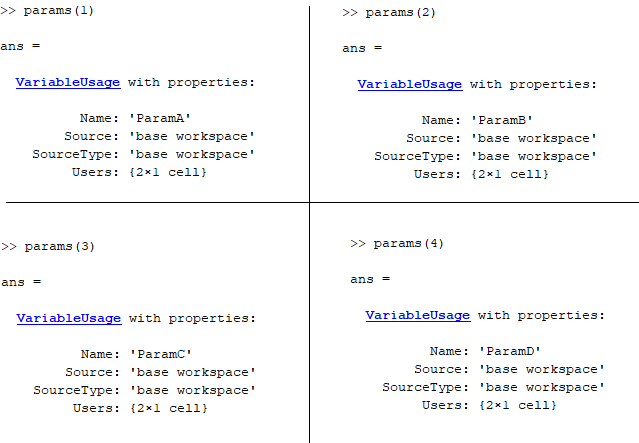

自動スタブの使用方法。 - Use Parameter Configuration in Analysis

Parameter configuration for Simulink Design Verifier analysis. - 解析を高速化するための Simulink キャッシュ ファイルの共有

Simulink キャッシュ ファイルを使用した解析のためのモデル表現の共有と再利用。 - Analyze Models in Parallel Using Parallel Computing Toolbox

Explains how to perform parallel analysis on multiple models using parallelfor-loop. - Resume an Incomplete Analysis

Simulink Design Verifier now automatically saves the state of an incomplete analysis, and allows you to resume later without restarting the analysis.

解析結果の解釈

- 解析結果のレビュー

Simulink Design Verifier の [結果の概要] ウィンドウで解析結果をレビューする。 - データ ファイルの解析結果の表示と解釈

Simulink Design Verifier データ ファイルのコンテンツを表示する。 - Understanding Objective Statuses

Simulink Design Verifier reports each verification condition as an objective with a status and supporting details. - View the Simulink Design Verifier Report

Simulink Design Verifier report summarizes analysis results, including errors, test cases, and verification outcomes for your model. - 解析レポートの結果の確認

Simulink Design Verifier レポートの解析結果を確認する。 - モデルにおける結果の強調表示

色分け強調表示をモデルの要素に適用して、解析結果を表示する。 - テスト シミュレーションのためのハーネス モデルの使用

基本的なハーネス モデルを作成して使用する。 - Analyze and Resolve Undecided Objective Statuses

Address undecided objectives obtained after Simulink Design Verifier analysis. - Approximations During Model Analysis

Manage approximations that Simulink Design Verifier performs before beginning its analysis.