解析のためのモデルの互換性チェック

Simulink® Design Verifier™ では、モデルを解析する前に、モデルが解析に対して互換性があるかどうかをチェックします。次の場合に、モデルは解析に対して互換性があります。

モデルが実行可能形式にコンパイルされている場合。

モデルがコード生成と互換性がある場合。

モデルがエラーのない 0 秒シミュレーション (シミュレーションの開始時間と終了時間が

0) を実行する場合。

このソフトウェアは、モデルにおいて Simulink および Stateflow® ソフトウェアの機能を広くサポートします。ただし、本製品でサポートされていない機能もあります。Simulink ソフトウェア機能に対する Simulink Design Verifier の制限事項とSimulink Design Verifier の Stateflow 機能の制限事項に説明があります。

サポートされている Simulink ブロックの詳細については、解析でサポートされていない Simulink ブロックを参照してください。

互換性チェックの実行

解析の開始前に、ソフトウェアでは、モデルの互換性がチェックされ、モデル表現が作成されます。モデル表現には、解析時に使用されるモデル アーティファクトが含まれています。詳細については、Reuse Model Representation for Analysisを参照してください。

解析を開始する前に、次のいずれかの方法を使用してモデルの互換性チェックを実行できます。このいずれかの方法を使用すると、モデル表現は常に再作成されます。

[Design Verifier] タブの [解析] セクションで、[互換性の確認] をクリックします。

モデル アドバイザーで、[製品別] 、 [Simulink Design Verifier] 、 [Simulink Design Verifier との互換性をチェック] を選択するか、[タスク別] 、 [Simulink Design Verifier 互換性チェック] 、 [Simulink Design Verifier との互換性をチェック] を選択します。[このチェックを実行] をクリックします。

詳細については、解析のモデル アドバイザー チェックを参照してください。

コマンド ラインまたは MATLAB® プログラムで、互換性チェックをプログラム実行する場合は、関数

sldvcompatを使用します。詳細については、sldvcompatを参照してください。subsystem の互換性をチェックするには、subsystem を右クリックし、[アプリの選択] にカーソルを合わせて [Design Verifier] ボタン

をクリックすることで、Design Verifier アプリ オプションをメニューに追加します。次に、[Design Verifier アプリ] セクションで、[サブシステムの互換性チェック] ボタン

をクリックすることで、Design Verifier アプリ オプションをメニューに追加します。次に、[Design Verifier アプリ] セクションで、[サブシステムの互換性チェック] ボタン  をクリックします。subsystem がバーチャルの場合、バーチャル サブシステムを atomic subsystem に変換し、サブシステムの互換性をチェックします。virtual subsystem を Atomic サブシステムに変換するには、virtual subsystem を右クリックし、[Atomic] を選択します。

をクリックします。subsystem がバーチャルの場合、バーチャル サブシステムを atomic subsystem に変換し、サブシステムの互換性をチェックします。virtual subsystem を Atomic サブシステムに変換するには、virtual subsystem を右クリックし、[Atomic] を選択します。

互換性チェックの結果

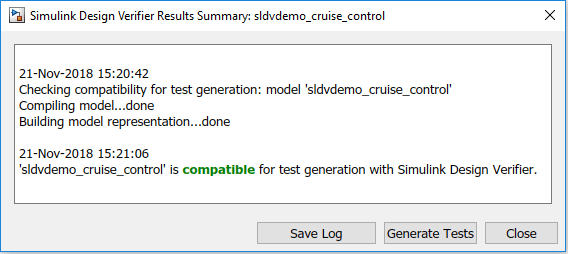

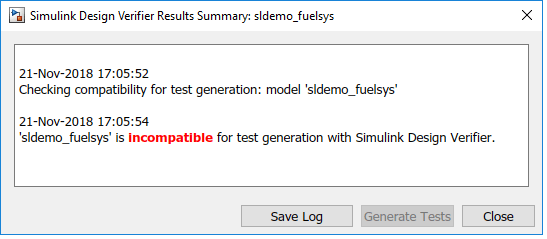

モデルの互換性チェックを実行すると、[結果の概要] ウィンドウに次のいずれかの結果が表示されます。

モデルが互換

モデルが互換である場合は、[結果の概要] ウィンドウで解析を続行できます。たとえば、テスト生成解析を続行するには、[テストの生成] をクリックします。

メモ

互換性チェックを完了後に、モデルを変更した場合は、[結果の概要] ウィンドウで解析を続行できません。モデルを変更した場合は、解析用に互換性チェックを再実行します。

モデルが非互換

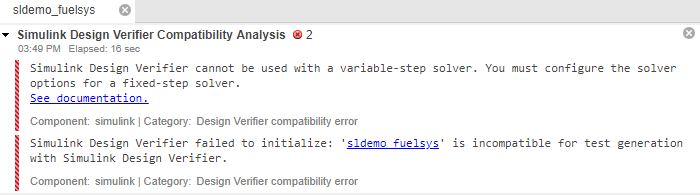

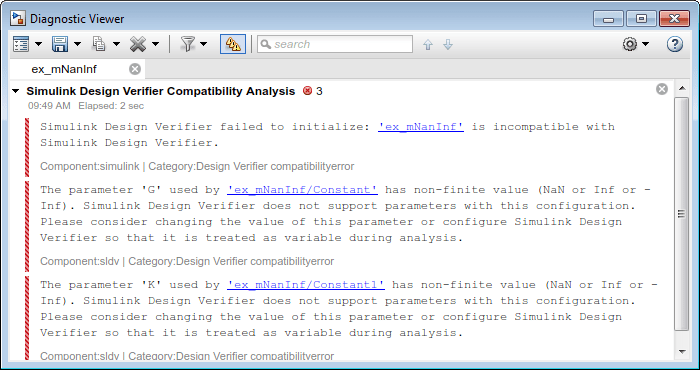

モデルが Simulink Design Verifier と互換性がない場合は、診断ビューアーのメッセージを介して非互換を特定し、修正できます。詳細については、エラーと警告の系統的診断を参照してください。

モデルが可変ステップ ソルバーを使用している場合は、ソルバーのタイプを

[固定ステップ]にします。

モデルに非有限データがある場合、データの値を変更するか、Simulink Design Verifier 解析時にそのデータが変数として扱われるようにモデルを構成します。詳細については、Simulink ソフトウェア機能に対する Simulink Design Verifier の制限事項を参照してください。

モデルが大規模で、多くのサブシステムが含まれる場合、テスト生成アドバイザーを使用して、特定のサブシステムが非互換性の原因となるかどうかを判定できます。詳細については、テスト生成アドバイザーによる解析可能コンポーネントの特定を参照してください。