デッド ロジック解析に対する結果の解析

この例は、ProtectedDivde モデルを使用して、デッド ロジックの原因となる可能性がある要因を特定する方法を示します。デッド ロジックの検出では、モデル要素が非アクティブで残される原因となる、モデル内の到達不可能なオブジェクティブを見つけます。

ワークフロー

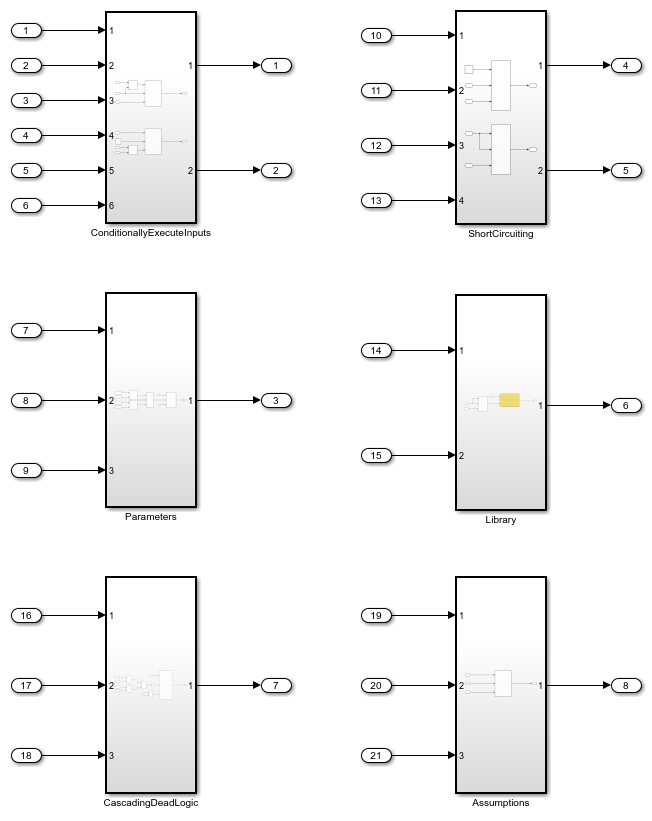

ProtectedDivde モデルは、モデルでデッド ロジックの原因となりやすいいくつかの一般的なパターンを示しています。モデル内の 6 つのサブシステムは、さまざまなパターンを表しています。このサブシステムは次のとおりです。

サブシステムの条件付き実行

解析時の Logical Operator ブロックのショートサーキット

定数として処理されるパラメーター値

ライブラリにリンクされたブロック

上流のブロック

信号の範囲の制限

デッド ロジック解析の実行

デッド ロジック解析を実行するには、次の手順に従います。

1.モデル ProtectedDivde を開きます。

open_system('ProtectedDivde');

2.[アプリ] ペインで [Design Verifier] を開きます。

3.[Design Verifier] タブで [エラーの検出設定] をクリックします。

4.[コンフィギュレーション パラメーター] ダイアログ ボックスで、次を行います。

a. [デッド ロジック (一部)] オプションを有効にします。

b. [網羅的解析を実行] オプションが選択されている場合、オフにします。

c. [解析するカバレッジ オブジェクティブ] を [条件判定] オプションに設定します。ドロップダウン メニューから選択できるオプションは、[判定]、[条件判定]、および [MCDC] です。

5.[Design Verifier] タブで [設計エラーの検出] をクリックします。

結果の解析およびレビュー

デッド ロジックについてモデルが解析され、結果が [結果の概要] ウィンドウに表示されます。結果から、44 のオブジェクティブ中 19 がデッド ロジックであることがわかります。

サブシステム ブロックでの解析結果の強調表示

このセクションでは、ProtectedDivde モデルでデッド ロジックを引き起こす一般的なパターンについて説明します。[結果の概要] ウィンドウで、[解析結果をモデル上で強調表示] をクリックします。デッド ロジックがあるサブシステムは赤で強調表示されます。このサブシステムは次のとおりです。

ConditionallyExecuteInputs

ShortCircuiting

パラメーター

ライブラリ

CascadingDeadLogic

ConditionGreaterThan0

ProtectedDivde モデルのサブシステムで、これらのパターンを説明します。赤色で強調表示されている各 Subsystem ブロックに、赤いデッド ロジックがあります。各サブシステムを 1 つずつ解析し、結果を強調表示することを検討します。

1. サブシステムの条件付き実行

モデルに "Switch" ブロックまたは "Multiport Switch" ブロックが含まれている場合、[条件付き入力分岐実行] パラメーターがオンに設定されていると、条件付き実行によって予期しないデッド ロジックが発生することがよくあります。ConditionallyExecuteInputs サブシステムを開き、赤で強調表示された AND ブロックをクリックします。[結果] ウィンドウにデッド ロジックの概要が示されます。

このサブシステムで、[条件付き入力分岐実行] パラメーターが On に設定されています。AND Logical Operator ブロックは条件付きで実行され、これによりサブシステムのデッド ロジックが発生します。

2. 解析時の Logical Operator ブロックのショートサーキット

Simulink Design Verifier は、デッド ロジックの解析時にショートサーキットが発生しているかのように論理ブロックを処理します。ShortCircuiting サブシステムを開き、赤で強調表示された AND ブロックをクリックします。[結果] ウィンドウにデッド ロジックの概要が示されます。

このモデルでは、In3 が false の場合、ショートサーキットが原因で 3 番目の入力が無視されます。これは、[結果] ウィンドウでデッド ロジックの考えられる説明として提示されます。

3. 定数として処理されるパラメーター値

モデルにパラメーターが含まれている場合、既定の設定で、Simulink Design Verifier はその値を定数として処理します。これが原因となってモデルでデッド ロジックが生じることがあります。この場合、これらのパラメーターが解析時に調整されるように設定することを検討してください。ShortCircuiting サブシステムを開き、赤で強調表示された Switch ブロックをクリックします。[結果] ウィンドウにデッド ロジックの概要が示されます。

ここでは、すべてのパラメーターがゼロに設定されています。これにより、Less Than ブロックのデッド ロジックが発生します。

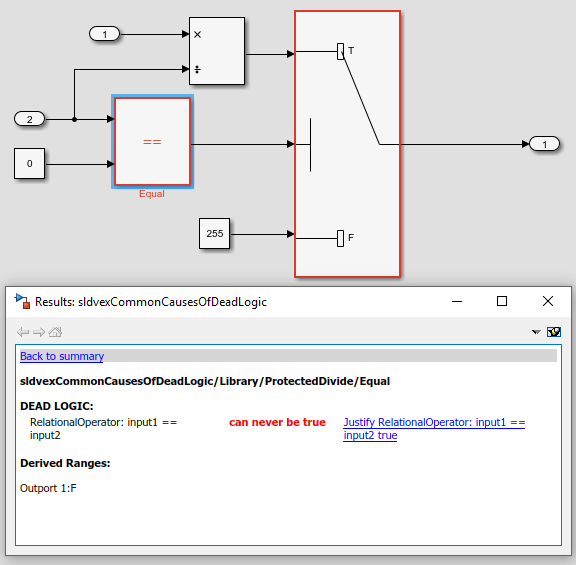

4. ライブラリにリンクされたブロック

ProtectedDivide ライブラリ サブシステムには、ゼロ除算に対する保護があります。ライブラリ ブロックは、使用される場所によっては、冗長化された防御的条件を伴って書き込まれる可能性があります。場合によっては、このためにデッド ロジックが発生することがあります。Library ブロックを開き、赤色で強調表示された ProtectedDivide サブシステムをクリックします。この場合、ProtectedDivide ライブラリ サブシステムへの入力がゼロ除算になることはありません。そのため、保護ロジックがデッドとなります。Equal ブロックにデッド ロジックが示されます。[結果] ウィンドウにデッド ロジックの概要が示されます。

これらのライブラリ ブロックから発生するデッド ロジックの正当化を検討してください。

5.上流のブロック

特定のブロックにデッド ロジックがあると、下流のブロックにもデッド ロジックが発生し、カスケード効果につながる場合がよくあります。CascadingDeadLogic サブシステムを開き、赤で強調表示された Less Than ブロックをクリックします。[結果] ウィンドウにデッド ロジックの概要が示されます。

Less Than ブロックのデッド ロジックにより、対応する下流のブロックでデッド ロジックが発生します。このため、多くの場合、下流のデッド ロジックを確認する前に上流のデッド ロジックを確認すると有効です。

6.信号の範囲の制限

最小値および最大値を制約としてもつルートレベルの Inport ブロックと、テスト生成の Test Condition ブロックは、デッド ロジックの原因となることがあります。たとえば、2 番目の Inport ブロックに最小値と最大値の範囲がそれぞれ 1 と 100 である ConditionGreaterThan0 Switch ブロックについて考えます。これによって、このサブシステムの Switch ブロックにデッド ロジックが生じます。これは、制約された範囲が、信号が常に 0 より大きい値になることを意味するためです。

解析レポートのビュー

[結果の概要] ウィンドウで [HTML] をクリックして、詳細な解析レポートを表示します。レポートには、モデルのすべてのデッド ロジックの結果が要約されます。

デッド ロジックについて網羅的解析を実行するには、[コンフィギュレーション パラメーター] ウィンドウの [設計エラー検出] ペインで、[網羅的解析を実行] を選択します。詳細な解析結果は、Simulink Design Verifier のデータ ファイル内の DeadLogic field に格納されます。このデータ ファイルを使用して、さらに結果を解析できます。

メモ: 欠陥チェッカーでは、デッド ロジック、範囲外配列アクセス、ゼロ除算、整数オーバーフロー、および指定された最小値と最大値の違反のチェックが自動的に呼び出されます。チェックを指定するには、欠陥チェッカーをオフに設定します。

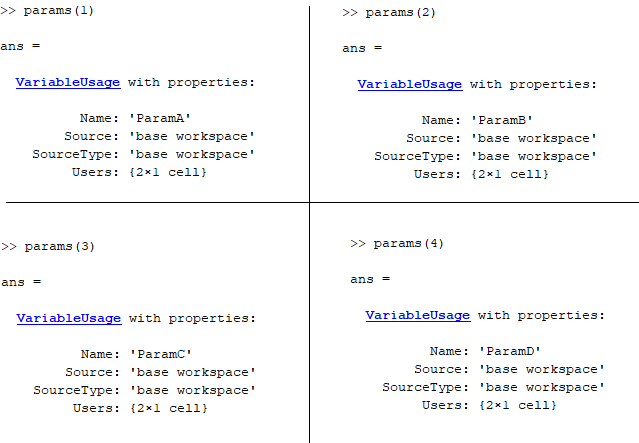

モデル スライサーを使用したブロックに対するパラメーターの影響の確認

次の手順を実行すると、モデル スライサーを使用して特定のブロックに影響を与える可能性のあるパラメーターを確認できます。

a. モデル スライサーを使用して SLSlicerAPI.ParameterDependence のオブジェクトを作成します。

slicerObj = slslicer('ProtectedDivde');

pd = slicerObj.parameterDependence;

b. "Product" ブロックに影響を与えるパラメーターを見つけます。

params = parametersAffectingBlock(pd, 'ProtectedDivde/Divide');

上の図には、Product ブロックに影響を与える関数 "parametersAffectingBlock" で返されたパラメーターが示されています。関数で返されるパラメーターのリストは、調整用と考えることができます。

c. クリーンアップ操作を実行してモデルのコンパイル状態を終了します。

slicerObj.terminate;