階層設計と同期ハードウェアの動作

HDL Coder ブロック ライブラリには、Simulink® モデル化環境に追加して、HDL アルゴリズムを開発できる多くのブロックが含まれます。大規模な設計のモデル化を行うには、モデルをサブシステムに分割して階層設計を作成します。同期ハードウェアの動作についてとハードウェア親和型の HDL コードを生成するには、サブシステム内部の State Control ブロックを使用します。

Simulink ライブラリ ブラウザーを絞り込んで HDL でサポートされたブロックのみを表示するには、「hdllib」と入力します。この節に記載されているブロックには、[HDL Coder] ライブラリでのみ使用可能なブロックが含まれます。Foreach Subsystem および Atomic Subsystem などのブロックは、ライブラリ ブラウザーの [Simulink] ライブラリにあります。

HDL コード生成でサポートされている Simulink ブロックのフィルターされたリストについては、Simulink ブロックのリスト (HDL コード生成) を参照してください。

関数

hdllib | HDL コード生成と互換性のあるブロックを表示する |

チェック

ブロック

トピック

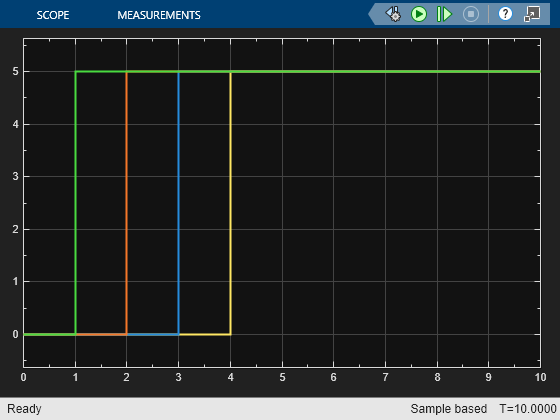

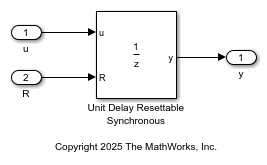

- State Control ブロックを使用する同期サブシステムの動作

State Control ブロック、およびより明確な HDL コードを生成する仕組みの説明。

- バス配列を使用するサブシステムの HDL コードの生成

設計でバス配列を使用するサブシステムの HDL コードを生成する。

- サブシステムで再利用可能なコードの生成

同一のサブシステムまたはマスク パラメーターの値以外が同一のサブシステムの共有コードを生成する。

- 参照モデルのパラメーター付きのコードの生成

モデル参照のモデル引数に VHDL®

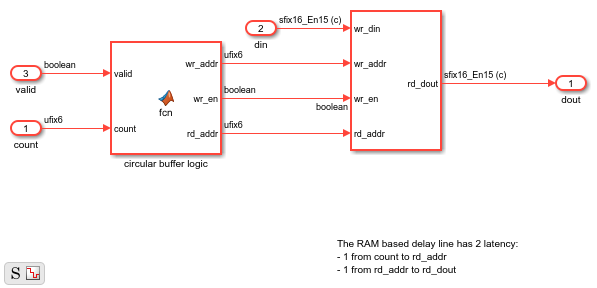

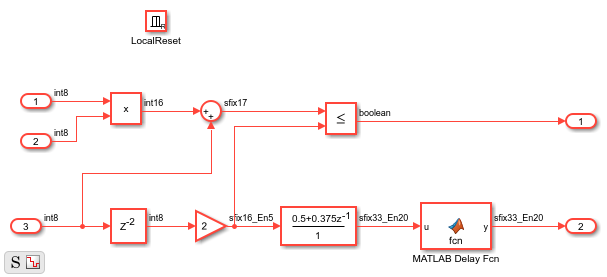

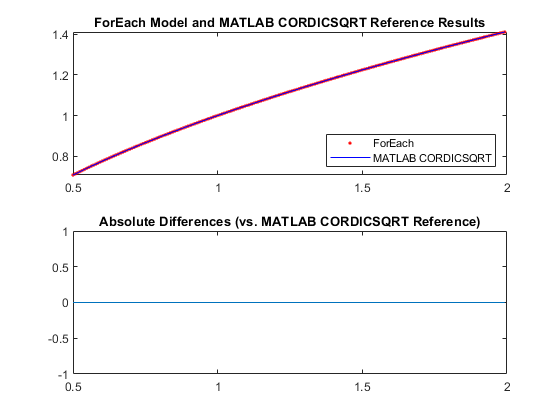

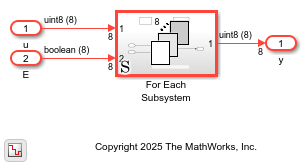

generic、Verilog® または SystemVerilogparameterを生成する。 - For Each Subsystem 内のブロックの HDL コードを生成

For Each Subsystem 内のブロックの HDL コードをモデル化して生成する方法を説明する例。

- HDL コード生成でのモデル参照

DUT サブシステム内のモデル参照により、以下が可能になります。

- Generate Incremental HDL Code for Referenced Models

When incremental code is generated for referenced models.

- Set Configuration Parameters for HDL Code Generation of Model Hierarchies

Satisfy model reference hierarchy requirements to enable HDL code generation.

- Generate HDL Code with Record or Structure Types for Bus Signals

Generate VHDL code with record or structure types for bus signals at different subsystem-level interfaces.