State Control ブロックを使用する同期サブシステムの動作

State Control ブロックとは

状態をもち、サブシステム内にイネーブル端子またはリセット端子をもつブロックがある場合、State Control ブロックの [同期] モードを使用して次を行います。

ハードウェア上の効率的なイネーブルおよびリセットのシミュレーション動作を提供します。

より明確な HDL コードを生成し、ハードウェア上のリソース使用を減らします。

State Control ブロックは、モデルの階層構造における任意のレベルで Simulink® モデルに追加できます。State Control ブロックの設定方法は、状態をもつサブシステム内の他のブロックのシミュレーション動作に影響します。

同期ハードウェア シミュレーション動作の場合、[状態制御] を

[同期]に設定します。既定の Simulink シミュレーション動作の場合、[状態制御] を

[クラシック]に設定します。

State Control ブロックのモード

| 機能 | 同期モード | クラシック モード |

|---|---|---|

State Control ブロック設定 | HDL Subsystems ブロック ライブラリからブロックを追加する場合の既定のブロック設定。 | シミュレーション動作は State Control ブロックを使用しないサブシステムと同じです。 |

Simulink シミュレーション動作

| update メソッドは状態を更新するだけです。output メソッドはタイム ステップごとに出力値を計算します。 たとえば、Enabled Subsystem がある場合、イネーブル信号が低位のときは新しい入力値が処理されるため、出力値は変化します。イネーブル信号が高位の場合、出力値は | update メソッドは状態を更新し、出力値を計算します。 たとえば、Enabled Subsystem がある場合、出力値はイネーブル信号が低位のときは安定し、イネーブル信号が高位になるときにのみ変化します。 |

HDL シミュレーション動作 | ハードウェア上でより効率的。 | ハードウェア上でより非効率的。 |

HDL コード生成の動作 | 生成される HDL コードはよりクリーンであり、ハードウェア上のリソース使用が少ない。 たとえば、Enabled Subsystem がある場合、HDL Coder™ は状態更新のたびにバイパス レジスタを生成せず、ハードウェア リソースの使用が少なくなります。 | 生成される HDL コードはクリーンではなく、より多くのハードウェア リソースを使用する。 たとえば、Enabled Subsystem がある場合、HDL Coder は状態更新のたびにバイパス レジスタを生成し、より多くのハードウェア リソースを使用します。 |

State Control ブロックの使用条件の詳細については、State Controlを参照してください。

同期モードを使用したサブシステムの同期バッジ

Simulink モデル内のサブシステムが同期セマンティクスを使用しているかどうか確認するには、次を行います。

同期動作を示す記号 S はサブシステムに表示されます。

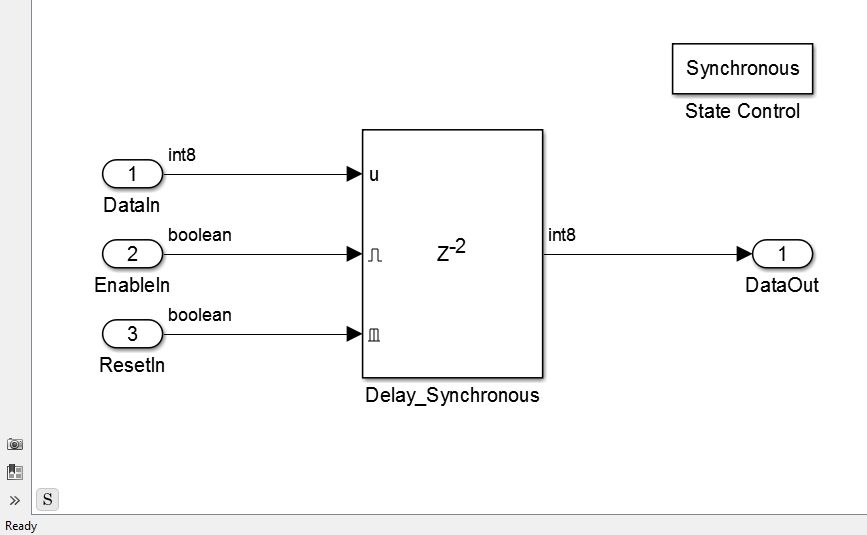

SynchronousStateControl サブシステムをダブルクリックすると、バッジ S が Simulink エディターに表示され、サブシステム内のブロックが同期ハードウェア セマンティクスを使用していることが示されます。

SynchronousStateControl サブシステムと ClassicStateControl サブシステムはそれぞれ [同期] モードと [クラシック] モードで外部リセットとイネーブル端子をもつ Delay ブロックを使用します。

State Control ブロックを使用した HDL コードの生成

次の表に、State Control ブロックの [クラシック] モードと [同期] モードにおいて Delay ブロックから生成された HDL コードの比較を示します。

| 機能 | 同期モード | クラシック モード |

|---|---|---|

HDL コード生成。適用した設定:

|

`timescale 1 ns / 1 ns

module SynchronousStateControl

(

clk,

reset,

enb,

DataIn,

EnableIn,

ResetIn,

DataOut

);

input clk;

input reset;

input enb;

input signed [7:0] DataIn; // int8

input EnableIn;

input ResetIn;

output signed [7:0] DataOut; // int8

reg signed [7:0] Delay_Synchronous_reg [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_reg_next [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_out1; // int8

always @(posedge clk)

begin : Delay_Synchronous_process

if (reset == 1'b1 || ResetIn == 1'b1) begin

Delay_Synchronous_reg[0] <= 8'sb00000000;

Delay_Synchronous_reg[1] <= 8'sb00000000;

end

else begin

if (enb && EnableIn) begin

Delay_Synchronous_reg[0] <= Delay_Synchronous_reg_next[0];

Delay_Synchronous_reg[1] <= Delay_Synchronous_reg_next[1];

end

end

end

assign Delay_Synchronous_out1 = Delay_Synchronous_reg[1];

assign Delay_Synchronous_reg_next[0] = DataIn;

assign Delay_Synchronous_reg_next[1] = Delay_Synchronous_reg[0];

assign DataOut = Delay_Synchronous_out1;

endmodule // SynchronousStateControl

|

`timescale 1 ns / 1 ns

module ClassicStateControl

(

clk,

reset,

enb,

DataIn,

EnableIn,

ResetIn,

DataOut

);

input clk;

input reset;

input enb;

input signed [7:0] DataIn; // int8

input EnableIn;

input ResetIn;

output signed [7:0] DataOut; // int8

reg signed [7:0] Delay_Synchronous_bypass; // sfix8

reg signed [7:0] Delay_Synchronous_reg [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_bypass_next; // sfix8

wire signed [7:0] Delay_Synchronous_reg_next [0:1]; // sfix8 [2]

wire signed [7:0] Delay_Synchronous_delay_out; // sfix8

wire signed [7:0] Delay_Synchronous_out1; // int8

always @(posedge clk)

begin : Delay_Synchronous_process

if (reset == 1'b1 || ResetIn == 1'b1) begin

Delay_Synchronous_bypass <= 8'sb00000000;

Delay_Synchronous_reg[0] <= 8'sb00000000;

Delay_Synchronous_reg[1] <= 8'sb00000000;

end

else begin

if (enb && EnableIn) begin

Delay_Synchronous_bypass <= Delay_Synchronous_bypass_next;

Delay_Synchronous_reg[0] <= Delay_Synchronous_reg_next[0];

Delay_Synchronous_reg[1] <= Delay_Synchronous_reg_next[1];

end

end

end

assign Delay_Synchronous_delay_out = (ResetIn == 1'b1 ? 8'sb00000000 :

Delay_Synchronous_reg[1]);

assign Delay_Synchronous_out1 = (EnableIn == 1'b1 ? Delay_Synchronous_delay_out :

Delay_Synchronous_bypass);

assign Delay_Synchronous_bypass_next = Delay_Synchronous_delay_out;

assign Delay_Synchronous_reg_next[0] = DataIn;

assign Delay_Synchronous_reg_next[1] = Delay_Synchronous_reg[0];

assign DataOut = Delay_Synchronous_out1;

endmodule // ClassicStateControl

|