For Each Subsystem 内のブロックの HDL コードを生成

この例では、Simulink® モデルにある For Each Subsystem 内のブロックを使用する方法、および HDL コードを生成する方法を説明します。

For Each Subsystem を使用する理由

入力信号の個々の要素やサブ配列に対して同じアルゴリズムを繰り返し実行するには、For Each Subsystem ブロックを使用します。Subsystem 内のブロックのセットは、入力信号の個々の要素や等分に分割されたサブ配列に適用されるアルゴリズムを複製します。For Each Subsystem ブロックを使用すると、同じアルゴリズムをモデル化する Subsystem ブロックの複製を作成して接続する必要がありません。For Each Subsystem は次のようなものです。

モデルのシミュレーション時間を減少させるベクトル処理または 2 次元行列処理をサポートします。入力信号の個々の要素やサブ配列を同時に処理します。

生成された HDL コード内で for-generate ループを使用することで、コードの可読性を向上させます。for-generate ループはコードの行数を減少させます。これを使用しないと、大きなベクトル信号のコードが数百行におよぶことがあります。

すべてのデータ型、Simulink ブロック、および事前定義された System object、およびユーザー定義の System object に対する HDL コード生成をサポートします。

リソース共有やパイプラインなどの、ブロックおよびブロック内の最適化をサポートします。指定された最適化と For Each Subsystem の並列処理の機能の組み合わせにより、ターゲット FPGA デバイスで高いパフォーマンスが発揮されます。

For Each Subsystem を使用したモデル化

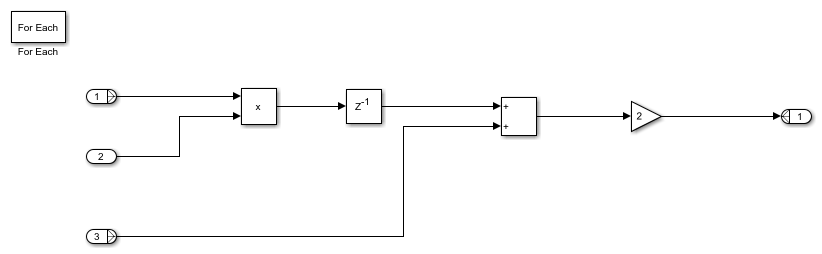

foreach_subsystem_example1 モデルを開きます。For Each Subsystem ブロックの内部でモデル化された、単純なアルゴリズムが表示されます。

モデルをシミュレートすると、入力信号 In1 および In3 がサブ配列に分割されて表示されます。この分割を表示するには、For Each ブロックをダブルクリックします。ブロックのパラメーター [分割の次元] および [分割幅] で、入力信号を分割する次元と各分割スライスの幅をそれぞれ指定します。指定した入力信号のサイズと分割に基づき、For Each Subsystem はアルゴリズムを計算するのに必要な反復の回数を決定します。

この例では、サイズが 8 の入力信号 In1 と In3 が、それぞれのサイズが 2 の 4 つのサブ配列に分割されています。サイズが 2 の入力信号 In2 は分割されていません。このアルゴリズムを計算するのに、For Each Subsystem は各反復で In1 と In3 の 4 つの各サブ配列に対してアルゴリズムを繰り返す 4 回の反復を必要とします。

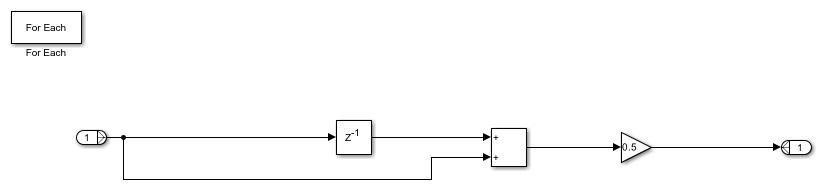

For Each Subsystem は、ベクトル化されたアルゴリズムのモデル化を簡略化します。この図は、複数のサブシステム インスタンスを作成することで同じアルゴリズムをモデル化するとどのようになるかを示しています。このモデルはグラフ的に複雑になり、メンテナンスが困難になる可能性があります。

行列入力信号の使用

For Each Subsystem は、HDL コード生成に対して 2 次元行列入力をサポートします。たとえば、foreach_subsystem_example2 モデルは単純なマルチチャネル フィルター演算を示しています。HDL コード生成は HDL DUT の入力端子と出力端子での行列に対してサポートされていないため、このモデルは DUT サブシステムの境界でチャネルを分離します。

For Each Subsystem は各チャネルのサンプルを平均化します。生成された HDL コードには For Each Subsystem 内のロジックのコピーが 3 つ含まれ、それぞれが 4 行 1 列のベクトルに対して演算を行います。

複素数データ信号の使用

HDL コード生成では、複素数データ型はブロックの入力としてサポートされていません。複素信号を入力するには、その信号を信号の配列に変換してからブロックに入力します。

信号の実数部と虚数部の両方に対して同じアルゴリズムを実行するには次のようにします。

Complex to Real-Imag ブロックを使用して、信号を実数部と虚数部に分けます。

Mux ブロックを使用して、実数部と虚数部で構成されるベクトル信号を作成します。

その後、このベクトルを For Each Subsystem ブロックに入力し、実数部と虚数部の両方について同じ計算を複製します。For Each Subsystem の出力でベクトル出力を複素信号に戻すことができます。Demux ブロックを使用して実数部と虚数部のスカラーに分け、それらのスカラーを Real-Imag to Complex ブロックに入力します。

HDL コードの生成

foreach_subsystem_example1 モデルで HDL コードを生成するには、Subsystem_Foreach ブロックを右クリックします。コンテキスト メニューに HDL Coder アプリのオプションを追加するには、[アプリの選択] をポイントし、[HDL Coder] をクリックします。次に、HDL Coder アプリのセクションで [サブシステムに対する HDL を生成] を選択します。

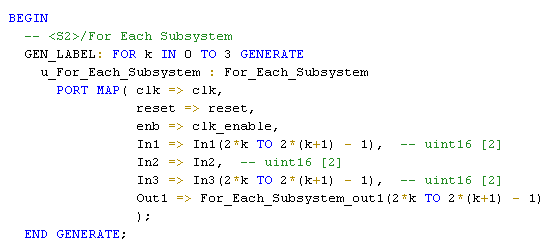

Subsystem_Foreach ブロックに対して生成された HDL コードを表示するには、MATLAB® コマンド ウィンドウで、Subsystem_Foreach.vhd ファイルをクリックします。VHDL® コードの抜粋内の HDL コードにこの for-generate ループがあります。このループは 4 つのサブシステム インスタンスを作成し、それぞれのインスタンスで入力 In1 と In3 のサイズ 2 のサブ配列に対してアルゴリズムを実行します。

For Each Subsystem がインスタンス化するサブシステムの内容を変更する最適化を指定できます。そのような場合、コード ジェネレーターは HDL コード内で for-generate ループを使用しません。以下のものがある場合、HDL コードは for-generate ループを含みません。

バスまたは複素数入力信号。

サブシステムにおけるリソース共有とストリーミングの最適化。

Verilog® コード内で非スカラー信号に分割されるベクトル入力。Verilog コード内で for-generate ループを得るには、ベクトル信号をスカラーに分割します。

For Each Subsystem アルゴリズムの最適化

For Each Subsystem に含まれるアルゴリズムを最適化するため、For Each Subsystem を含む DUT 上でリソース共有やストリーミングなどの最適化を有効にすることができます。たとえば、リソース共有最適化を使用すると、For Each Subsystem によって作成された複数の Subsystem インスタンスを共有できます。この最適化は、複数のインスタンスにわたって Subsystem でモデル化されるアルゴリズムを再利用することにより、ターゲット デバイス上の使用面積を削減します。

メモ: For Each Subsystem で最適化を有効にした場合、生成される HDL コードに for-generate ループは含まれません。

以下の例では、For Each Subsystem にリソース共有最適化を適用する方法を示します。リソースを共有するには、For Each Subsystem を含む Subsystem ブロックを選択し、[Sharing Factor] を指定します。この例では、Subsystem_Foreach ブロックを右クリックし、Simulink コンテキスト メニューの HDL Coder のセクションで、[HDL ブロック プロパティ] を選択します。この For Each Subsystem は 4 つのサブシステム インスタンスを生成するため、[Sharing Factor] を 4 に設定します。次に、この Subsystem_Foreach ブロックの HDL コードを生成します。

リソース共有最適化の効果を確かめるには、コマンド ラインで「gm_foreach_subsystem_example1」と入力し、生成したモデルを開きます。生成されたモデルから、最適化によって、For Each Subsystem によって生成された 4 つのサブシステム インスタンスが 1 つのサブシステム For Each Subsystem_Instance1 として共有されたことが分かります。

For Each Subsystem_Instance1 ブロックをダブルクリックすると、入力 In1 および In3 のサイズ 2 のサブ配列に対して計算されたアルゴリズムが表示されます。

リソース共有最適化の詳細については、リソース共有を参照してください。