HDL Coder での Resettable Subsystem のサポート

この例では、HDL Coder™ での Resettable Subsystem の使用方法を示します。

Resettable Subsystem の概要

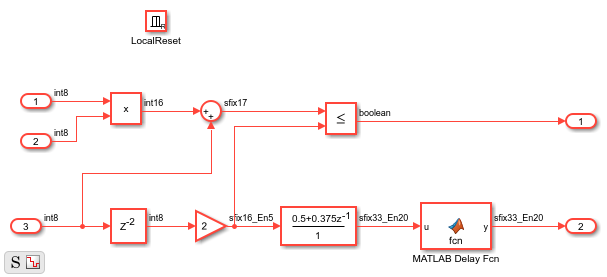

Resettable Subsystem は、サブシステム階層内のすべての状態を boolean 制御信号に基づいてリセットするサブシステムです。この場合、ステートフルな各ブロックに Simulink® でリセット信号を結線する必要はありません。この機能により、MATLAB Function ブロックなどの使用可能なリセット端子がないブロックをリセットできます。HDL Coder でのサポートでは、Resettable Subsystem がサポートされるのは同期状態制御領域内のみになります。

load_system('hdlcoder_resettable_subsystem'); open_system('hdlcoder_resettable_subsystem/DUT/Resettable Subsystem'); set_param('hdlcoder_resettable_subsystem', 'SimulationCommand', 'update');

Reset ブロック

Resettable Subsystem は、内部に専用の Reset Port ブロックがある Enabled Subsystem やその他の Simulink 条件付き実行サブシステムに似ています。この制御端子ブロックには、使用可能なトリガー タイプが複数あります。HDL Coder では、"レベル保持" トリガー タイプがサポートされます。

open_system('hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/LocalReset');

生成される HDL コードに対する Resettable Subsystem の効果

Resettable Subsystem では、サブシステム内の状態をもつすべてのブロックの状態を初期値にリセットできます。生成される HDL コードでは、設計上の各遅延 (Simulink で明示的にモデル化された遅延) にリセットが追加されます。パイプライン遅延などのハードウェア実装の遅延はリセットされません。リセット信号は同期信号であり、グローバル リセット信号からは完全に独立しています。

close_system('hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/LocalReset'); makehdl('hdlcoder_resettable_subsystem/DUT'); type hdlsrc/hdlcoder_resettable_subsystem/DUT.vhd

### Working on the model <a href="matlab:open_system('hdlcoder_resettable_subsystem')">hdlcoder_resettable_subsystem</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_resettable_subsystem/DUT')">hdlcoder_resettable_subsystem/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_resettable_subsystem', { 'HDL Code Generation' } )">hdlcoder_resettable_subsystem</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_resettable_subsystem'.

### Begin compilation of the model 'hdlcoder_resettable_subsystem'...

### Working on the model 'hdlcoder_resettable_subsystem'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_resettable_subsystem', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_resettable_subsystem'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_resettable_subsystem/gm_hdlcoder_resettable_subsystem.slx')">hdlsrc/hdlcoder_resettable_subsystem/gm_hdlcoder_resettable_subsystem.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_resettable_subsystem'.

### Working on hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/Discrete FIR Filter as hdlsrc/hdlcoder_resettable_subsystem/Discrete_FIR_Filter.vhd.

### Working on hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/MATLAB Delay Fcn as hdlsrc/hdlcoder_resettable_subsystem/MATLAB_Delay_Fcn.vhd.

### Working on hdlcoder_resettable_subsystem/DUT/Resettable Subsystem as hdlsrc/hdlcoder_resettable_subsystem/Resettable_Subsystem.vhd.

### Working on hdlcoder_resettable_subsystem/DUT as hdlsrc/hdlcoder_resettable_subsystem/DUT.vhd.

### Generating package file hdlsrc/hdlcoder_resettable_subsystem/DUT_pkg.vhd.

### Code Generation for 'hdlcoder_resettable_subsystem' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex72183536/hdlsrc/hdlcoder_resettable_subsystem', '/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex72183536/hdlsrc/hdlcoder_resettable_subsystem/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex72183536/hdlsrc/hdlcoder_resettable_subsystem/DUT_report.html

### HDL check for 'hdlcoder_resettable_subsystem' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

-- -------------------------------------------------------------

--

-- File Name: hdlsrc/hdlcoder_resettable_subsystem/DUT.vhd

-- Created: 2026-01-25 05:44:34

--

-- Generated by MATLAB 26.1, HDL Coder 26.1, and Simulink 26.1

--

--

-- -------------------------------------------------------------

-- Rate and Clocking Details

-- -------------------------------------------------------------

-- Model base rate: 1

-- Target subsystem base rate: 1

--

--

-- Clock Enable Sample Time

-- -------------------------------------------------------------

-- ce_out 1

-- -------------------------------------------------------------

--

--

-- Output Signal Clock Enable Sample Time

-- -------------------------------------------------------------

-- Out1 ce_out 1

-- Out2 ce_out 1

-- -------------------------------------------------------------

--

-- -------------------------------------------------------------

-- -------------------------------------------------------------

--

-- Module: DUT

-- Source Path: hdlcoder_resettable_subsystem/DUT

-- Hierarchy Level: 0

-- Model version: 20.0

--

-- -------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY DUT IS

PORT( clk : IN std_logic;

reset : IN std_logic;

clk_enable : IN std_logic;

LocalReset : IN std_logic;

In2 : IN std_logic_vector(7 DOWNTO 0); -- int8

In3 : IN std_logic_vector(7 DOWNTO 0); -- int8

In4 : IN std_logic_vector(7 DOWNTO 0); -- int8

ce_out : OUT std_logic;

Out1 : OUT std_logic;

Out2 : OUT std_logic_vector(32 DOWNTO 0) -- sfix33_En20

);

END DUT;

ARCHITECTURE rtl OF DUT IS

-- Component Declarations

COMPONENT Resettable_Subsystem

PORT( clk : IN std_logic;

reset : IN std_logic;

enb : IN std_logic;

In1 : IN std_logic_vector(7 DOWNTO 0); -- int8

In2 : IN std_logic_vector(7 DOWNTO 0); -- int8

In3 : IN std_logic_vector(7 DOWNTO 0); -- int8

LocalReset : IN std_logic;

Out1 : OUT std_logic;

Out2 : OUT std_logic_vector(32 DOWNTO 0) -- sfix33_En20

);

END COMPONENT;

-- Component Configuration Statements

FOR ALL : Resettable_Subsystem

USE ENTITY work.Resettable_Subsystem(rtl);

-- Signals

SIGNAL Resettable_Subsystem_Out1 : std_logic;

SIGNAL Resettable_Subsystem_Out2 : std_logic_vector(32 DOWNTO 0); -- ufix33

BEGIN

u_Resettable_Subsystem : Resettable_Subsystem

PORT MAP( clk => clk,

reset => reset,

enb => clk_enable,

In1 => In2, -- int8

In2 => In3, -- int8

In3 => In4, -- int8

LocalReset => LocalReset,

Out1 => Resettable_Subsystem_Out1,

Out2 => Resettable_Subsystem_Out2 -- sfix33_En20

);

Out1 <= Resettable_Subsystem_Out1;

Out2 <= Resettable_Subsystem_Out2;

ce_out <= clk_enable;

END rtl;

MATLAB Function ブロックには、明示的なリセット端子のサポートはありません。Resettable Subsystem に配置すると、HDL Coder により、関数内部の永続変数のリセットを制御するための外部の同期リセット信号が生成されます。

function y = fcn(u)

persistent state;

if isempty(state)

state = fi(0, 1, 33, 20);

endy = state; state = u; end

type hdlsrc/hdlcoder_resettable_subsystem/MATLAB_Delay_Fcn.vhd

-- -------------------------------------------------------------

--

-- File Name: hdlsrc/hdlcoder_resettable_subsystem/MATLAB_Delay_Fcn.vhd

-- Created: 2026-01-25 05:44:34

--

-- Generated by MATLAB 26.1, HDL Coder 26.1, and Simulink 26.1

--

-- -------------------------------------------------------------

-- -------------------------------------------------------------

--

-- Module: MATLAB_Delay_Fcn

-- Source Path: hdlcoder_resettable_subsystem/DUT/Resettable Subsystem/MATLAB Delay Fcn

-- Hierarchy Level: 2

-- Model version: 20.0

--

-- -------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY MATLAB_Delay_Fcn IS

PORT( clk : IN std_logic;

reset : IN std_logic;

enb : IN std_logic;

u : IN std_logic_vector(32 DOWNTO 0); -- sfix33_En20

LocalReset : IN std_logic;

y : OUT std_logic_vector(32 DOWNTO 0) -- sfix33_En20

);

END MATLAB_Delay_Fcn;

ARCHITECTURE rtl OF MATLAB_Delay_Fcn IS

-- Signals

SIGNAL u_signed : signed(32 DOWNTO 0); -- sfix33_En20

SIGNAL y_tmp : signed(32 DOWNTO 0); -- sfix33_En20

BEGIN

u_signed <= signed(u);

MATLAB_Delay_Fcn_1_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

y_tmp <= to_signed(0, 33);

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' THEN

IF LocalReset = '1' THEN

y_tmp <= to_signed(0, 33);

ELSE

y_tmp <= u_signed;

END IF;

END IF;

END IF;

END PROCESS MATLAB_Delay_Fcn_1_process;

y <= std_logic_vector(y_tmp);

END rtl;

MATLAB Function ブロックに実装された遅延に対する生成された VHDL コードに、LocalDelay という名前の同期遅延信号が追加されています。