Tapped Delay Enabled Resettable Synchronous

Delay scalar signal multiple sample periods and output all delayed versions when external Enable signal is true and external Reset signal is false

Since R2023a

Libraries:

HDL Coder /

Discrete

Description

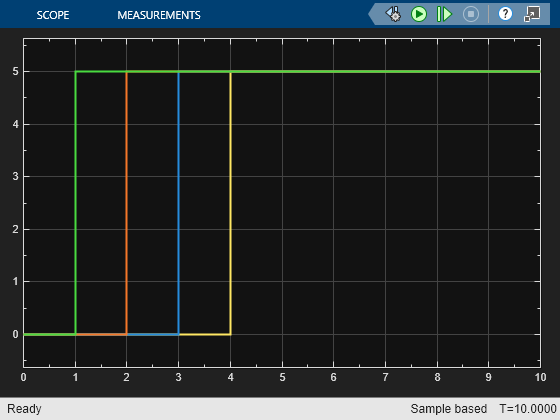

The Tapped Delay Enabled Resettable Synchronous block delays an input by the specified number of sample periods. The block returns an output signal for each delay when external Enable signal E is true and external Reset signal R is false.

For example, when you specify Number of delays as

4 and Order output starting with as

Oldest, the block returns four signals, the first delayed by four

sample periods, the second delayed by three, and so on. Use this block to discretize a signal

in time domain or resample a signal.

Output Vector Order

The block accepts one scalar input and generates an output vector that contains data for each incremental delay. Specify the order of the delayed signals in the output vector with the Order output vector starting with parameter:

Oldestorders the output vector starting with the oldest delay version and ending with the newest delay version.Newestorders the output vector starting with the newest delay version and ending with the oldest delay version.

Specify the output vector for the first sampling period with the Initial condition parameter. Careful selection of this parameter can mitigate unwanted output behavior.

Synchronous State Control

The block uses synchronous state control semantics. When you use this block in your

model and generate HDL code by using HDL Coder™, your model generates cleaner HDL code and uses fewer hardware resources due

to the Synchronous behavior of the block.

Examples

Limitations

The block does not support vector inputs on the Enable port.

You cannot use the block inside Enabled Subsystem, Triggered Subsystem, or Resettable Subsystem blocks that use

Classicsemantics. The Subsystem must useSynchronoussemantics.