このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

サブシステムで再利用可能なコードの生成

HDL Coder™ では、同一またはマスク パラメーターの値以外は同一の一部の Atomic サブシステムおよびバーチャル サブシステムから、再利用可能な HDL モジュールまたはエンティティを生成できます。再利用可能な HDL コードは、単一のファイルとして生成され、複数回インスタンス化されます。

Atomic サブシステムで再利用可能なコードの生成の要件

HDL Coder では、次の場合に Atomic サブシステムから再利用可能な HDL モジュールまたはエンティティを生成します。

DefaultParameterBehaviorモデル コンフィギュレーション パラメーターがInlinedである。このパラメーターは、コマンド ラインで、関数set_paramまたは関数hdlsetupを使用して設定できます。この設定を [コンフィギュレーション パラメーター] ダイアログ ボックスで指定するには、Simulink® Coder™ が必要です。メモ

hdlsetupを使用するとInlineParamsプロパティがonに設定されません。このパラメーターの有効化は、DefaultParameterBehaviorをInlinedに設定するのと同じです。InlineParamsをoffに設定すると、DefaultParameterBehaviorの値がTunableに変更されます。To Workspace ブロックや To File ブロックなどの信号ログ機能を使用していない。

Atomic サブシステムが同一であるか、マスク パラメーターの値以外は同一である。

再利用可能なサブシステムに異なる値のマスク パラメーターがある場合、関連するサブシステムまたはモデルの

MaskParameterAsGenericコンフィギュレーション パラメーターがonでなければなりません。このパラメーターはバーチャル サブシステムには影響しません。詳細については、Generate parameterized HDL code from masked subsystemを参照してください。調整可能なパラメーターを使用しているブロックが Constant、Gain、または Compare To Constant のみでなければなりません。

マスク パラメーターがスカラーでなければなりません。

マスク パラメーターのデータ型は、語長が 32 以下の整数または固定小数点でなければなりません。

端子およびパラメーターのデータ型が一致していなければなりません。

調整可能なマスク パラメーターの値を変更する場合に出力端子のデータ型が変わってはなりません。いずれかの Atomic サブシステムに異なる端子データ型があると、そのサブシステム用に生成されたコードも異なります。

バーチャル サブシステムで再利用可能なコードの生成の要件

HDL Coder では、次の場合にバーチャル サブシステムから再利用可能な HDL モジュールまたはエンティティを生成します。

DefaultParameterBehaviorコンフィギュレーション パラメーターがInlinedである。このパラメーターは、コマンド ラインで、関数set_paramまたは関数hdlsetupを使用して設定できます。この設定を [コンフィギュレーション パラメーター] ダイアログ ボックスで指定するには、Simulink Coder が必要です。メモ

hdlsetupを使用するとInlineParamsプロパティがonに設定されません。このパラメーターの有効化は、DefaultParameterBehaviorをInlinedに設定するのと同じです。InlineParamsをoffに設定すると、DefaultParameterBehaviorの値がTunableに変更されます。To Workspace ブロックや To File ブロックなどの信号ログ機能を使用していない。

SubsystemReuseコンフィギュレーション パラメーターがAtomic and Virtualに設定されている。SubsystemReuseをAtomic and Virtualに設定すると疑似代数ループ エラーが削減され、設計の他の部分のトポロジに関係なく同一のサブシステムの認識が向上します。同一サブシステムの同定はリソース共有に役立ちます。これらの値を設定するには、MATLAB コマンド ウィンドウで次のように入力します。

hdlset_param('myHDLModel', 'SubsystemReuse', 'Atomic and Virtual')

あるいは、[コンフィギュレーション パラメーター] ダイアログ ボックスの最上位の [HDL コード生成] ペインからこのオプションを設定できます。[グローバル設定] 、 [コーディング スタイル] で、[コードの再利用] パラメーターを必要なオプションに変更します。

前述のコマンドでは、

SubsystemReuseオプションがモデルに対して設定されます。このオプションを現在のコード生成セッションのみに対して設定するには、次のように入力します。makehdl(<DUT system>, 'SubsystemReuse', 'Atomic and Virtual')

バーチャル サブシステムが同一である。

調整可能なパラメーターを使用しているブロックが Constant、Gain、または Compare To Constant のみでなければなりません。

端子およびパラメーターのデータ型が一致していなければなりません。

パラメーターの値がサブシステム間で同一でなければなりません。

サブシステムで再利用可能なコードの生成

この例では、同一のサブシステムをもつモデルの HDL コード生成について示します。設計に同一のサブシステムが含まれる場合、HDL Coder はそのサブシステムに対して 1 つの HDL モジュールまたはエンティティを生成し、それを複数回インスタンス化します。

モデルを開く

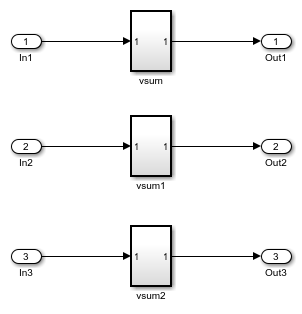

hdlcoder_reusable_code_identical_subsystem モデルを開いて、同一の 3 つのサブシステムを含む DUT サブシステムの例を表示します。

load_system('hdlcoder_reusable_code_identical_subsystem'); open_system('hdlcoder_reusable_code_identical_subsystem/DUT');

HDL コードの生成

関数makehdlを使用してモデルの HDL コードを生成できます。DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_reusable_code_identical_subsystem/DUT')

### Working on the model <a href="matlab:open_system('hdlcoder_reusable_code_identical_subsystem')">hdlcoder_reusable_code_identical_subsystem</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_reusable_code_identical_subsystem/DUT')">hdlcoder_reusable_code_identical_subsystem/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_reusable_code_identical_subsystem', { 'HDL Code Generation' } )">hdlcoder_reusable_code_identical_subsystem</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_reusable_code_identical_subsystem'.

### Begin compilation of the model 'hdlcoder_reusable_code_identical_subsystem'...

### Working on the model 'hdlcoder_reusable_code_identical_subsystem'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_reusable_code_identical_subsystem', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_reusable_code_identical_subsystem'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem/gm_hdlcoder_reusable_code_identical_subsystem.slx')">hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem/gm_hdlcoder_reusable_code_identical_subsystem.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem/gm_hdlcoder_reusable_code_identical_subsystem_vnl')">gm_hdlcoder_reusable_code_identical_subsystem_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_reusable_code_identical_subsystem'.

### Working on hdlcoder_reusable_code_identical_subsystem/DUT/vsum as hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem/vsum.vhd.

### Working on hdlcoder_reusable_code_identical_subsystem/DUT as hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem/DUT.vhd.

### Generating package file hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem/DUT_pkg.vhd.

### Code Generation for 'hdlcoder_reusable_code_identical_subsystem' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc25b_2988451_710120/tp11ca1a46/hdlcoder-ex21822210/hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem', '/tmp/Bdoc25b_2988451_710120/tp11ca1a46/hdlcoder-ex21822210/hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc25b_2988451_710120/tp11ca1a46/hdlcoder-ex21822210/hdl_prj/hdlsrc/hdlcoder_reusable_code_identical_subsystem/DUT_report.html

### HDL check for 'hdlcoder_reusable_code_identical_subsystem' complete with 0 errors, 0 warnings, and 2 messages.

### HDL code generation complete.

HDL Coder は、3 つのサブシステムに対して、1 つの VHDL® ファイル vsum.vhd を生成します。DUT サブシステム用に生成されたコード DUT.vhd には、vsum コンポーネントの 3 つのインスタンス化が含まれます。

ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT vsum PORT( In1 : IN vector_of_std_logic_vector16(0 TO 9); -- int16 [10] Out1 : OUT std_logic_vector(19 DOWNTO 0) -- sfix20 ); END COMPONENT;

-- Component Configuration Statements FOR ALL : vsum USE ENTITY work.vsum(rtl);

-- Signals SIGNAL vsum_out1 : std_logic_vector(19 DOWNTO 0); -- ufix20 SIGNAL vsum1_out1 : std_logic_vector(19 DOWNTO 0); -- ufix20 SIGNAL vsum2_out1 : std_logic_vector(19 DOWNTO 0); -- ufix20

BEGIN

u_vsum : vsum

PORT MAP( In1 => In1, -- int16 [10]

Out1 => vsum_out1 -- sfix20

);

u_vsum1 : vsum

PORT MAP( In1 => In2, -- int16 [10]

Out1 => vsum1_out1 -- sfix20

);

u_vsum2 : vsum

PORT MAP( In1 => In3, -- int16 [10]

Out1 => vsum2_out1 -- sfix20

);

Out1 <= vsum_out1;

Out2 <= vsum1_out1;

Out3 <= vsum2_out1;

END rtl;

調整可能なマスク パラメーターをもつ Atomic サブシステムで再利用可能なコードの生成

この例を使用して、調整可能なマスク パラメーターの値以外は同一の Atomic サブシステムを含む設計の HDL コードを生成できます。サブシステムに対して 1 つの HDL モジュールまたはエンティティを生成できます。生成されたコード内で、モジュールまたはエンティティが複数回インスタンス化されます。

モデルを開く

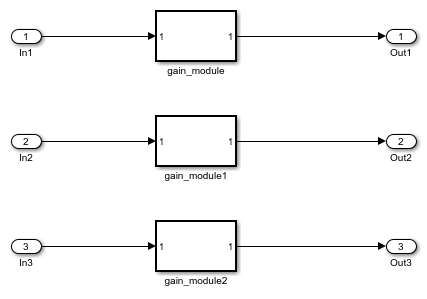

hdlcoder_reusable_code_parameterized_subsystem モデルは、調整可能なマスク パラメーター値以外は同一の Atomic サブシステムを含む DUT サブシステムの例を示しています。

load_system('hdlcoder_reusable_code_parameterized_subsystem'); open_system('hdlcoder_reusable_code_parameterized_subsystem/DUT');

hdlcoder_reusable_code_parameterized_subsystem/DUT 内で、ゲイン モジュールは調整可能なマスク パラメーターで表されるゲイン値をもつサブシステムです。ゲイン値は、gain_module は 4、gain_module1 は 5、gain_module2 は 7 です。

HDL コードの生成

同一の Atomic サブシステムに対して再利用可能なコードを生成するには、モデルに対して MaskParameterAsGeneric を有効にします。既定では MaskParameterAsGeneric は無効になっています。

調整可能なパラメーターをもつ Atomic サブシステムの再利用可能なコードの生成を有効にするには、hdlset_param関数を使用してモデルの MaskParameterAsGeneric オプションを on に設定します。

hdlset_param('hdlcoder_reusable_code_parameterized_subsystem','MaskParameterAsGeneric','on');

または、[コンフィギュレーション パラメーター] ダイアログ ボックスで、[HDL コード生成]、[グローバル設定]、[コーディング スタイル] タブを選択し、[マスクされたサブシステムからのパラメーター化された HDL コードの生成] パラメーターを有効にします。

makehdl関数を使用して MaskParameterAsGeneric を有効にし、DUT サブシステムの HDL コードを生成することもできます。

makehdl('hdlcoder_reusable_code_parameterized_subsystem/DUT','MaskParameterAsGeneric','on',... 'TargetLanguage','Verilog')

### Working on the model <a href="matlab:open_system('hdlcoder_reusable_code_parameterized_subsystem')">hdlcoder_reusable_code_parameterized_subsystem</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_reusable_code_parameterized_subsystem/DUT')">hdlcoder_reusable_code_parameterized_subsystem/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_reusable_code_parameterized_subsystem', { 'HDL Code Generation' } )">hdlcoder_reusable_code_parameterized_subsystem</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_reusable_code_parameterized_subsystem'.

### Begin compilation of the model 'hdlcoder_reusable_code_parameterized_subsystem'...

### Working on the model 'hdlcoder_reusable_code_parameterized_subsystem'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_reusable_code_parameterized_subsystem', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_reusable_code_parameterized_subsystem'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_reusable_code_parameterized_subsystem/gm_hdlcoder_reusable_code_parameterized_subsystem.slx')">hdlsrc/hdlcoder_reusable_code_parameterized_subsystem/gm_hdlcoder_reusable_code_parameterized_subsystem.slx</a>

### Begin Verilog Code Generation for 'hdlcoder_reusable_code_parameterized_subsystem'.

### Working on hdlcoder_reusable_code_parameterized_subsystem/DUT/gain_module as hdlsrc/hdlcoder_reusable_code_parameterized_subsystem/gain_module.v.

### Working on hdlcoder_reusable_code_parameterized_subsystem/DUT as hdlsrc/hdlcoder_reusable_code_parameterized_subsystem/DUT.v.

### Code Generation for 'hdlcoder_reusable_code_parameterized_subsystem' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc25b_2988451_710066/tpa22c8237/hdlcoder-ex53380017/hdlsrc/hdlcoder_reusable_code_parameterized_subsystem', '/tmp/Bdoc25b_2988451_710066/tpa22c8237/hdlcoder-ex53380017/hdlsrc/hdlcoder_reusable_code_parameterized_subsystem/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc25b_2988451_710066/tpa22c8237/hdlcoder-ex53380017/hdlsrc/hdlcoder_reusable_code_parameterized_subsystem/DUT_report.html

### HDL check for 'hdlcoder_reusable_code_parameterized_subsystem' complete with 0 errors, 1 warnings, and 0 messages.

### HDL code generation complete.

MaskParameterAsGeneric が有効な場合、HDL Coder は単一のソース ファイル gain_module.v を 3 つのゲイン モジュールのサブシステムに対して生成します。DUT サブシステム用に生成されたコード DUT.v には、gain_module コンポーネントの 3 つのインスタンス化が含まれます。

module DUT

(

In1,

In2,

In3,

Out1,

Out2,

Out3

);

input [7:0] In1; // uint8 input [7:0] In2; // uint8 input [7:0] In3; // uint8 output [31:0] Out1; // uint32 output [31:0] Out2; // uint32 output [31:0] Out3; // uint32

wire [31:0] gain_module_out1; // uint32 wire [31:0] gain_module1_out1; // uint32 wire [31:0] gain_module2_out1; // uint32

gain_module # (.myGain(4) ) u_gain_module (.In1(In1), // uint8 .Out1(gain_module_out1) // uint32 );

assign Out1 = gain_module_out1;

gain_module # (.myGain(5) ) u_gain_module1 (.In1(In2), // uint8 .Out1(gain_module1_out1) // uint32 );

assign Out2 = gain_module1_out1;

gain_module # (.myGain(7) ) u_gain_module2 (.In1(In3), // uint8 .Out1(gain_module2_out1) // uint32 );

assign Out3 = gain_module2_out1;

endmodule // DUT

gain_module.v 内で、myGain Verilog® パラメーターが調整可能なマスク パラメーター用に生成されます。

module gain_module

(

In1,

Out1

);

input [7:0] In1; // uint8 output [31:0] Out1; // uint32

parameter [31:0] myGain = 4; // ufix32

wire [31:0] kconst; // ufix32 wire [39:0] Gain_mul_temp; // ufix40 wire [31:0] Gain_out1; // uint32

assign kconst = myGain;

assign Gain_mul_temp = kconst * In1; assign Gain_out1 = Gain_mul_temp[31:0];

assign Out1 = Gain_out1;

endmodule // gain_module

入力モデルにマスク変数やマスク初期化コードなどのマスク情報を含むサブシステムがある場合、このようなサブシステムのマスク情報は生成されたモデルで保持されます。この情報が不要な場合は削除できます。