HDL Coder での State Control ブロックを使用した効率的なコードの生成

この例では、HDL Coder™ で State Control ブロックを使用してハードウェア親和型の HDL コードを生成する方法を示します。

State Control ブロックの概要

State Control ブロックは、それを含むサブシステムとその下の入れ子になったすべてのサブシステムに対する Simulink® のシミュレーション動作を変更するブロックです。これは、クロックで制御されるデジタル ハードウェアの同期動作について、特に状態をもつブロックでの明示的なイネーブル信号とリセット信号の使用をより厳密にモデル化することを目的としています。

State Control ブロックをサブシステムに配置し、そのパラメーターを Synchronous に設定すると、ハードウェアとの親和性が高い HDL コードが生成されます。サブシステムが同期モードの場合、S というグラフィックスのマークが左下に表示されます。State Control ブロックのパラメーターが Classic に設定されている場合は、サブシステムに State Control ブロックがない場合と同じ動作になります。

2 つのモードのシミュレーション動作にはわずかな違いしかありませんが、効率的な HDL コードを生成するうえで大きな意味をもちます。シミュレーション動作の違いは、主に明示的なリセット信号とイネーブル信号に関するものです。たとえば、同期モードでは、明示的なブロック リセット入力がブロック イネーブル入力信号よりも優先されます。

明示的なイネーブル入力端子をもつ Delay に対するクラシック モードの動作

HDL Coder で生成される HDL コードは、生成元のモデルと同じ動作をシミュレートします。この要件により、Classic State Control モードでは、特定の構造に対する生成コードで準最適なハードウェアが実装されます。たとえば、明示的なイネーブル入力をもつ Delay ブロックについて、Simulink のクラシック モードの動作を再現するために、モデル化されたレジスタに加えて、レジスタとマルチプレクサーで構成されるバイパス レジスタが生成されます。

Enabled_Delay.vhd の内容を調べて、追加のレジスタ信号とバイパス レジスタを確認します。

load_system('hdlcoder_statecontrol_model'); open_system('hdlcoder_statecontrol_model'); set_param('hdlcoder_statecontrol_model', 'SimulationCommand', 'update'); makehdl('hdlcoder_statecontrol_model/MAC FIR Block', 'TargetDirectory', 'hdlsrc_classic');

### Working on the model <a href="matlab:open_system('hdlcoder_statecontrol_model')">hdlcoder_statecontrol_model</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_statecontrol_model/MAC FIR Block')">hdlcoder_statecontrol_model/MAC FIR Block</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_statecontrol_model', { 'HDL Code Generation' } )">hdlcoder_statecontrol_model</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_statecontrol_model'.

### Begin compilation of the model 'hdlcoder_statecontrol_model'...

### Begin compilation of the model 'hdlcoder_statecontrol_model'...

### Working on the model 'hdlcoder_statecontrol_model'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_statecontrol_model', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_statecontrol_model'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc_classic/hdlcoder_statecontrol_model/gm_hdlcoder_statecontrol_model.slx')">hdlsrc_classic/hdlcoder_statecontrol_model/gm_hdlcoder_statecontrol_model.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_statecontrol_model'.

### Unused logic removed during HDL code generation. To highlight the logic removed, click the following MATLAB script: hdlsrc_classic/hdlcoder_statecontrol_model/highlightRemovedDeadBlocks.m

### To clear highlighting, click the following MATLAB script: hdlsrc_classic/hdlcoder_statecontrol_model/clearHighlightingRemovedDeadBlocks.m

### Working on hdlcoder_statecontrol_model/MAC FIR Block/Coeff ROM as hdlsrc_classic/hdlcoder_statecontrol_model/Coeff_ROM.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block/Enabled_Delay as hdlsrc_classic/hdlcoder_statecontrol_model/Enabled_Delay.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block/RAM delay line/circular buffer logic as hdlsrc_classic/hdlcoder_statecontrol_model/circular_buffer_logic.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block/RAM delay line/SimpleDualPortRAM_generic as hdlsrc_classic/hdlcoder_statecontrol_model/SimpleDualPortRAM_generic.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block/RAM delay line as hdlsrc_classic/hdlcoder_statecontrol_model/RAM_delay_line.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block as hdlsrc_classic/hdlcoder_statecontrol_model/MAC_FIR_Block.vhd.

### Generating package file hdlsrc_classic/hdlcoder_statecontrol_model/MAC_FIR_Block_pkg.vhd.

### Code Generation for 'hdlcoder_statecontrol_model' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3699846/tp6829dcca/hdlcoder-ex66924147/hdlsrc_classic/hdlcoder_statecontrol_model', '/tmp/Bdoc26a_3146167_3699846/tp6829dcca/hdlcoder-ex66924147/hdlsrc_classic/hdlcoder_statecontrol_model/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3699846/tp6829dcca/hdlcoder-ex66924147/hdlsrc_classic/hdlcoder_statecontrol_model/MAC_FIR_Block_report.html

### HDL check for 'hdlcoder_statecontrol_model' complete with 0 errors, 1 warnings, and 1 messages.

### HDL code generation complete.

type hdlsrc_classic/hdlcoder_statecontrol_model/Enabled_Delay.vhd

-- -------------------------------------------------------------

--

-- File Name: hdlsrc_classic/hdlcoder_statecontrol_model/Enabled_Delay.vhd

-- Created: 2026-01-25 05:40:44

--

-- Generated by MATLAB 26.1, HDL Coder 26.1, and Simulink 26.1

--

-- -------------------------------------------------------------

-- -------------------------------------------------------------

--

-- Module: Enabled_Delay

-- Source Path: hdlcoder_statecontrol_model/MAC FIR Block/Enabled_Delay

-- Hierarchy Level: 1

-- Model version: 19.0

--

-- -------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY Enabled_Delay IS

PORT( clk : IN std_logic;

reset : IN std_logic;

enb : IN std_logic;

din_re : IN std_logic_vector(33 DOWNTO 0); -- sfix34_En31

din_im : IN std_logic_vector(33 DOWNTO 0); -- sfix34_En31

LocalEnable : IN std_logic;

Out1_re : OUT std_logic_vector(33 DOWNTO 0); -- sfix34_En31

Out1_im : OUT std_logic_vector(33 DOWNTO 0) -- sfix34_En31

);

END Enabled_Delay;

ARCHITECTURE rtl OF Enabled_Delay IS

-- Signals

SIGNAL din_re_signed : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL din_im_signed : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL Enabled_Delay_bypass_delay_re : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL Enabled_Delay_bypass_delay_im : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL Enabled_Delay_reg_re : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL Enabled_Delay_reg_im : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL dout_re : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL dout_im : signed(33 DOWNTO 0); -- sfix34_En31

BEGIN

din_re_signed <= signed(din_re);

din_im_signed <= signed(din_im);

Enabled_Delay_1_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

Enabled_Delay_bypass_delay_re <= to_signed(0, 34);

Enabled_Delay_bypass_delay_im <= to_signed(0, 34);

Enabled_Delay_reg_re <= to_signed(0, 34);

Enabled_Delay_reg_im <= to_signed(0, 34);

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' AND LocalEnable = '1' THEN

Enabled_Delay_bypass_delay_im <= Enabled_Delay_reg_im;

Enabled_Delay_reg_im <= din_im_signed;

Enabled_Delay_bypass_delay_re <= Enabled_Delay_reg_re;

Enabled_Delay_reg_re <= din_re_signed;

END IF;

END IF;

END PROCESS Enabled_Delay_1_process;

dout_re <= Enabled_Delay_reg_re WHEN LocalEnable = '1' ELSE

Enabled_Delay_bypass_delay_re;

dout_im <= Enabled_Delay_reg_im WHEN LocalEnable = '1' ELSE

Enabled_Delay_bypass_delay_im;

Out1_re <= std_logic_vector(dout_re);

Out1_im <= std_logic_vector(dout_im);

END rtl;

明示的なイネーブル入力端子をもつ Delay に対する同期モードの動作

Synchronous State Control モードにある、明示的なイネーブルをもつ Delay ブロックについて、より効率的なハードウェアを作成する HDL コードが生成されます。実装にバイパス レジスタは含まれません。

Enabled_Delay_Sync.vhd を調べて、生成コードがクラシック モードの出力と比較して改善されたことを確認します。

makehdl('hdlcoder_statecontrol_model/MAC FIR Block Sync', 'TargetDirectory', 'hdlsrc_sync');

### Working on the model <a href="matlab:open_system('hdlcoder_statecontrol_model')">hdlcoder_statecontrol_model</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_statecontrol_model/MAC FIR Block Sync')">hdlcoder_statecontrol_model/MAC FIR Block Sync</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_statecontrol_model', { 'HDL Code Generation' } )">hdlcoder_statecontrol_model</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_statecontrol_model'.

### Begin compilation of the model 'hdlcoder_statecontrol_model'...

### Begin compilation of the model 'hdlcoder_statecontrol_model'...

### Working on the model 'hdlcoder_statecontrol_model'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_statecontrol_model', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_statecontrol_model'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc_sync/hdlcoder_statecontrol_model/gm_hdlcoder_statecontrol_model.slx')">hdlsrc_sync/hdlcoder_statecontrol_model/gm_hdlcoder_statecontrol_model.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_statecontrol_model'.

### Unused logic removed during HDL code generation. To highlight the logic removed, click the following MATLAB script: hdlsrc_sync/hdlcoder_statecontrol_model/highlightRemovedDeadBlocks.m

### To clear highlighting, click the following MATLAB script: hdlsrc_sync/hdlcoder_statecontrol_model/clearHighlightingRemovedDeadBlocks.m

### Working on hdlcoder_statecontrol_model/MAC FIR Block Sync/Coeff ROM as hdlsrc_sync/hdlcoder_statecontrol_model/Coeff_ROM.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block Sync/Enabled Delay Sync as hdlsrc_sync/hdlcoder_statecontrol_model/Enabled_Delay_Sync.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block Sync/RAM delay line/circular buffer logic as hdlsrc_sync/hdlcoder_statecontrol_model/circular_buffer_logic.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block Sync/RAM delay line/SimpleDualPortRAM_generic as hdlsrc_sync/hdlcoder_statecontrol_model/SimpleDualPortRAM_generic.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block Sync/RAM delay line as hdlsrc_sync/hdlcoder_statecontrol_model/RAM_delay_line.vhd.

### Working on hdlcoder_statecontrol_model/MAC FIR Block Sync as hdlsrc_sync/hdlcoder_statecontrol_model/MAC_FIR_Block_Sync.vhd.

### Generating package file hdlsrc_sync/hdlcoder_statecontrol_model/MAC_FIR_Block_Sync_pkg.vhd.

### Code Generation for 'hdlcoder_statecontrol_model' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3699846/tp6829dcca/hdlcoder-ex66924147/hdlsrc_sync/hdlcoder_statecontrol_model', '/tmp/Bdoc26a_3146167_3699846/tp6829dcca/hdlcoder-ex66924147/hdlsrc_sync/hdlcoder_statecontrol_model/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3699846/tp6829dcca/hdlcoder-ex66924147/hdlsrc_sync/hdlcoder_statecontrol_model/MAC_FIR_Block_Sync_report.html

### HDL check for 'hdlcoder_statecontrol_model' complete with 0 errors, 1 warnings, and 1 messages.

### HDL code generation complete.

type hdlsrc_sync/hdlcoder_statecontrol_model/Enabled_Delay_Sync.vhd

-- -------------------------------------------------------------

--

-- File Name: hdlsrc_sync/hdlcoder_statecontrol_model/Enabled_Delay_Sync.vhd

-- Created: 2026-01-25 05:40:53

--

-- Generated by MATLAB 26.1, HDL Coder 26.1, and Simulink 26.1

--

-- -------------------------------------------------------------

-- -------------------------------------------------------------

--

-- Module: Enabled_Delay_Sync

-- Source Path: hdlcoder_statecontrol_model/MAC FIR Block Sync/Enabled Delay Sync

-- Hierarchy Level: 1

-- Model version: 19.0

--

-- -------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY Enabled_Delay_Sync IS

PORT( clk : IN std_logic;

reset : IN std_logic;

enb : IN std_logic;

din_re : IN std_logic_vector(33 DOWNTO 0); -- sfix34_En31

din_im : IN std_logic_vector(33 DOWNTO 0); -- sfix34_En31

LocalEnable : IN std_logic;

Out1_re : OUT std_logic_vector(33 DOWNTO 0); -- sfix34_En31

Out1_im : OUT std_logic_vector(33 DOWNTO 0) -- sfix34_En31

);

END Enabled_Delay_Sync;

ARCHITECTURE rtl OF Enabled_Delay_Sync IS

-- Signals

SIGNAL din_re_signed : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL din_im_signed : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL dout_re : signed(33 DOWNTO 0); -- sfix34_En31

SIGNAL dout_im : signed(33 DOWNTO 0); -- sfix34_En31

BEGIN

din_re_signed <= signed(din_re);

din_im_signed <= signed(din_im);

Enabled_Delay_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

dout_re <= to_signed(0, 34);

dout_im <= to_signed(0, 34);

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' AND LocalEnable = '1' THEN

dout_re <= din_re_signed;

dout_im <= din_im_signed;

END IF;

END IF;

END PROCESS Enabled_Delay_process;

Out1_re <= std_logic_vector(dout_re);

Out1_im <= std_logic_vector(dout_im);

END rtl;

Enabled Subsystem

モデルに同期モードの Enabled Subsystem がある場合、その生成コードも改善されます。同期モードの Enabled Subsystem では、サブシステムの出力にバイパス レジスタが生成されません。さらに、Enabled Subsystem の内部の明示的なイネーブル入力をもつレジスタについても、上記と同じ改善が見られます。

MATLAB Function ブロックと同期モード

MATLAB Function ブロックを同期モードで使用するには、より正確な構成が必要になります。ブロックの入力から出力までの直接の連結パスがブロックに含まれている場合、直達を有効にしなければなりません。

プロパティ インスペクターを開きます。[モデル化] タブの [設計] セクションで、[プロパティ インスペクター] をクリックします。

MATLAB Function ブロックをクリックします。

[詳細設定] セクションを展開します。連結出力パスを含む各ブロックについて、[直達を許可] を選択します。

この設定により、MATLAB Function ブロックのコードに連結パスと順次パスの両方が含まれている場合に、そのブロックから同期モードでコードを生成できるようになります。

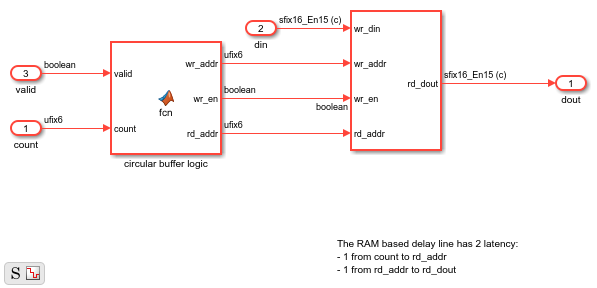

open_system('hdlcoder_statecontrol_model/MAC FIR Block Sync/RAM delay line') % open_system('hdlcoder_statecontrol_model/MAC FIR Block Sync/RAM delay line/circular buffer logic')

追加情報

State Control ブロックの詳細については、State Controlを参照してください。