Stateflow は、状態遷移図、フローチャート、状態遷移表、および真理値表を含むグラフィカル言語を提供する製品です。Stateflow を使用すると、MATLAB アルゴリズムや Simulink モデルが入力信号、イベント、および時間ベースの条件にどのように反応するかを説明できます。

Stateflow により、監視制御、タスク スケジューリング、障害管理、通信プロトコル、ユーザー インターフェイス、およびハイブリッドシステムを設計および開発できます。

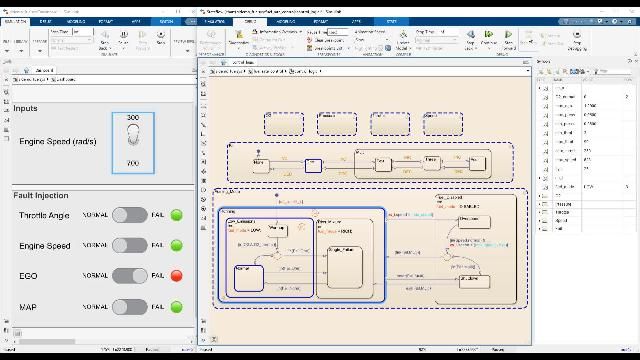

Stateflow では、組み合わせと順序の判定ロジックをモデル化し、Simulink モデル内でブロックとしてシミュレーションしたり、MATLAB オブジェクトとして実行したりできます。グラフィカルなアニメーションを使用して、実行中のロジックを解析およびデバッグできます。編集時および実行時のチェックにより、設計の一貫性と完全性を実装前に確認できます。

ステートマシンの設計

Stateflow では、ドラッグ アンド ドロップ要素とシンプルな論理ステートメントを使用してステートマシンを設計できます。Stateflow 入門およびトレーニングを活用してすぐに始めることができます。

ドキュメンテーション | 例

ドキュメンテーション | 例

ドキュメンテーション | 例

Stateflow チャートの実行

状態図を実行すると、アニメーションによってアクティブなステートと遷移が強調表示されます。実行中に手動で変数を変更して、システムへの影響を可視化できます。

ドキュメンテーション | 例

データの監視および解析

シミュレーション データ インスペクターは、シミュレーション データを可視化する機能を提供します。このツールを使用すると、システムを監視して、その動作に関する重要な洞察を収集できます。

ドキュメンテーション | 例

Stateflow におけるロジックのデバッグ

Stateflow のデバッグ機能により、チャートの実行を詳細にステップ実行できます。ブレークポイントを設定し、状態図のさまざまな関数をステップ実行して、予期しない動作を理解できます。

ドキュメンテーション | 例

Stateflow のタスク スケジューリング

Stateflow は、Simulink アルゴリズムを周期的または連続的に呼び出して、コンポーネントの実行をスケジュールし、リアルタイム環境をシミュレーションできます。

ドキュメンテーション | 例

Simulink による設計の妥当性確認

Stateflow は設計の検証、妥当性確認、テストを行う他の MathWorks 製品とシームレスに統合されます。これらの製品を活用することで、設計が要件を満たしていることを確認し、エラーを早期に発見し、品質目標を達成できます。

ドキュメンテーション | 例

展開用コードの生成

コード生成により、ステート チャート ロジックを組み込みシステムに実装できます。Stateflow は、C、C++、VHDL、Verilog コード、および PLC 用のストラクチャード テキストを生成するワークフローをサポートしています。

ドキュメンテーション | 例

製品リソース:

あなたは学生ですか?

ご所属の学校にはすでに Campus-Wide License が導入されていて、MATLAB、Simulink、その他のアドオン製品を利用できる可能性があります。