このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

さまざまなサブシステム タイプの使用方法

設計にさまざまなサブシステム タイプを使用してアルゴリズムを階層的にモデル化する方法については、以下のガイドラインに従ってください。各ガイドラインに準拠要件のレベルを示す重大度レベルが割り当てられています。詳細については、HDL モデリング ガイドラインの重大度レベルを参照してください。

バーチャル サブシステム: DUT として使用する

ガイドライン ID

2.4.1

重大度

強く推奨

説明

バーチャル サブシステムは、条件付き実行でない subsystem または Atomic Subsystem である subsystem です。既定では、Simulink® モデルに追加する通常の Subsystem ブロックはバーチャル サブシステムです。非バーチャル サブシステム タイプには、Atomic Subsystem、モデル参照、Variant Subsystem、バリアント モデルが含まれます。

サブシステムがバーチャルかどうかを特定するには、関数 get_param をパラメーター IsSubsystemVirtual を指定して使用します。以下に例を示します。

get_param('sfir_fixed/symmetric_fir', 'IsSubsystemVirtual')

Atomic サブシステムとバーチャル サブシステム: 再利用可能な HDL ファイルを生成する

ガイドライン ID

2.4.2

重大度

推奨

説明

階層の下位レベルで使用するサブシステムの同一インスタンスに対して単一の HDL ファイルを生成するには、サブシステムで再利用可能なコードの生成およびCode reuseを参照してください。

サブシステム ユニットでリソース共有を有効にするには、サブシステム共有の一般的な注意事項を参照してください。

Atomic サブシステムとバーチャル サブシステムから再利用可能なコードを生成するには、信号のログをオフにする必要があります。サブシステム内の信号をログに記録する場合は、Atomic サブシステムとバーチャル サブシステムからの再利用可能なコードの生成に失敗する可能性があります。

Variant Subsystem: HDL コード生成用に Variant Subsystem を使用する

ガイドライン ID

2.4.3

重大度

必須

説明

Variant Subsystem ブロックは、Variant Subsystem の選択肢として使用するために 2 つの Subsystem ブロックを含めるように事前構成されたテンプレートです。シミュレーション中に、バリアント制御は 2 つの Subsystem ブロックのどちらがアクティブであるかを決定します。したがって、Variant Subsystem を使用して 2 つの異なる構成またはサブシステムの動作を作成してから、モデル コンパイル段階でのアクティブな構成またはシミュレーションのシミュレーションループ段階を指定できます。Variant Subsystem ブロックの詳細については、Variant Subsystemを参照してください。

Variant Subsystem を DUT として使用することはできません。コードを生成するには、DUT として使用するサブシステム内に Variant Subsystem を配置します。ファイル名と生成されたコードのインスタンス名は、アクティブな構成のみ、またはアクティブおよび非アクティブ両方の構成のために作成されます。

Variant Subsystem の最適化を使用して複数の Variant Subsystem ブロックを共有することはできません。

生成されたコードの機能を検証する際に、モデルのシミュレーションで使用したアクティブなバリアントが HDL コードの生成で使用したアクティブなバリアントと同じであることを確認しなければなりません。

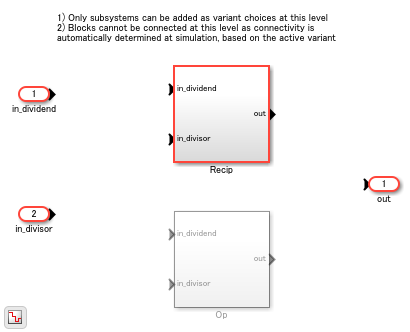

たとえば、モデル hdlcoder_variant_subsystem_design.slx を開きます。DUT サブシステムを開くと、Variant Subsystem ブロック Divide が表示されます。Variant Subsystem には Recip と Op の 2 つの異なるサブシステムがあります。Divide サブシステムの [ブロック パラメーター] ダイアログ ボックスを開くと、シミュレーション時に有効にするサブシステムを決定する [バリアント制御式] と [条件] が表示されます。[バリアントのアクティベーションのタイミング] によって、シミュレーションのどの段階でサブシステムを有効にするかが決まります。この場合、Rcp は 1 であり、アクティベーション時間は update diagram になります。Recip サブシステムはシミュレーション時にアクティブになります。

load_system('hdlcoder_variant_subsystem_design') set_param('hdlcoder_variant_subsystem_design','SimulationCommand','Update') open_system('hdlcoder_variant_subsystem_design/DUT/Divide')

生成コード

HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_variant_subsystem_design/DUT');Recip サブシステムはコード生成時にアクティブであり、コードの生成対象であるため、Recip.vhd という名前の HDL ファイルが生成されます。

Recip と Op 両方の HDL コードを生成するには、Divide サブシステムの [ブロック パラメーター] ダイアログ ボックスでこれらのパラメーターの設定を変更してから、makehdl コマンドを実行します。

1. [バリアントのアクティベーションのタイミング] を startup に設定します。

set_param('hdlcoder_variant_subsystem_design/DUT/Divide','VariantActivationTime','startup')

2. Simulink.VariantControl タイプ、通常の MATLAB® 変数、または Simulink.Parameter のバリアント制御変数 Rcp を設定し、その値を整数値に設定します。この例では、Rcp は int16 値を持つ通常の MATLAB 変数です。

Rcp = int16(1);

3. [組み込みの空の選択肢] を on に設定します。

set_param('hdlcoder_variant_subsystem_design/DUT/Divide','EmptyChoice','on')

4. [Variant Subsystem の外部に条件を伝播する] を off に設定します。

set_param('hdlcoder_variant_subsystem_design/DUT/Divide','PropagateVariantConditions','off')

メモ: Recip および Op サブシステムの [Atomic サブシステムとして扱う] が on に設定されていることを確認します。

set_param('hdlcoder_variant_subsystem_design/DUT/Divide/Recip','TreatAsAtomicUnit','on') set_param('hdlcoder_variant_subsystem_design/DUT/Divide/Op','TreatAsAtomicUnit','on')

次のコマンドを使用して HDL コードを生成します。

makehdl('hdlcoder_variant_subsystem_design/DUT');Recip と Op 両方のサブシステムに対してコードが生成されるため、Recip.vhd と Op.vhd という名前の HDL ファイルが生成されます。

HDL Coder でバリアント サブシステム Divide の次の VHDL® コードが生成され、そのバリアント制御変数は調整可能なパラメーター Rcp に設定されます。コード ジェネレーターによって DUT 端子が生成され、その端子が調整可能なパラメーターに対応することを示すコメントが追加されます。Rcp にマッピングされたチップ上のピンに値を指定することで、Rcp の値を変更できます。

ENTITY Divide IS

PORT( clk : IN std_logic;

reset : IN std_logic;

enb : IN std_logic;

in_dividend : IN std_logic_vector(15 DOWNTO 0); -- sfix16_En14

in_divisor : IN std_logic_vector(15 DOWNTO 0); -- sfix16_En13

Rcp : IN std_logic_vector(23 DOWNTO 0); -- sfix24_En9 Tunable port

out_rsvd : OUT std_logic_vector(23 DOWNTO 0) -- sfix24_En9

);

END Divide;VariantMerge_For_Outport_out_out1 <= Op_out1_signed WHEN Selected_Index_floor = to_signed(16#0001#, 15) ELSE Recip_out1_signed WHEN Selected_Index_floor = to_signed(16#0002#, 15) ELSE GroundForVM_out_out1;

モデル参照: 小規模な分割を使用したモデル設計をビルドする

ガイドライン ID

2.4.4

重大度

推奨

説明

大規模な設計を階層的にモデル化すると、コード生成時間が増加する可能性があります。トレーサビリティ レポートなどのレポートの生成を指定する場合、コード生成時間はさらに大幅に増加する場合があります。このようなパフォーマンスの問題を回避するには、小規模な分割に設計を分割することをお勧めします。Modelブロックを使用して小規模な分割で構成されるモデルを統一します。また、インクリメンタルなコード生成を行うこともできます。親モデルまたは参照モデルに対して HDL コードを生成できます。生成された HDL コードを表示するには、hdlsrc フォルダーに、親モデル用のフォルダーが、参照モデル用の個別のサブフォルダーと共に作成されます。

HDL テスト ベンチの生成時に、テスト ベンチが連続サンプル時間で動作するブロックで構成されている場合、DUT を参照モデルに変換できます。この変換により、DUT を固定ステップ、離散サンプル時間で実行できます。詳細については、連続ブロックを使用したテストベンチ用のモデル参照への DUT サブシステムの変換を参照してください。

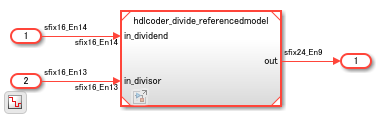

たとえば、モデル hdlcoder_divide_parentmodel.slx を開きます。DUT サブシステムをダブルクリックすると、モデル hdlcoder_divide_referencedmodel を参照する Model ブロックが表示されます。

load_system('hdlcoder_divide_parentmodel') set_param('hdlcoder_divide_parentmodel', 'SimulationCommand', 'Update') open_system('hdlcoder_divide_parentmodel/DUT')

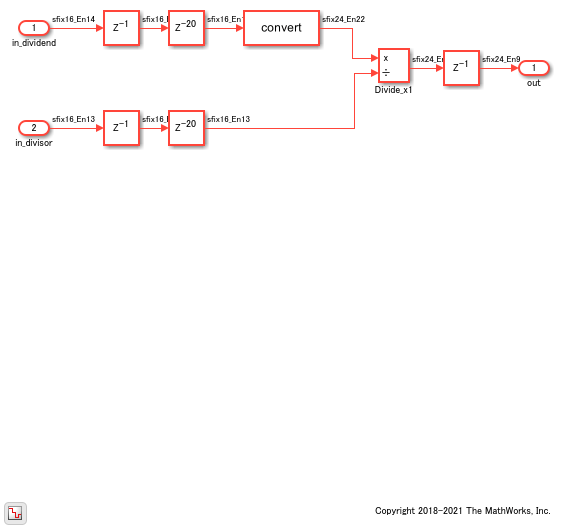

参照モデルを表示するには、Model ブロックをダブルクリックします。

open_system('hdlcoder_divide_parentmodel/DUT/Model')

HDL コードを生成するには、次のコマンドを入力します。

makehdl('hdlcoder_divide_parentmodel/DUT')

詳細については、HDL コード生成でのモデル参照を参照してください。

Enabled Subsystem と Triggered Subsystem のブロック設定

ガイドライン ID

2.4.5

重大度

必須

説明

Triggered Subsystem は Trigger ブロックから制御信号を受け取るサブシステムです。Triggered Subsystem はトリガー イベントが発生するたびに 1 サイクルを実行します。Triggered Subsystem の HDL コードを生成する場合、以下を考慮します。

Triggered Subsystem ブロックを DUT として使用しないでください。Triggered Subsystem を別の Subsystem ブロック内に配置し、その Subsystem を DUT として使用します。

Triggered Subsystem ブロックの外部で Triggered Subsystem の出力信号に単位遅延を追加できます。単位遅延により、HDL Coder™ で追加のバイパス レジスタが HDL コードに挿入されないようにします。

[トリガー信号をクロックとして使用] 設定により、テストベンチをシミュレートして生成されたコードを検証する際にタイミングの不一致が発生しないことを確認します。詳細については、HDL コード生成のための Triggered Subsystem の使用を参照してください。

HDL コード生成用に Triggered Subsystem ブロックを構成する際のその他の基本設定については、Triggered Subsystem ページのHDL コード生成を参照してください。

Enabled Subsystem は Enable ブロックから制御信号を受け取るサブシステムです。Enabled Subsystem は制御信号に正の値がある各シミュレーション ステップで実行されます。Enabled Subsystem の HDL コードを生成する場合、以下を考慮します。

Enabled Subsystem ブロックを DUT として使用しないでください。Enabled Subsystem を別の Subsystem ブロック内に配置し、その Subsystem を DUT として使用します。

State Control ブロックを

Synchronousモードで Enabled Subsystem 内に追加すると、より効率的でハードウェア親和型の HDL コードを生成できます。Synchronousモードの State Control ブロックにより、HDL Coder で追加のバイパス レジスタが HDL コードに挿入されないようにします。State Control ブロックは Enabled Subsystem ブロックを Enabled Synchronous Subsystem ブロックに変換します。詳細については、State Control ブロックを使用する同期サブシステムの動作を参照してください。State Control ブロックを

Classicモードにする場合や State Control ブロックを追加しない場合は、Enabled Subsystem ブロックの外部で Enabled Subsystem の出力信号に単位遅延を追加することによって、HDL Coder で追加のバイパス レジスタが HDL コードに挿入されないようにすることができます。

HDL コード生成用に Enabled Subsystem ブロックを構成する際のその他の基本設定については、Enabled Subsystem ページのHDL コード生成を参照してください。