このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

HDL コード生成のための Triggered Subsystem の使用

Triggered Subsystem ブロックは、制御信号がトリガー値をもつたびに実行される Subsystem ブロックです。ブロックの詳細については、Triggered Subsystem を参照してください。

ベスト プラクティス

HDL コード生成をターゲットにしているモデルで Triggered Subsystem を使用するときは、次のことを検討します。

合成結果を Simulink® 結果と一致させるために、FPGA 上で (同期クロックをもつ) 登録済みのロジックを使用してトリガー端子を駆動する。

Triggered Subsystem の出力信号に単位遅延を加えることが推奨される。こうすることで、コード ジェネレーターによって余分なバイパス レジスタが HDL コード内に挿入されることを回避できます。

Triggered Subsystem を使用すると、合成結果に次のように影響する可能性がある。

システム クロックの速度がわずかに低下する場合がある。

Triggered Subsystem インスタンスの数とサブシステムあたりの出力端子の数に対応して、生成コードでより多くのリソースが使用される。

Signal Editor ブロックの使用

出力を Signal Editor ブロックから Triggered Subsystem に接続するときに、Rate Transition ブロックを使用しなければならない場合があります。Triggered Subsystem のすべての端子を同じレートで実行するには、次を行います。

トリガー ソースが Signal Editor ブロックであるが、その他の Triggered Subsystem の入力が他のソースから取り込まれている場合、トリガー入力の前に Rate Transition ブロックを信号パスに挿入する。

すべての入力 (トリガーを含む) が Signal Editor ブロックから取り込まれている場合は、レートが同じであるため、特別なアクションは必要ない。

トリガーをクロックとして使用

Triggered Subsystem 内でトリガーをクロックとして使用すると、生成コードにおいて設計を異なるクロック領域に分割できます。[コンフィギュレーション パラメーター] ダイアログ ボックスの [クロック エッジ] 設定が、Triggered Subsystem 内の Trigger ブロックの [トリガー タイプ] と一致していることを確認します。

たとえば、次のモデル化が可能になります。

同じレート、異なる位相で動作するクロックをもつ設計。

外部または内部のクロック デバイダーによって駆動される複数のクロック領域。

レートが互いの整数倍ではない複数のクロックで駆動される複数のクロック領域。

内部生成されるクロック。

低電力設計のクロック ゲート。

メモ

Triggered Subsystem のクロックとしてトリガーを使用すると、テストベンチのシミュレーション中に 1 サイクルのタイミングの不一致が生じる場合があります。

トリガーをクロックとして指定

[HDL コード生成] 、 [グローバル設定] 、 [端子] タブで、[トリガー信号をクロックとして使用] を選択します。

makehdlまたはhdlset_paramを使用してTriggerAsClockプロパティを設定します。たとえば、トリガー信号をモデルmyModel内の DUT サブシステムmyDUT内にある Triggered Subsystem のクロックとして使用する HDL コードを生成するには、次のように入力します。makehdl ("myModel/myDUT",TriggerAsClock="on")

同期レジスタなしのクロックとしてトリガー

Triggered Subsystem のクロックとしてトリガーを使用する場合、Triggered Subsystem の各入力または出力は、サブシステムのすぐ外側とすぐ内側に同期遅延が必要です。これらの遅延は、異なるレートで動作している複数の領域間の同期インターフェイスの役割を果たします。HDL Coder™ では、"同期レジスタなしのクロックとしてトリガー" オプションを有効にすることで、同期遅延を追加せずに HDL コードを生成できます。既定では、このオプションは on です。

このオプションは、関数 makehdl または hdlset_param を使用して有効または無効にできます。たとえば、モデル myModel 内の DUT サブシステム myDUT に対し、同期遅延をもたずに Triggered Subsystem のクロックとしてトリガーを使用する HDL コードを生成するには、次のように入力します。

makehdl("myModel/myDUT",TriggerAsClockWithoutSyncRegisters="on")

Triggered Subsystem でトリガー信号をクロックとしてモデル化

この例では、Triggered Subsystem のトリガー端子をクロック信号としてモデル化する方法を説明します。Triggered Subsystem でクロックとしてトリガーを使用する機能により、生成された HDL コード内でトリガー信号をクロックとして使用できます。

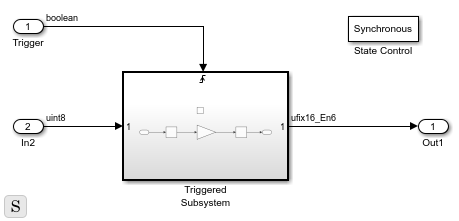

モデル TriggerAsClockSingle には、Triggered Subsystem を含む DUT サブシステムがあります。次のコマンドを実行して TriggerAsClockSingle モデルを読み込んで開きます。

load_system("TriggerAsClockSingle"); set_param("TriggerAsClockSingle",'SimulationCommand','Update') open_system("TriggerAsClockSingle/DUT");

生成された HDL コードでトリガー信号をクロックとして使用するには、コンフィギュレーション設定の [HDL コード生成]、[グローバル設定]、[端子] タブで、[トリガー信号をクロックとして使用] オプションを有効にします。次に、makehdlコマンドまたは HDL Coder™ アプリを使用して DUT サブシステムの HDL コードを生成します。

makehdl("TriggerAsClockSingle/DUT")

生成された HDL コードで、HDL Coder は Triggered Subsystem のトリガー端子をクロックにマッピングします。次のコードの抜粋は、Trigger 信号をクロックとして使用する Triggered Subsystem の HDL コードを示しています。

Delay1_process : PROCESS (Trigger, reset)

BEGIN

IF reset = '1' THEN

Delay1_out1 <= to_unsigned(16#0000#, 16);

ELSIF Trigger'EVENT AND Trigger = '1' THEN

Delay1_out1 <= Gain_out1;

END IF;

END PROCESS Delay1_process;Triggered Subsystem と Resettable Subsystem を使用したクロック信号およびリセット信号のモデル化

Triggered Subsystem と Resettable Subsystem を使用して、クロックやリセットなどの制御信号をモデル化できます。クロックとしてトリガーを使用する機能により、Triggered Subsystem からのトリガー端子をクロックとしてモデル化し、Resettable Subsystem を使用して Simulink からのリセット端子をモデル化できます。

HDL コード生成をターゲットとするモデルで Triggered Subsystem または Resettable Subsystem を使用すると、以下を実行できます。

Triggered Subsystem 内に Resettable Subsystem を含めて、Simulink からのクロック信号とリセット信号をモデル化する。

同期セマンティクスをもつ Triggered Subsystem を使用する。

[トリガー信号をクロックとして使用] パラメーターと [グローバル リセットの最小化] パラメーターを使用して、Triggered Subsystem 内で入れ子にされた Resettable Subsystem に対して単一のクロックとリセットをもつコードを生成する。

複数の Triggered Subsystem と Resettable Subsystem で構成されるモデルに対して複数のクロック信号とリセット信号をもつコードを生成する。

Triggered Subsystem 内で Unit Delay Enabled Synchronous ブロックを使用する。

同期セマンティクスをもつ Resettable Subsystem に Unit Delay ブロックを追加し、その Resettable Subsystem を Triggered Subsystem 内に配置することで、Triggered Subsystem 内で Unit Delay Resettable Synchronous ブロックをモデル化する。

同期セマンティクスをもつ Resettable Subsystem に Unit Delay Enabled ブロックを追加し、その Resettable Subsystem を Triggered Subsystem 内に配置することで、Triggered Subsystem 内で Unit Delay Enabled Resettable Synchronous ブロックをモデル化する。

Triggered Subsystem と Resettable Subsystem を使用した単一のクロック信号およびリセット信号のモデル化

この例では、Triggered Subsystem と Resettable Subsystem を使用してクロック信号およびリセット信号をモデル化する方法を説明します。クロックとしてトリガーを使用する機能により、Triggered Subsystem からのトリガー端子をクロックとしてモデル化し、Resettable Subsystem を使用してリセット端子をモデル化できます。

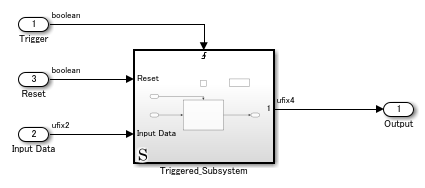

モデル ClockAndResetModellingUsingTriggerAsClock には、Triggered Subsystem を含む DUT サブシステムがあります。次のコマンドを実行して ClockAndResetModellingUsingTriggerAsClock モデルを読み込んで開きます。

load_system("ClockAndResetModellingUsingTriggerAsClock"); set_param("ClockAndResetModellingUsingTriggerAsClock",'SimulationCommand','Update') open_system("ClockAndResetModellingUsingTriggerAsClock/DUT");

Triggered Subsystem 内に Resettable Subsystem が配置されています。Resettable Subsystem を使用して、モデルのリセット端子をモデル化できます。グローバル リセット オプションを最小化して、モデルが Resettable Subsystem からの単一のリセット信号をもつようにします。グローバル リセット オプションを最小化するには、コンフィギュレーション設定の [HDL コード生成]、[グローバル設定]、[端子] タブで、[グローバル リセットの最小化] を有効にします。

生成された HDL コードでトリガー信号をクロックとして使用するには、[HDL コード生成]、[グローバル設定]、[端子] タブで、[トリガー信号をクロックとして使用] オプションを有効にします。次に、makehdlコマンドまたは HDL Coder™ アプリを使用して DUT サブシステムの HDL コードを生成します。

makehdl("ClockAndResetModellingUsingTriggerAsClock/DUT")

生成された HDL コードで、HDL Coder は Triggered Subsystem のトリガー端子をクロックにマッピングします。また、Resettable Subsystem からリセット信号が生成されます。Triggered Subsystem の HDL コードは、トリガー端子から Resettable Subsystem のクロック信号へのマッピングを示します。

module Triggered_Subsystem

(Trigger,

Reset_1,

Input_Data,

Output_rsvd); input Trigger;

input Reset_1;

input [1:0] Input_Data; // ufix2

output [3:0] Output_rsvd; // ufix4wire [3:0] Resettable_Subsystem_out1; // ufix4

Resettable_Subsystem u_Resettable_Subsystem (.clk(Trigger),

.Input_Data(Input_Data), // ufix2

.Reset_1(Reset_1),

.Output_rsvd(Resettable_Subsystem_out1) // ufix4

);

assign Output_rsvd = Resettable_Subsystem_out1;endmodule // Triggered_Subsystem

制限

HDL Coder は、以下の条件を満たす Triggered Subsystem の HDL コード生成をサポートします。

Triggered Subsystem が DUT ではない。

サブシステムのトリガー "および" 有効化が "どちらも" 行われていない。

トリガー信号がスカラーである。

Subsystem の出力がバスである場合、出力端子の初期値は 0 でなければならない。

Triggered Subsystem のすべての入出力 (トリガー信号を含む) が同じレートで実行される。

Trigger ブロックの [出力端子の表示] パラメーターが

[オフ]に設定されている。Triggered Subsystem 内の Inport ブロックでは [外部信号を遅延して入力をラッチ] チェック ボックスは選択されていない。

DUT に以下のブロックが含まれている場合、

RAMArchitectureがWithClockEnableに設定されている。Dual Port RAM

Simple Dual Port RAM

Single Port RAM

Triggered Subsystem に以下のブロックが含まれていない。

Discrete-Time Integrator

CIC Decimation

CIC Interpolation

FIR Decimation

FIR Interpolation

Downsample

Upsample

HDL Verifier™ の HDL Cosimulation ブロック

Rate Transition

Pixel Stream FIFO (Vision HDL Toolbox™)

PN Sequence Generator ([トリガー信号をクロックとして使用] オプションが選択されている場合)

参考

Use Triggered Subsystem for Asynchronous Clock Domain