Convolutional Encoder

畳み込み符号化スキームを使用したバイナリ データの符号化

ライブラリ:

Communications Toolbox /

Error Detection and Correction /

Convolutional

Communications Toolbox HDL Support /

Error Detection and Correction /

Convolutional

説明

Convolutional Encoder ブロックは、トレリス構造体で指定された畳み込み符号化スキームを使用して、入力バイナリ メッセージを符号化します。詳細については、畳み込み符号化を参照してください。

このブロックは、シミュレーション中に長さが変化する入力を受け入れることができます。可変サイズ信号の詳細については、可変サイズの信号の基礎 (Simulink)のトピックを参照してください。

以下のアイコンには、有効にしたオプションのブロック端子が表示されています。

![]()

![]()

例

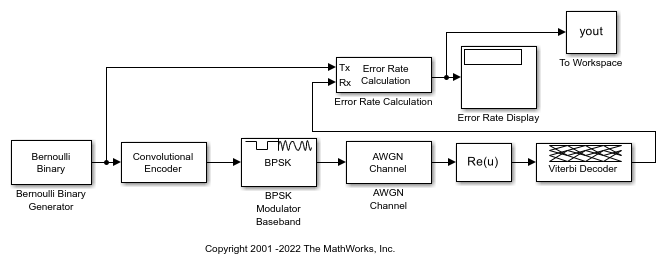

畳み込み符号化と BPSK 変調をバイナリ信号に適用し、変調後の信号を AWGN チャネルに渡します。BPSK 復調とビタビ復号化を適用した後の信号のシンボル エラー レート (SER) を計算します。

モデルの検証

doc_conv モデルは、Bernoulli Binary Generatorブロックを使用してバイナリ信号を生成します。Convolutional Encoderブロックは信号を符号化します。BPSK Modulator Basebandブロックは信号を変調します。AWGN Channelブロックは信号にノイズを付加します。BPSK 変調信号をゼロ位相シフトで復調するには、Complex to Real-Imag (Simulink)ブロックを使用して複素シンボル復調の実数成分の値を単に抽出します。Viterbi Decoderブロックは信号を復号化します。Error Rate Calculationブロックは SER を計算します。

シミュレーションの実行

ans =

'Filtering the signal through an AWGN channel with the EsN0 set to -1 dB, the computed SER is 0.005608.'

ans =

'For 53499 transmitted symbols, there were 300 symbols errors.'

この例では、符号化率 1/2 の畳み込み符号化とビタビ復号化を使用するパンクチャド符号化システムをシミュレートします。ビタビ復号化器の複雑度は符号化率に伴い急激に増大します。パンクチャ手法を使用すると、符号化率の低い標準のコーダーを使用して符号化率の高い符号の符号化と復号化を行うことができます。

cm_punct_conv_code モデルは、畳み込み符号化後の BPSK 信号を AWGN チャネル経由で送信し、受信信号を復調し、ビタビ復号化を行って符号化前の信号を復元します。このモデルは、エラー レートを計算するため、元の % 信号と復号化後の信号を比較します。

このモデルは、コールバック関数 PreloadFcn を使用してこれらのワークスペース変数を設定し、ブロック パラメーターを初期化します。

puncvec = [1;1;0;1;1;0]; EsN0dB = 2; traceback = 96; % Viterbi traceback depth

詳細については、モデル コールバック (Simulink)を参照してください。

このモデルのブロックは次の処理を行います。

Bernoulli Binary Generator — [フレームあたりのサンプル数] を

3に設定します。このブロックは、各サンプル時刻においてフレームあたり 3 つのサンプルを出力するランダム ビットから成るシーケンスを作成します。Convolutional Encoder — [Trellis structure] で既定の設定を使用し、[Puncture code] を選択し、[パンクチャ ベクトル] をワークスペース変数

puncvecに設定します。このブロックは、符号化率 1/2、拘束長 7 の畳み込み符号を符号化率 3/4 の符号にパンクチャすることによって、データのフレームを符号化します。puncvecで指定されたパンクチャ ベクトルは、符号化率が 1/2 で拘束長が 7 の畳み込み符号に最も適したパンクチャ ベクトルです。パンクチャ ベクトルにおいて、1は符号化されたベクトルの対応する位置にあるビットが出力ベクトルに送信されることを示し、0はそのビットが削除されることを示します。ここで構成した符号化器では、符号化後の位置 1、2、4、および 5 にあるビットは送信されますが、位置 3 および 6 にあるビットは削除されます。符号化率が 3/4 であるということは、3 ビットを入力するごとにパンクチャド符号によって 4 ビットの出力が生成されることを意味します。BPSK Modulator Baseband — 既定のパラメーター値を使用して、符号化されたメッセージを変調します。

AWGN Channel — [モード] を

Signal to noise ratio (Es/No)に設定し、Es/No (dB)をワークスペース変数EsN0dBに設定します。変調器ブロックは単位電力信号を生成するため、[Input signal power, referenced to 1 ohm (watts)] は既定値1のままにします。Viterbi Decoder — [Trellis structure]、[Punctured code]、および [パンクチャ ベクトル] を、Convolutional Encoder ブロックに合わせて設定します。このブロックは、[判定タイプ] を

Unquantizedに設定し、[トレースバック長] をワークスペース変数tracebackに設定します。符号のパンクチャ処理を行わない場合、指定した畳み込み符号を復号化するにはトレースバック長が 40 あれば十分です。ただし、このブロックは、パンクチャによって生じるあいまいさを解決するための十分なデータを復号化器に与えるため、トレースバック長を 96 にしてパンクチャド符号を復号化します。畳み込み符号化器と同様に、復号化器のパンクチャ ベクトルによってパンクチャの位置が示されます。パンクチャされたビットは送信されないため、その値を示す情報は存在しません。そのため、復号化器による復号化処理では、この位置にあるビットは無視されます。パンクチャ ベクトルの各 1 は送信されるビットを、各 0 は復号化器への入力で無視されるパンクチャされたビットを示します。Complex to Real-Imag (Simulink) — 複素数サンプルの実数部を抽出して BPSK 信号を復調します。

Error Rate Calculation — [受信遅延] の値を使用してシステム遅延のサンプル数の合計を表し、復号化されたビットを元のソース ビットと比較します。このブロックは、計算された BER、観測された誤り数、および処理されたビットの数で構成される 3 要素ベクトルを出力します。このシステムではビタビのトレースバック長によってのみ遅延が生じるため、[受信遅延] をワークスペース変数

tracebackに設定します。一般に、BER シミュレーションは、誤り数が最小となるまで、またはシミュレーションで最大数のビットが処理されるまで実行されます。Error Rate Calculation ブロックは、シミュレーション期間を制御するため、[シミュレーションの停止] パラメーターを選択し、目標誤り数を100に設定し、シンボルの最大数を1e6に設定します。

ビット エラー レートの評価

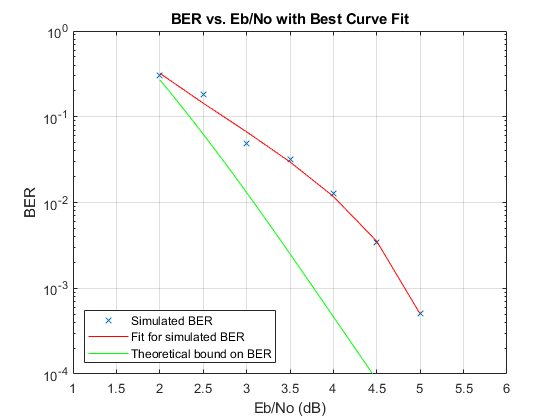

設定した EbN0 の範囲についてこのコードを実行してモデルをシミュレートし、ビット エラー レート曲線を作成します。

シミュレーション結果をパンクチャド符号ビット エラー確率の境界近似値と比較します [1]。符号化率  のパンクチャド符号のビット エラー レート性能は、次式のように上に有界となります。

のパンクチャド符号のビット エラー レート性能は、次式のように上に有界となります。

この式において、erfc は相補誤差関数を示し、 は符号化率を示します。

は符号化率を示します。 と

と  はどちらも個々のコードに依存します。この例で示す符号化率 3/4 の符号の場合、

はどちらも個々のコードに依存します。この例で示す符号化率 3/4 の符号の場合、 = 5、

= 5、 = 42、

= 42、 = 201、

= 201、 = 1492 などのようになります。詳細については、参考文献 [ 1 ] を参照してください。

= 1492 などのようになります。詳細については、参考文献 [ 1 ] を参照してください。

2:0.02:5 における Eb/N0 の値の積算の最初の 7 項を使用して、理論的な境界の近似値を計算します。nerr で使用する値は参考文献 [ 2 ] の Table II から取得します。

シミュレーション結果、近似曲線、および理論的な境界をプロットします。

場合によっては、下方ビットのエラー レートが限界より少し上回るようなシミュレーション結果になることがあります。これは、復号器のトレースバック長が有限なためです。または、ビット エラーの観測個数が 500 個未満の場合はシミュレーションのばらつきによるものです。

パンクチャを行わない畳み込み符号化を示す例については、誤りの検出と訂正の「軟判定復号化」のセクションを参照してください。

参考文献

Yasuda, Y., K. Kashiki, and Y. Hirata, "High Rate Punctured Convolutional Codes for Soft Decision Viterbi Decoding," IEEE Transactions on Communications, Vol. COM-32, March, 1984, pp. 315–319.

Begin, G., Haccoun, D., and Paquin, C., "Further results on High-Rate Punctured Convolutional Codes for Viterbi and Sequential Decoding," IEEE Transactions on Communications, Vol. 38, No. 11, November, 1990, p. 1923.

Viterbi Decoderブロックを固定小数点の硬判定畳み込み復号化と軟判定畳み込み復号化に使用します。ビット エラー レート解析アプリで計算された理論上の上限と結果を比較します。

シミュレーションの構成

cm_viterbi_harddec_fixpt モデルおよび cm_viterbi_softdec_fixpt モデルは、同様のレイアウトを使用して、ビタビ復号化器の固定小数点モデリング属性を強調表示します。モデルの既定の構成では、PreLoadFcn コールバックを使用して、AWGN Channelブロックの  の設定を 4 dB に指定します。畳み込み符号化器は、符号化率 1/2 の符号化器として構成されます。具体的には、2 ビットごとに、符号化器がさらに 2 つの冗長ビットを追加します。符号化率に対応するため、AWGN ブロックの [Eb/No (dB)] パラメーターは、割り当てられた

の設定を 4 dB に指定します。畳み込み符号化器は、符号化率 1/2 の符号化器として構成されます。具体的には、2 ビットごとに、符号化器がさらに 2 つの冗長ビットを追加します。符号化率に対応するため、AWGN ブロックの [Eb/No (dB)] パラメーターは、割り当てられた  の設定から

の設定から 10*log10(2) を差し引くことにより、半分にされます。Error Rate Calculationブロックの実行期間を 100 エラーまたは 1e6 ビットに制限します。

固定小数点モデリング

固定小数点モデリングは、ハードウェア実装の検討およびデータとパラメーターのダイナミック レンジを考慮に入れたビットトゥルー シミュレーションを有効にします。たとえば、対象のハードウェアが DSP マイクロプロセッサである場合、可能性のある語長は 8、16、または 32 ビットであり、ターゲット ハードウェアが ASIC または FPGA の場合は語長の選択に柔軟性があります。

固定小数点のビタビ復号化を有効にするための条件は、次のとおりです。

硬判定の場合、ブロック入力は ufix1 型 (語長 1 の符号なし整数) でなければなりません。この入力 ( a 0 または a 1 のいずれか) に基づき、内部分岐メトリクスは、トレリス構造体に指定された (硬判定例の場合は 2 に等しい) ように、語長の符号なし整数 = (出力ビットの数) を使用して計算されます。

軟判定の場合、ブロック入力は ufixN 型 (語長 N の符号なし整数) でなければなりません。ここで、N は固定長小数点の復号化を有効にするための軟判定ビットの数です。ブロック入力は、0 ~

の範囲の整数でなければなりません。内部分岐メトリクスは、トレリス構造体に指定された (軟判定例の場合は 4 に等しい) ように、語長の符号なし整数 = (N + 出力ビットの数 - 1) を使用して計算されます。

の範囲の整数でなければなりません。内部分岐メトリクスは、トレリス構造体に指定された (軟判定例の場合は 4 に等しい) ように、語長の符号なし整数 = (N + 出力ビットの数 - 1) を使用して計算されます。

[State metric word length] は、ユーザーによって指定され、通常は既に計算されている分岐メトリクス語長よりも長くなければなりません。これは、システム用に記録されたデータを確認することによって、最も適した値に (ハードウェアやデータの検討に基づいて) 調整することができます。

ログを有効にするため、[アプリ]、[固定小数点ツール] を選択します。[固定小数点設定] メニューで、[固定小数点のインストルメンテーション モード] を [Minimums, maximums and overflows] に設定し、シミュレーションを再実行します。オーバーフローが確認できた場合は、データが選択したコンテナーに収まらなかったことを示しています。データを処理する前にデータのスケーリングを行うか、語長のサイズを増やしてみる (ハードウェアで許可されている場合) ことができます。データの最小値と最大値に基づいて、選択したコンテナーが適切なサイズであるかどうかを判断することもできます。

[State metric word length] のさまざまな値でシミュレーションを実行して、その値のアルゴリズムへの影響を理解します。BER の結果に悪影響を及ぼさない適切な値になるようにパラメーターを絞り込むこともできます。

cm_viterbi_harddec_fixpt モデルの硬判定構成:

BPSK Demodulator Basebandは、復号化器に渡される硬判定を生成します。

Data Type Conversion (Simulink)ブロックは

ModeパラメーターをFixed pointに設定し、出力データ型をfixdt(0,1,0)にキャストします。Viterbi Decoderブロックに対する信号入力はufix1です。

Viterbi Decoder ブロックの

Decision typeパラメーターはHard decisionに設定されます。[Data Types] タブでは、State metric word lengthが4に設定され、Output data typeがbooleanに設定されます。ビット エラー レートが表示され、ワークスペース変数BERに取得されます。

cm_viterbi_softdec_fixpt モデルの軟判定構成:

BPSK Demodulator Basebandは、対数尤度比を使用して軟判定を生成します。これらの軟出力は、3 ビットで量子化され、復号化器に渡されます。

Quantizer サブシステム (Gain (Simulink)、Scalar Quantizer Encoder、Data Type Conversion (Simulink)ブロックを含む) は信号を量子化し、出力データ型を

fixdt(0,3,0)にキャストします。Viterbi Decoderブロックに対する信号入力はufix3です。

Viterbi Decoderブロックでは、

Decision typeパラメーターはSoft decision、Number of soft decision bitsは 3 に設定されています。[Data Types] タブでは、State metric word lengthが6、Output data typeがbooleanに設定されています。ビット エラー レートが表示され、ワークスペース変数BERに取得されます。

硬判定と軟判定の復号化の比較

2 つのモデルは、ビット エラー レート解析アプリ内から実行してシミュレーション曲線を生成し、硬判定復号化と軟判定復号化の BER 性能を比較するように構成されています。

以下に概説する手順に従って、次のプロットで結果を生成できます。

以下の手順により、理論値と固定小数点の硬判定/軟判定ビタビ復号化のシミュレーション結果が生成されます。

[アプリ] タブで選択するか、MATLAB コマンド プロンプトで

bertoolと入力して、ビット エラー レート解析アプリを開きます。[Theoretical] ペインで、[Eb/N0 range] を 2:5 に設定し、[Channel type] を

[AWGN]に設定し、[Modulation type] を[PSK]に設定し、[Channel coding] を[Convolutional]に設定し、[Decision method] を[Hard]に設定して実行した後[Soft]に設定して実行します。理論上の結果の硬判定データ セットと軟判定データ セットを識別できるように、[BER Data Set] の名前を変更します。[Monte Carlo] ペインで、[Eb/N0 range] を 2:1:5 に設定し、[Simulation environment] で

[Simulink]を選択し、[BER variable name] を[BER]に設定し、[Simulation limits] の [Number of errors] を 100、[Number of bits] を 1e6 に設定します。[Model name] をcm_viterbi_harddec_fixptに設定して実行した後cm_viterbi_softdec_fixptに設定して実行します。Simulink の結果の硬判定データ セットと軟判定データ セットを識別できるように、[BER Data Set] の名前を変更します。

この 4 回の実行により、アプリは次のイメージのようになります。

倍精度データとの比較

さらに詳しく調べるために、Apps > Fixed-Point Tool を選択して、倍精度データで同じモデルを実行できます。Fixed-Point Tool アプリで、Data type override を選択して Double にします。この選択によって、すべてのブロックのすべてのデータ型設定がオーバーライドされて倍精度を使用します。Viterbi Decoder ブロックでは、Output type が boolean に設定されているため、このパラメーターも double に設定しなければなりません。

モデルのシミュレーション時に、倍精度と固定小数点の BER の結果が同じであることに注意してください。これらが同じになるのは、精度の低下を避け、メモリ効率を最適化するためにモデルの固定小数点パラメーターが選択されているためです。

拡張例

テールバイティング畳み込み符号化

Convolutional Encoder ブロックと Viterbi Decoder ブロックを使用して、テールバイティング畳み込み符号をシミュレートする。

端子

入力

入力メッセージ。バイナリ列ベクトルとして指定します。この端子は 2 番目の入力端子が有効になるまでは名前なしになります。符号化器が K 入力ビット ストリームを取る (つまり、2K の入力シンボル候補を受信できる) 場合、ブロックの入力ベクトルの長さはある正の整数 L に対して L×K になります。

例: [1 1 0 1 0 0 1 1] はメッセージを 8 要素のバイナリ行ベクトルとして指定します。

データ型: double | single | Boolean | int8 | int16 | int32 | uint8 | uint16 | uint32 | ufix1

ブロックへのフレーム入力ごとの符号化器レジスタの初期状態。非負の整数として指定します。

依存関係

この端子を有効にするには、[Operation mode] パラメーターを [Truncated (reset every frame)] に設定し、[Specify initial state via input port] を選択します。

データ型: double | uint32

符号化器レジスタの状態のリセット。スカラー値として指定します。任意の非ゼロ値により、符号化器レジスタのリセットが強制されます。

依存関係

この端子を有効にするには、[Operation mode] パラメーターを [Reset on nonzero input via port] に設定します。

データ型: double | Boolean

出力

畳み込み符号化されたコードワード。バイナリ列ベクトルとして返されます。この端子はブロック アイコンで名前なしになります。符号化器が N 個の出力ビット ストリームを生成する (つまり、2N 個の出力シンボル候補を生成できる) 場合、ブロックの出力ベクトルの長さはある正の整数 L に対して L×N になります。この出力のデータ型は、In 入力から継承されます。

データ型: double | single | Boolean | int8 | int16 | int32 | uint8 | uint16 | uint32 | ufix1

ブロックから出力される各フレームの符号化器レジスタの最終状態。非負の整数として返されます。

依存関係

このパラメーターは、[Operation mode] パラメーターを [Continuous]、[Truncated (reset every frame)]、または [Reset on nonzero input via port] に設定し、[Output final state] パラメーターを選択したときにのみ表示されます。

データ型: double

パラメーター

ブロック パラメーターを対話的に編集するには、プロパティ インスペクターを使用します。Simulink® ツールストリップの [シミュレーション] タブの [準備] ギャラリーで [プロパティ インスペクター] を選択します。

畳み込み符号のトレリス表現。符号化率 K / N の符号に対するトレリス表現を含む構造体として指定します。K は入力ビット ストリーム数を表し、N は出力ビット ストリーム数を表します。

トレリス構造体は、関数 poly2trellis を使用して作成するか、手動で作成することができます。この構造体の詳細については、Trellis Description of a Convolutional Codeおよび関数 istrellis を参照してください。

トレリス構造体には次のフィールドがあります。

符号化器への入力シンボルの数。2K と等しい整数として指定します。ここで、K は入力ビット ストリームの数です。

符号化器からの出力シンボルの数。2N と等しい整数として指定します。ここで、N は出力ビット ストリームの数です。

符号化器内の状態の数。2 のべき乗として指定します。

現在の状態と現在の入力のすべての組み合わせの次の状態。整数の行列として指定します。行列のサイズは numStates 行 2K 列でなければなりません。

現在の状態と現在の入力のすべての組み合わせの出力。8 進数の行列として指定します。行列のサイズは numStates 行 2K 列でなければなりません。

符号化フレームの終了方法。以下のいずれかのモードの値を指定します。

Continuous— ブロックは各入力の終わりの符号化器の状態を次のフレームで使用するために保持します。Truncated (reset every frame)— ブロックは各入力を個別に処理します。各入力フレームの開始時に、符号化器の状態はすべて 0 の状態にリセットされます。または、[Specify initial state via input port] を選択した場合は、ISt端子で指定された状態にリセットされます。Terminate trellis by appending bits— ブロックは各入力を個別に処理します。個々の入力フレームごとに追加のビットを使用することで、符号化器の状態を各フレームの終了時にすべて 0 の状態にリセットします。出力の長さは、y = N × (x + s) / K で与えられます。ここで x は入力ビットの数、s = constraint length – 1 (複数の拘束長の場合は s =sum(constraint length(i) – 1)) です。メモ

このブロックは K ≥ 1 の場合に機能します。ここで、ブロックは各入力ストリームで拘束長に同じ値を取ります。たとえば、拘束長 [2 2] または [7 7] は機能しますが、[5 4] は機能しません。

Reset on nonzero input via port— ブロックにRstとラベル付けされた追加の入力端子が表示されます。このRstの入力が非ゼロ値となると、符号化器はすべてゼロの状態にリセットします。

メモ

このブロックがシミュレーション中に長さが変わるシーケンスを出力し、[Operation mode] を [Truncated (reset every frame)] または [Terminate trellis by appending bits] に設定した場合、ブロックの状態は入力タイム ステップごとにリセットされます。

符号化データの計算後にブロックをリセットするには、このパラメーターを選択します。リセット アクションの遅延により、このブロックは HDL コード生成をサポートできます。HDL コードを生成するには、HDL Coder™ ソフトウェアが必要です。

依存関係

このパラメーターは、[Operation mode] パラメーターを [Reset on nonzero input via port] に設定したときにのみ表示されます。

ブロックに ISt 入力端子を追加するには、このパラメーターを選択します。

依存関係

このパラメーターは、[Operation mode] パラメーターを [Truncated (reset every frame)] に設定したときにのみ表示されます。

ブロックに FSt 出力端子を追加するには、このパラメーターを選択します。

依存関係

このパラメーターは、[Operation mode] パラメーターを [Continuous]、[Truncated (reset every frame)]、または [Reset on nonzero input via port] に設定したときにのみ表示されます。

[Puncture vector] 端子を表示して有効にするには、このパラメーターを選択します。

詳細

畳み込み符号化は、メモリがある誤り制御符号化です。具体的には、計算と符号化される出力が、入力シンボルの現在のセットに加え、前の入力シンボルのいくつかにも依存します。依存する入力シンボルの数は、トレリスの構成に応じて異なります。畳み込み符号化器は、K 個の入力ビットごとに N ビットを出力します。入力は、シミュレーション全体で K ビットのさまざまな倍数になることがあります。

一連の生成多項式を定義する MATLAB® トレリス構造体を使用して、非組織、組織フィードフォワード、または組織フィードバック畳み込み符号をモデル化できます。さまざまな畳み込みコード アーキテクチャを示す詳細と例については、Convolutional Codesのトピックを参照してください。

畳み込み符号化された出力の復号化には以下を使用できます。

Viterbi Decoder ブロック — 硬判定と軟判定の復号化でビタビ アルゴリズムを使用

APP Decoder ブロック — 畳み込み符号の軟出力復号化に "事後" 確率復号化器を使用

畳み込み符号化器の定義には、[Trellis structure] パラメーターを使用します。関数 poly2trellis の呼び出しでトレリス構造体を指定できます。詳細については、Trellis Description of a Convolutional Codeを参照してください。

たとえば、符号化器を拘束長 7 で使用し、符号生成多項式を 171 と 133 (8 進数)、フィードバック接続多項式を 171 (8 進数) とするには、[Trellis structure] パラメーターを次のように設定します。

poly2trellis(7,[171 133],171)

poly2trellis への同じ呼び出しで MATLAB ワークスペース変数を初期化し、[Trellis structure] パラメーターでその変数名を指定します。[Trellis structure] パラメーターで関数 poly2trellis を呼び出すのではなく、トレリス構造体を含むワークスペース変数を使用して [Trellis structure] パラメーターを指定した場合、Simulink が各シミュレーションの開始時にダイアグラムを更新する時間が短縮されます。

[Operation mode] パラメーターを使用して、操作モードと開始レジスタの状態を指定します。

参照

[1] Clark, George C., and J. Bibb Cain. Error-Correction Coding for Digital Communications. Applications of Communications Theory. New York: Plenum Press, 1981.

[2] Gitlin, Richard D., Jeremiah F. Hayes, and Stephen B. Weinstein. Data Communications Principles. Applications of Communications Theory. New York: Plenum Press, 1992.

[3] Yasuda, Y., K. Kashiki, and Y. Hirata. “High-Rate Punctured Convolutional Codes for Soft Decision Viterbi Decoding.” IEEE® Transactions on Communications 32, no. 3 (March 1984): 315–19. https://doi.org/10.1109/TCOM.1984.1096047.

[4] Haccoun, D., and G. Begin. “High-Rate Punctured Convolutional Codes for Viterbi and Sequential Decoding.” IEEE Transactions on Communications 37, no. 11 (November 1989): 1113–25. https://doi.org/10.1109/26.46505.

[5] Begin, G., D. Haccoun, and C. Paquin. “Further Results on High-Rate Punctured Convolutional Codes for Viterbi and Sequential Decoding.” IEEE Transactions on Communications 38, no. 11 (November 1990): 1922–28. https://doi.org/10.1109/26.61470.

拡張機能

C/C++ コード生成

Simulink® Coder™ を使用して C および C++ コードを生成します。

メモ

HDL 用に最適化され、ハードウェア フレンドリーな制御信号をもつ畳み込み符号化器には、Convolutional Encoder (Wireless HDL Toolbox) ブロックを使用します。Wireless HDL Toolbox™ ブロックを使用すると、Simulink で HDL アルゴリズムのレイテンシをシミュレートすることもできます。

HDL Coder は、HDL の実装および合成ロジックに影響を与える、追加の構成オプションを提供します。

このブロックは 1 つの既定の HDL アーキテクチャをもっています。

| ConstrainedOutputPipeline | 設計内で既存の遅延を移動することによって出力に配置するレジスタの数。分散型パイプラインは、これらのレジスタを再分散しません。既定の設定は |

| InputPipeline | 生成コードに挿入する入力パイプライン ステージの数。分散型パイプラインと制約付き出力パイプラインは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成コードに挿入する出力パイプライン ステージの数。分散型パイプラインと制約付き出力パイプラインは、これらのレジスタを移動できます。既定の設定は |

入力データの要件:

スカラー入力でなければなりません。

booleanデータ型またはufix1データ型でなければなりません。

HDL Coder は、以下の符号化率のみをサポートします。

½ ~ 1/7

2/3

HDL Coder は 3 ~ 9 の拘束長のみをサポートします。

関数

poly2trellisで [Trellis structure] を指定します。HDL Coder は、以下の [Operation mode] 設定をサポートしています。

ContinuousReset on nonzero input via portこのモードを選択した場合、[Delay reset action to next time step] オプションを選択しなければなりません。このオプションを選択すると、Convolutional Encoder ブロックは、リセットを実行する前に現在の計算を終了します。

Resettable Synchronous Subsystem (HDL Coder) 内で、このブロックの HDL を生成することはできません。

バージョン履歴

R2006a より前に導入

参考

ブロック

関数

オブジェクト

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)