このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

cosimulationConfiguration

説明

cosimulationConfiguration オブジェクトは、指定された HDL モジュールの HDL Cosimulation ブロックまたは System object™ の作成を制御します。

作成

構文

説明

cosimObj = cosimulationConfiguration(HDLSimulator,SubWorkflow,HDLTopLevelName)HDLSimulator、SubWorkflow、および HDLTopLevelName 値を持つ cosimulationConfiguration オブジェクトを作成します。

このワークフローは、HDL Cosimulation ブロックまたは hdlverifier.HDLCosimulation System object を作成するために コシミュレーション ウィザード を使用する代わりに使用するコマンドラインです。

cosimObj = cosimulationConfiguration(MATfile)cosimulationConfiguration オブジェクトを作成します。

プロパティ

ワークフロー

コシミュレーションに使用する HDL シミュレータ。'ModelSim'、'Xcelium'、'Vivado Simulator'、または 'VCS' として指定されます。

実行するコシミュレーションの種類:

'Simulink'— Simulink®コシミュレーション用の HDL Cosimulation ブロックを作成するようにワークフローを構成します。'MATLAB System Object'— MATLAB®コシミュレーション用のhdlverifier.HDLCosimulationSystem object を作成するようにワークフローを構成します。

文字列または文字ベクトルとして指定された、最上位 HDL モジュールまたはエンティティの名前。

データ型: char | string

HDL コンパイル

文字列または cell 配列として指定された、コシミュレーションに必要な HDL ディレクトリ、ファイル、またはファイル。ファイルの 1 つに既知の HDL ファイル拡張子がない場合、ツールはそれを無視します。

例: './hdlsrc' には hdlsrc ディレクトリのすべてのファイルが含まれます

例: {'./hdlsrc','myModule.v'} には、hdlsrc ディレクトリのすべてのファイルと、myModule.v という名前のローカル ファイルが含まれます。

別のオプションとして、各ファイルの後にファイル タイプが続くリストを指定します。使用可能なファイルの種類はシミュレータによって異なります。

ModelSim™:

Verilog(*.v、*.sv)、VHDL(*.vhd)、ModelSim macro file(*.do)Xcelium™:

Verilog(*.v、*.sv)、VHDL(*.vhd)、Shell script(*.sh)Vivado®:

Verilog(*.v、*.sv)、VHDL(*.vhd)、Vivado XCI file(*.xci)VCS®:

Verilog(*.v、*.sv)、VHDL(*.vhd)、PLI tab file(*.tab)

例: {'mytop.v','Verilog','submod.v','Verilog'}

データ型: char | string | cell array

文字列または文字ベクトルとして指定された HDL シミュレータの場所。システム PATH で指定された場所とは異なる場所でシミュレータを使用する場合は、このオプションを使用します。空の場合は、システム パスが使用されます。

データ型: char | string

VCS vhdlan ツールのフラグを指定します。

依存関係

このプロパティを有効にするには、HDLSimulator を VCS に設定します。

データ型: char | string

VCS vlogan ツールのフラグを指定します。

依存関係

このプロパティを有効にするには、HDLSimulator を VCS に設定します。

データ型: char | string

使用するコンパイル コマンド。文字列または文字ベクトルとして指定します。コンパイル コマンドは、選択したシミュレータと設計ファイル リストに基づいて自動的に生成されます。特定のライブラリにコンパイルする必要がある場合など、必要に応じて異なるコンパイル コマンドを指定できます。

ヒント

ワークフローを 1 回実行して cosimWizard_<TOP>.mat ファイルを生成すると便利です。その後、コンパイル コマンドを変更してこのプロパティを設定できます。

依存関係

HDLSimulator が VCS に設定されている場合、このプロパティは無効になります。

データ型: char | string

HDLパラメーターまたはジェネリックのデフォルト以外の値を指定するには、パラメーターファイルをインクルードします。ファイルを編集してデフォルト値を上書きし、パラメーター値を有効にするために runWorkflow 関数を実行します。次のいずれかのオプションを入力できます。

''—parameter_という名前のデフォルトのパラメーターファイルを生成します。ここで、HDLTopLevelName.cfgHDLTopLevelNameは最上位 HDL モジュールまたはエンティティの名前です。ファイルには各 HDLパラメーターの行が含まれており、すべての行がコメント化されています。runWorkflow関数を実行すると、関数はデフォルトのファイルを生成し、ワークフロー全体にわたって実行を続けます。GENERATE_AND_EDIT— デフォルトのファイル名parameter_で新しいパラメーターファイルを生成します。HDLTopLevelName.cfgrunWorkflow関数を実行すると、パラメーター設定ファイルが生成された後に実行が停止します。ファイルを編集して、関連するパラメーターを含む行のコメントを解除し、その値を変更してデフォルト値を上書きします。次に、コマンドラインでrunworkflow(c)を実行してワークフローを再起動します。filename — ワークフローを実行するときに、指定されたパラメーターファイルを使用します。

このプロパティは、Xcelium または ModelSim とのコシミュレーションの場合にのみ有効です。

ヒント

Vivado シミュレータを使用するときに HDLパラメーターを設定するには、HDLCompilationCommand プロパティを使用します。詳細については、Vivado シミュレーションの HDL パラメータを設定するを参照してください。

データ型: char | string

文字列または文字ベクトルとして指定された、HDL 詳細化ツールのオプション。

依存関係

このプロパティは、VCS または Xcelium とのコシミュレーションに有効です。

データ型: char | string

文字列または文字ベクトルとして指定された、HDL シミュレーション ツールのオプション。

Xcelium のデフォルト値は、64 ビット アプリの使用を強制します。

ModelSim のデフォルト値には、HDL 時間精度を定義し、コシミュレーション用のポートの読み取り/書き込みアクセスを許可するために必要なフラグが含まれています。

依存関係

このプロパティは、Xcelium、VCS、または ModelSim とのコシミュレーションに有効です。

データ型: char | string

HDL タイミング

HDL シミュレーションの時間単位。このユニットは次の構成に影響します。

PreCosimulationRunTimeプロパティSampleTimeプロパティ (MATLAB System object サブワークフロー)クロック端子の周期属性

リセットポートの持続属性

デフォルトの単位は、コンパイル時に HDL シミュレータに時間精度を問い合わせることによって (ModelSim、Xcelium)、または HDLTimePrecision プロパティによって (Vivado) 動的に決定されます。

メモ

出力ポートの SampleTime 属性は Simulink 時間を指定するため、秒単位になります。

シミュレーションを開始する前に HDL シミュレーターを実行する時間 (Simulink または MATLAB、HDLTimeUnit 単位)。この時間により、必要なリセットを実行し、クロック イネーブルをアサートできるようになります。

ワークフローを実行すると、クロック、リセット、およびコシミュレーション開始時間の視覚的なタイミング図がファイル hdlverifier_rstclk_waveform.jpg に作成されます。

最初のコシミュレーションで Simulink 時間と HDL 時間の比率を自動的に決定します。

Simulink サンプル時間は、タイミング スケールを使用して HDL シミュレーション時間に関連付けられます。多くの場合、基本的な Simulink サンプル時間が HDL で最速のクロック周期と等しくなるようにすることが最善の選択となります。このワークフローの実行時にはすべての入力サンプル時間がわかっていないため、すべてのサンプル時間がわかっている最初のシミュレーションでタイムスケールを自動的に決定するように選択できます。

依存関係

このプロパティを有効にするには、Subworkflow を Simulink に設定します。

このプロパティは、VCS とのコシミュレーションでは使用できません。

スケール係数と時間単位として指定して、タイムスケールを手動で設定します: {factor, unit}。

スケールは Simulink の 1 秒に相対的です。Simulink の 1 秒は HDL の {factor, unit} に相当します。係数は double で、単位は 'fs','ps','ns','us','ms' または 's' のいずれかです。デフォルト値は {1, 's'} です。つまり、Simulink 時間は HDL 時間と同じになります。

例: Simulinkのサンプル時間が1秒でHDLクロックが100MHzの場合、Simulinkの1秒がHDLの10nsに等しいタイムスケールを作成します: c.AutoTimeScale = false; c.TimeScale = {10, 'ns'};

依存関係

このプロパティを有効にするには、Subworkflow を Simulink に設定します。

生成された System object の MATLAB サンプル時間を HDLTimeUnit 単位で設定します。すべての入力と出力は MATLAB で同じサンプル時間を共有し、step メソッドの各呼び出しでこの時間が経過します。

デフォルト値は、指定されたクロック周期と出力サンプル時間によって決まります。

依存関係

このプロパティを有効にするには、Subworkflow を MATLAB System Object に設定します。

HDLシミュレータ接続

MATLAB または Simulink を HDL シミュレータに接続するためのチャネルタイプ。Socket または Shared Memory として指定されます。

Socket: MATLAB または Simulink と HDL シミュレータは、指定された TCP/IP ソケットを介して通信します。単一システムおよびネットワーク構成に使用できます。このオプションは最大のスケーラビリティを提供します。TCP/IP ソケット通信の詳細については、TCP/IPソケットポート を参照してください。Shared memory: MATLAB または Simulink と HDL シミュレータは共有メモリを介して通信します。共有メモリ通信により最適なパフォーマンスが提供されます。HDLSimulatorがVCSに設定されている場合、このオプションは使用できません。

ポートインターフェースのプロパティ

正規表現として指定された、ポートをクロックに自動割り当てするための式。MATLAB の正規表現の詳細については、正規表現 を参照してください。

例: 'clk_in$' は、「clk_in」で終わるすべてのポートをクロック端子として割り当てます。

リセットにポートを自動割り当てするための式。正規表現として指定します。MATLAB の正規表現の詳細については、正規表現 を参照してください。

例: c.ResetPortRegularExpression = [c.ResetPortRegularExpress 'rst[0-9]$'] は、リセット ポートのデフォルト式に加えて、"rst" と数値で終わるすべてのポートをリセット ポートとして割り当てます。

正規表現として指定された、ポートを未使用としてラベル付けする式。未使用として割り当てられたポートは、コシミュレーションの一部ではありません。未使用のポートはコシミュレーションインターフェイスに表示されず、駆動もサンプリングもされません。

仕様をクリアするには、信号名の後に空の引数を指定します。

MATLAB の正規表現の詳細については、正規表現 を参照してください。

例: 'clk_out$' は、「clk_out」で終わるポートが未使用であることを示します。

この プロパティ は読み取り専用です。

入力ポートがテーブルとして表示されます。portInterface オブジェクト関数を呼び出して、テーブルの全内容を表示します。

デフォルトは空のテーブルであり、ワークフローによって入力データ ポートが決定されます。クロック、リセット、未使用の正規表現に一致しない入力は、入力データ ポートと見なされます。

specifyInput オブジェクト関数を使用して、入力ポートを明示的に割り当てることができます。

この プロパティ は読み取り専用です。

出力ポートがテーブルとして表示されます。テーブルの各行には、出力ごとに次の情報が含まれています。

出力ポート名

SampleTimeDataTypeSignedFractionLength

DUT 出力に加えて、テーブルには default_output_definition という名前の行が含まれており、出力に割り当てられたデフォルト値が含まれています。

specifyOutput オブジェクト関数を使用して、デフォルトの出力値を変更したり、出力ポートを手動で割り当てたりすることができます。

portInterface オブジェクト関数を呼び出して、テーブルの全内容を表示します。

この プロパティ は読み取り専用です。

クロック端子がテーブルとして表示されます。表の各行には、クロックごとに次の情報が含まれています。

クロック端子の名前

EdgePeriod

DUT クロックに加えて、テーブルにはデフォルトのクロック定義用の default_clock_definition という追加の行が含まれています。

デフォルトのクロック値を変更したり、specifyClock オブジェクト関数を使用してクロックを手動で割り当てたりすることができます。

portInterface オブジェクト関数を呼び出して、テーブルの全内容を表示します。

この プロパティ は読み取り専用です。

リセット ポートがテーブルとして表示されます。表の各行には、リセットごとに次の情報が含まれています。

Name— リセットポートの名前InitialValue— リセットの初期値Duration— リセット信号の持続時間

DUT リセットに加えて、テーブルにはデフォルトのリセット定義用の default_reset_definition という追加の行が含まれています。

デフォルトのリセット値を変更したり、specifyReset オブジェクト関数を使用してリセットを手動で割り当てたりすることができます。

portInterface オブジェクト関数を呼び出して、テーブルの全内容を表示します。

この プロパティ は読み取り専用です。

未使用のポートがテーブルとして表示されます。portInterface オブジェクト関数を呼び出して、テーブルの全内容を表示します。

デフォルトは空のテーブルであり、ワークフローによって未使用のポートが決定されます。未使用の正規表現に一致するポートは未使用とみなされます。

specifyUnused オブジェクト関数を使用すると、ポートを未使用として明示的にラベル付けできます。

オブジェクト関数

portInterface | ポートの仕様の表示 |

runWorkflow | 協調シミュレーションワークフローを実行し、必要な成果物を生成する |

specifyClock | クロックポートをコシミュレーションブロックまたはSystem objectに割り当てる |

specifyInput | HDL入力ポートをコシミュレーションブロックまたはSystem objectに割り当てる |

specifyOutput | HDL出力ポートをコシミュレーションブロックまたはSystem objectに割り当てる |

specifyReset | リセットポートをコシミュレーションブロックまたはSystem objectに割り当てる |

specifyUnused | HDLポートを未使用ポートとしてラベル付けする |

例

この例では、コマンドライン インターフェイスを使用して Simulink ® でレイズド コサイン フィルターをコシミュレートする方法を示します。これは、Simulink HDL コシミュレーション入門 と同じワークフローに従ってコシミュレーション成果物を生成しますが、コシミュレーションウィザードの代わりにコマンド ラインを使用します。

コシミュレーションワークフローを構成する

コシミュレーション構成オブジェクトを作成します。

c = cosimulationConfiguration('ModelSim','Simulink','rcosflt_rtl');

HDL ファイルを設定します。

c.HDLFiles = {'./rcosflt_rtl.v','Verilog'};

filter_out ポートを符号付き固定小数点データ型の出力として設定し、小数部の長さを 29 に設定します。

specifyOutput(c,'filter_out',Datatype='Fixedpoint',Signed=true,FractionLength=29)

クロックの周期を 20 ns に設定し、リセット期間を 15 ns に設定します。

specifyClock(c,'clk',Period=20) specifyReset(c,'reset',Duration=15)

ポート テーブルを表示します。出力、クロック、リセット属性に対して行われた設定が反映されます。その他の設計ポートはデフォルトの属性を取得します。

portInterface(c);

----- Input Data Ports -----

0×1 empty table

Name

____

----- Output Data Ports -----

2×5 table

Name SampleTime DataType Signed FractionLength

_____________________________ __________ ______________ ______ ______________

{'default_output_definition'} 1 {'Inherit' } false 0

{'filter_out' } 1 {'Fixedpoint'} true 29

----- Clock Ports -----

2×3 table

Name Edge Period

____________________________ __________ ______

{'default_clock_definition'} {'Rising'} 10

{'clk' } {'Rising'} 20

----- Reset Ports -----

2×3 table

Name InitialValue Duration

____________________________ ____________ ________

{'default_reset_definition'} 1 8

{'reset' } 1 15

----- Unused Ports -----

0×1 empty table

Name

____

HDL Cosimulation ブロックを生成する

ワークフローを実行して、HDL Cosimulation ブロックと付随するファイルを生成します。

runWorkflow(c);

-------------------- Step 1------------------

Select the type of cosimulation you want to do.If the HDL simulator executable you want to use is not on the system path in your environment you must specify its location.

-------------------- Step 2------------------

Add all VHDL, Verilog, and/or script files to be used in cosimulation to the following table. If the file type cannot be automatically detected or the detection result is incorrect, specify the correct file type in the table. If possible, we will determine the compilation order automatically using HDL simulator provided functionality. Then the HDL files can be added in any order.

-------------------- Step 3------------------

HDL Verifier has automatically generated the following HDL compilation commands. You can customize these commands with optional parameters as specified in the HDL simulator documentation but they are sufficient as shown to compile your HDL code for cosimulation. The HDL files will be compiled when you click Next.

Compiling HDL design. Please wait ...

###Compiling HDL design

Reading pref.tcl

# 2024.2

# do hdlverifier_compile_design.do

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# Loading project compile_project

# .

# QuestaSim-64 vlog 2024.2 Compiler 2024.05 May 20 2024

# Start time: 14:09:05 on Aug 29,2025

# vlog -work work -vopt C:/Users/user/OneDrive - MathWorks/Documents/MATLAB/ExampleManager/user.Bdoc25b.j2987061/hdlverifier-ex80882452/rcosflt_rtl.v

# -- Compiling module rcosflt_rtl

#

# Top level modules:

# rcosflt_rtl

# End time: 14:09:07 on Aug 29,2025, Elapsed time: 0:00:02

# Errors: 0, Warnings: 0

# Compile of rcosflt_rtl.v was successful.

# All compile dependencies have been resolved.vlog -work work -vopt -stats=none {C:/Users/user/OneDrive - MathWorks/Documents/MATLAB/ExampleManager/user.Bdoc25b.j2987061/hdlverifier-ex80882452/rcosflt_rtl.v}

# reading E:/share/apps/HDLTools/ModelSim/questasim-2024.2/Windows/win64/../modelsim.ini

# QuestaSim-64 vlog 2024.2 Compiler 2024.05 May 20 2024

# -- Compiling module rcosflt_rtl

#

# Top level modules:

# rcosflt_rtl

...done

-------------------- Step 4------------------

Use 'Shared Memory' communication method if your firewall policy does not allow TCP/IP socket communication.

Elaborating and Loading HDL simulation image. Please wait ...

Waiting for HDL Simulator to startup ...

120 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

119 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

118 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

117 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

116 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

115 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

114 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

113 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

112 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

...done

-------------------- Step 5------------------

Specify all input and output port types. Input signals that are identified as 'Clock' and 'Reset' signals will be forced in the HDL simulator through Tcl commands. You can specify the timing parameters for forced 'Clock' and 'Reset' signals in the next step. If you want to drive your HDL clock and reset signals with Simulink signals, mark them as 'Input'.

-------------------- Step 6------------------

Set the sample time and data type for each output port. You can specify the sample time as -1, which means that it will be inherited via back propagation in the Simulink model. Back propagation may fail in certain circumstances; click Help for details.

-------------------- Step 7------------------

Set clock and reset parameters here. The time in these tables refers to time in the HDL simulator.

Please wait while generating waveforms.

...done

-------------------- Step 8------------------

The diagram below shows the current settings for forced 'Clock' and 'Reset' signals. The red line represents the time in the HDL simulation at which MATLAB/Simulink will start (i.e. cosimulation will start).

To change the MATLAB/Simulink start time relative to the HDL simulation time, enter the new start time below. To avoid a race condition, make sure the start time does not coincide with the active edge of any clock signal. You can do so by moving the start time or by changing the clock active edge in the previous step (click Back).

-------------------- Step 9------------------

When you click Finish, the Cosimulation Wizard performs the following actions:

- Creates and opens a new Simulink model containing an HDL Cosimulation block configured to your specifications.

- Generates the scripts to compile your HDL code and launch the HDL simulator according

to the choices you made with this assistant.

- (If you check the box below) Configures the HDL Cosimulation block to assist you in setting the timescale

when you cosimulate the block for the first time.

- (If you uncheck the box below) The timescale is set to the default setting of 1 Simulink second = 1 second in the HDL simulator

or you may change it below.

Generating blocks ... Please wait.

Warning: The model name 'hdlverifier_wizard_rcosflt_rtl' is shadowing another

name in the MATLAB workspace or path. Type "which -all

hdlverifier_wizard_rcosflt_rtl" at the command line to find the other uses of

this name. You should change the name of the model to avoid problems.

...done

ワークフローはステップを実行し、hdlverifier_wizard_rcosflt_rtl.slx という名前の Simulink モデルを生成します。このモデルには、HDL Cosimulation ブロックと、コンパイルおよび HDL シミュレータとの通信用の 2 つの追加ブロックが含まれています。

提供されたテストベンチ モデルを開きます。

open_system('rcosflt_tb.slx')

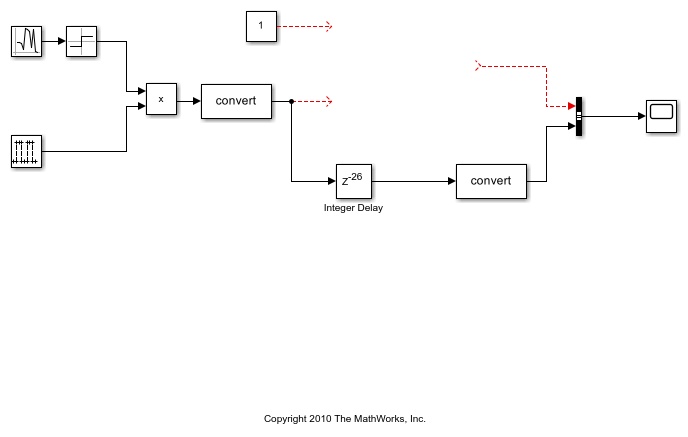

生成された HDL Cosimulation ブロックをキャンバスにドラッグし、その入力と出力をテストベンチに接続します。モデルは次の図のようになります。

コシミュレーションを実行してHDL設計を検証する

Launch HDL Simulator というラベルの付いたブロックをダブルクリックして、HDL シミュレータを起動します。

HDL シミュレータの準備ができたら、Simulink に戻り、シミュレーションを開始します。

タイムスケールを決定します。

AutoTimeScaleプロパティはシミュレーションの開始時にタイムスケールを自動的に決定するように設定されているため、HDL Verifier はシミュレーションを開始する代わりに、タイムスケールの詳細グラフィカル インターフェイスを起動します。HDL シミュレータと Simulink はどちらもfilter_inポートとfilter_outポートを 1 秒ごとにサンプリングします。ただし、HDL シミュレータでのサンプル時間はクロック周期 (20 ns) と同じである必要があります。/rcosflt_rtl/clkの Simulink サンプル時間を 1 (秒) に変更し、Enter を押します。その後、ウィザードはテーブルを更新します。次の図は新しいタイムスケールを示しています。Simulink の 1 秒は、HDL シミュレータの 2e-008 秒に相当します。

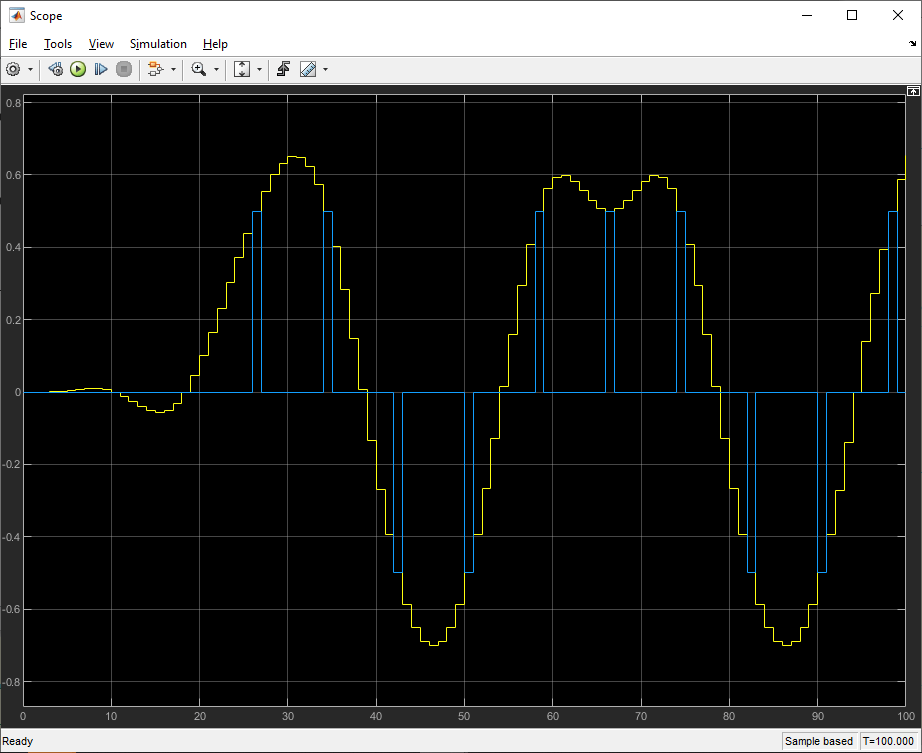

4. OK をクリックして、[タイムスケールの詳細] ダイアログ ボックスを閉じます。Simulink シミュレーションを再起動し、テストベンチ モデルのスコープからの結果を確認します。

スコープには、レイズド コサイン フィルターへの入力の遅延バージョンとそのフィルターの出力の両方が表示されます。このフィルタの出力を直接サンプリングすると、シンボル間干渉は発生しません。

制限

MATLAB リリースで生成した

.matファイルは、他のリリースでも動作することは保証されません。異なる MATLAB リリースの場合は、デザインに必要なカスタマイズを使用して コシミュレーション ウィザード ワークフローを完了まで実行し、.matファイルを再生成します。

バージョン履歴

R2022b で導入MATLAB System object ワークフローを使用する場合、出力ポートのデフォルトのデータ型は Fixedpoint Unsigned です。以前のリリースでは、デフォルトは Fixedpoint Signed でした。

Synopsys® VCS および MATLAB と共シミュレートします。

パラメータ化された HDL 設計をインポートします。HDLパラメーターの値を設定するには、パラメーターファイルを指定または編集します。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)