このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

コシミュレーションで HDL パラメータを使用する

コシミュレーションでは、Verilog パラメータまたは VHDL ジェネリックを設定できます。cosimulationConfiguration オブジェクトの HDLParameterFile プロパティまたは Cosimulation Wizard の HDL パラメータ ファイル ファイルを使用して、次の操作を行います。

既知のパラメータに値を割り当てる独自のパラメータ ファイルを提供します。デザイン階層内のパラメータがわかっていて、使用したい特定の設定がある場合にこのオプションを使用します。

パラメータ値がコメントアウトされたデフォルトのパラメータ ファイルを生成します。

パラメータ ファイルを生成し、それを編集してデフォルトのパラメータ値を上書きします。

この機能は Vivado® コシミュレーションではサポートされていません。Vivado コシミュレーションのパラメータを手動で設定するには、Vivado シミュレーションの HDL パラメータを設定する を参照してください。

パラメータファイルの生成と編集

Simulation Options ペインで、Parameter file フィールドにファイル名を指定します。

Generate をクリックすると、デフォルトのパラメータ値を持つ新しいパラメータ ファイルが作成されます。

Editをクリックします。開いたファイルで、上書きするパラメータを含む行のコメントを解除し、その値を設定します。

構成ファイルには、各 HDL パラメータの行が含まれており、デフォルト値が割り当てられています。設定するパラメータの行のコメントを解除し、デフォルト値を上書きする値を割り当てます。

たとえば、ModelSim® コシミュレーション用に生成されたこの構成ファイルを考えてみます。

# Uncomment lines below for any parameter whose default value you want to change. # For parameters marked "N/A" (not available) the default value could not be # determined, but you can override in the same way. #-G/design_top/coeff1=0 #-G/design_top/coeff2=18 #-G/design_top/coeff3=74coeff1の値を 32 に変更するには、その行のコメントを解除し、値 32 を割り当てます。-G/design_top/coeff1=32 #-G/design_top/coeff2=18 #-G/design_top/coeff3=74同様に、Xcelium™ とコシミュレーションする場合、ジェネリックとパラメータの値の割り当てを強制するために、構成ファイル内のパラメータが

-gpgディレクティブを使用して作成されます。-gpg "design_top.coeff1=120 #-gpg "design_top.coeff2=18 #-gpg "design_top.coeff3=74

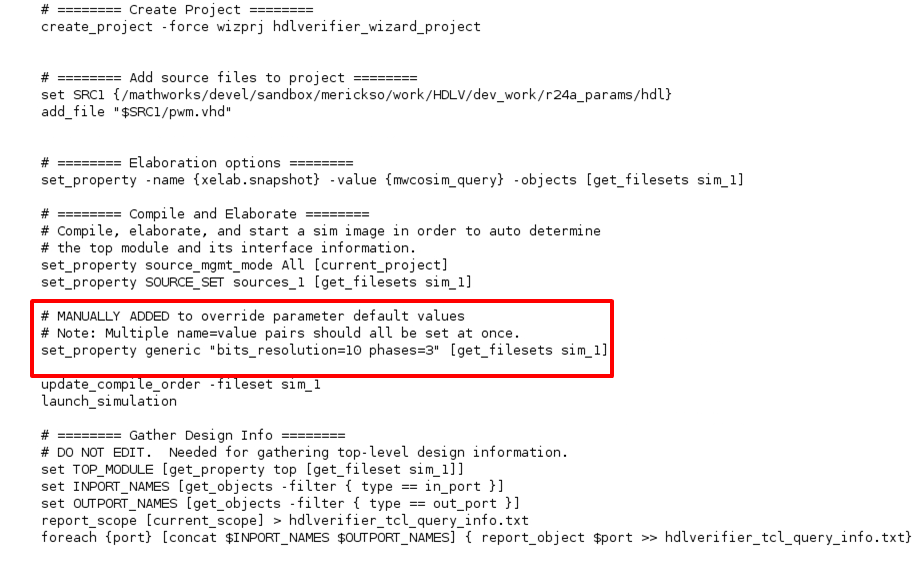

Vivado シミュレーションの HDL パラメータを設定する

Vivado シミュレータを使用するときに HDL パラメータを設定するには、cosimulationConfiguration オブジェクトの HDLCompilationCommand プロパティを使用します。または、Cosimulation Wizard の コンパイル コマンド フィールドを編集します。たとえば、デフォルトのコンパイル コマンドを編集して、赤で強調表示されている bits_resolution および phases というラベルの付いたジェネリックの値を設定します。

メモ

複数のパラメータまたはジェネリックを設定する場合は、すべてを 1 つのコマンドで設定する必要があります。

HDLパラメータでサポートされるデータ型

サポートされている Verilog データ型

整数 — 最大 32 ビット

実数

文字列 — 最大256バイト

サポートされているVHDLデータ型

整数

実数

文字列 — 最大256バイト

時間

ビット

boolean

Enum

標準ロジック

パラメータ化されたポートサイズによるコシミュレーション

Simulink® コシミュレーションでは、HDL デザインに入力ポートまたは出力ポートの幅を設定するパラメータが含まれている場合、Cosimulation Wizard はそのポート幅のデフォルト値を持つ HDL Cosimulation ブロックを作成します。ポート幅を変更するには、そのパラメータに新しい値を割り当てて、Cosimulation Wizard を再実行します。ブロックを生成した後にデフォルト値を上書きする場合は、次の手順に従う必要があります (Vivado ではサポートされていません)。

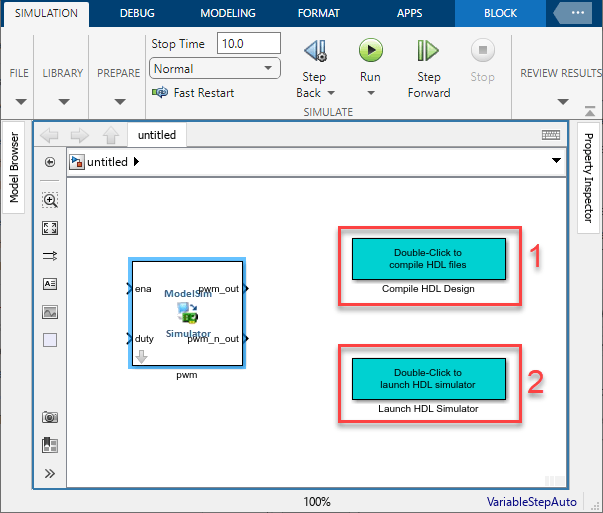

parameter_ファイルを編集し、パラメータ値を上書きして、必要なポート幅を反映します。たとえば、DUT.cfgoutput_widthパラメータを8に変更します。-G/design_top/output_width=8HDL シミュレータが開いていないことを確認してください。HDL Cosimulation ブロックを生成した後に開く Simulink キャンバスで、Compile HDL Design というラベルの付いたブロックをダブルクリックして、HDL デザインを再コンパイルします。次に、Launch HDL Simulator というラベルの付いたブロックをダブルクリックして、HDL シミュレーターを起動します。

HDL シミュレータが開いてデザインをロードしたら、HDL Cosimulation ブロック マスクを開きます。Ports タブで各ポートを選択し、テーブルが空になるまで Delete をクリックします。

Auto Fill をクリックし、開いた Auto Fill ペインに DUT へのパスを入力します。

Fillをクリックします。ポート リストに新しいパラメータ値が反映されます。

このポート リストには、変更されたポート幅を持つ HDL ポートと、クロックおよびリセット用のポートが含まれます。Simulink には暗黙的なクロックとリセットがあるため、リストからこれらの 2 つのポートを選択して削除できます。

共同シミュレーション活動を継続します。ブロックを再生成しないでください。