このページは前リリースの情報です。該当の英語のページはこのリリースで削除されています。

Xilinx Zynq プラットフォーム

Xilinx®

Zynq®-7000 プラットフォームの HDL コードと組み込みソフトウェアの生成と展開

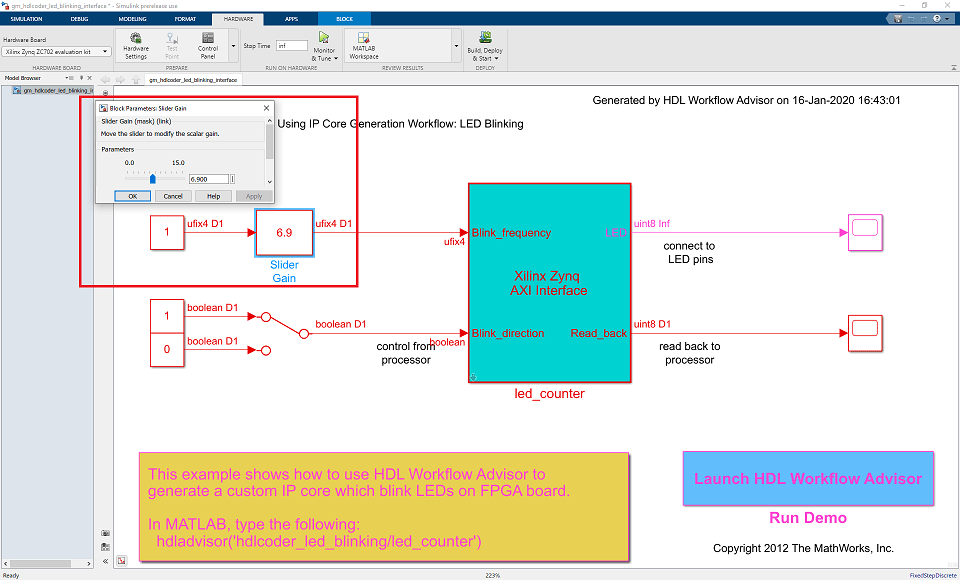

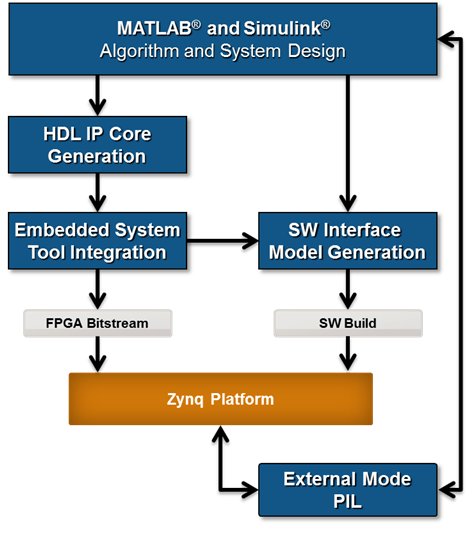

HDL Coder™ では IP コアを生成して Vivado® プロジェクトに組み込み、Zynq ハードウェアをプログラムできます。Embedded Coder® を使用すると、組み込みソフトウェアを生成してビルドし、ARM® プロセッサで実行できます。SoC プラットフォーム向けのハードウェア ソフトウェア協調設計ワークフローを参照してください。

設計を Zynq ハードウェアに展開するには、HDL Coder Support Package for Xilinx Zynq Platformをインストールしなければなりません。インストールについては、HDL Coder でサポートされているハードウェアを参照してください。

HDL Coder Support Package for Xilinx Zynq Platform では、Xilinx Vivado または Xilinx ISE を使用して FPGA 設計に統合できる IP コアの生成がサポートされています。Embedded Coder Support Package for Xilinx Zynq Platform と組み合わせて使用することで、このソリューションでは C および HDL コード生成を使用して Xilinx Zynq SoC をプログラムできます。ハードウェア ソフトウェア協調設計ワークフローはシミュレーション、プロトタイピング、検証、および実装にまたがります。

カテゴリ

- セットアップと構成

サードパーティの EDA ツールおよびサポートされるハードウェアで使用するサポート パッケージをダウンロードしてインストールする

- ハードウェア ソフトウェア協調設計の基礎

ハードウェア ソフトウェア協調設計ワークフローについて、およびワークフロー アドバイザーを使用して SoC プラットフォームでアルゴリズムを実行する方法について説明する

- モデル化

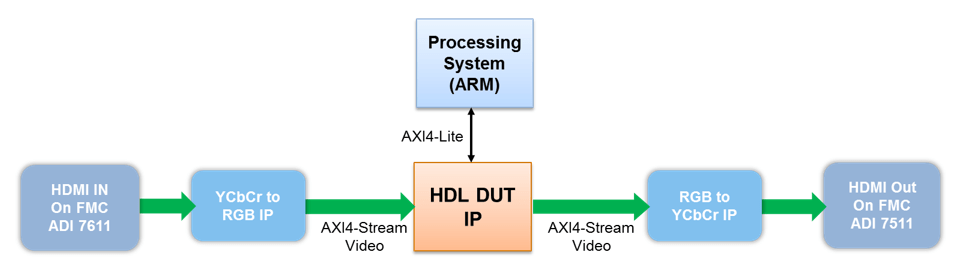

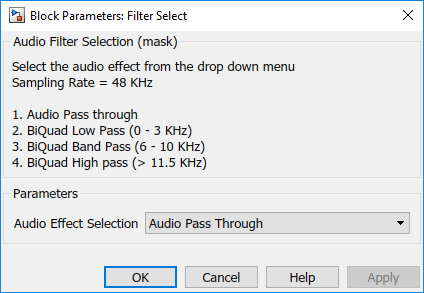

AXI4-Stream、AXI4-Stream Video、または AXI4 Master インターフェイスへのマッピングに簡易プロトコルを使用して Simulink® でアルゴリズムをモデル化する

- カスタム IP コアの生成

既定のシステム リファレンス設計またはボードに登録されたカスタム リファレンス設計への展開用に DUT から HDL IP コアを生成する

- カスタム ボードとリファレンス設計

Xilinx Zynq プラットフォーム用のカスタム リファレンス設計またはカスタム ボードを定義して登録する

- 展開と検証

ユーザー プログラミングを含むビットストリームを作成し、Xilinx Zynq プラットフォームにダウンロードする

関連情報

- Xilinx Zynq プラットフォーム (Embedded Coder)

- IP コアおよびビットストリームの生成

- カスタム ハードウェア プラットフォームの作成