このページは前リリースの情報です。該当の英語のページはこのリリースで削除されています。

カスタム IP コアの生成

既定のシステム リファレンス設計またはボードに登録されたカスタム リファレンス設計への展開用に DUT から HDL IP コアを生成する

HDL Coder™ は、デバイスに展開できるカスタム HDL IP コアを生成できます。生成された IP コアを既定のシステム リファレンス設計またはボードに登録した独自のカスタム リファレンス設計に統合できます。

トピック

- Generate an IP Core for Xilinx SoC Devices from MATLAB

IP core generation for Xilinx® SoC Devices from MATLAB®.

- Generate an IP Core for Xilinx SoC Devices from Simulink

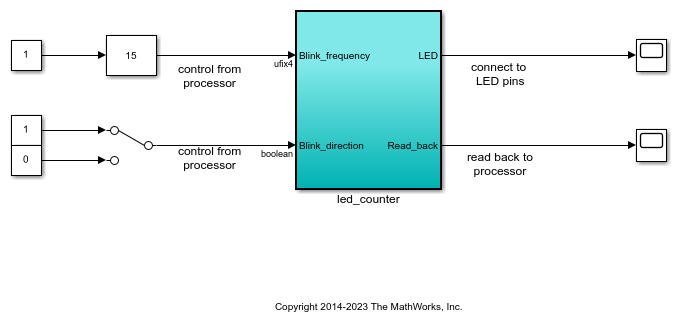

IP core generation for Xilinx SoC Devices from Simulink®.

- カスタム IP コアの生成

HDL ワークフロー アドバイザーを使用し、モデルまたはアルゴリズムからカスタム IP コアを生成します。

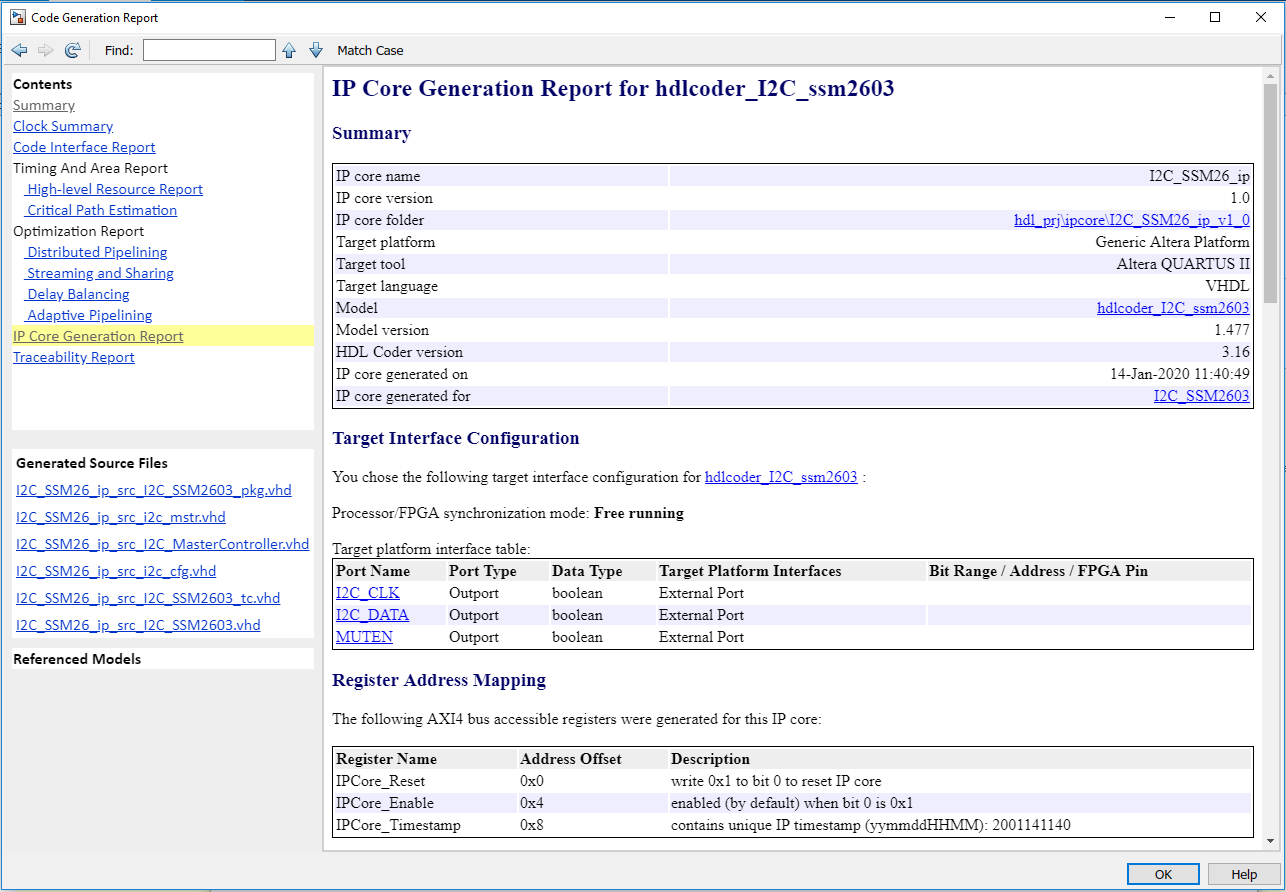

- カスタム IP コア レポート

既定では、カスタム IP コアの生成時に HTML カスタム IP コア レポートが生成されます。

- リファレンス設計の合成を高速化するための IP キャッシュ

IP キャッシュを使用し、Out-Of-Context ワークフローを使用してリファレンス設計の合成時間を高速化します。

トラブルシューティング

IP コアの生成ワークフローと Simulink Real-Time FPGA I/O ワークフローでのタイミング エラーの解決

Vivado ベースのボードでの IP コアの生成ワークフローまたは Simulink Real-Time FPGA I/O ワークフローの [FPGA ビットストリームのビルド] ステップにおけるタイミング エラーを解決します。