FPGA および SoC ハードウェアをターゲットにする方法の概要

アルゴリズムを設計して特にハードウェアに展開する手順に従って、FPGA または SoC デバイスをターゲットにします。Simulink® モデルまたは MATLAB® 関数から始めて、ターゲットにするハードウェア プラットフォームを選択し、ハードウェア ソフトウェア協調設計ワークフローに従います。次の手順を繰り返すことにより、設計を分割して展開する最適な方法を調べます。

ターゲット プラットフォームを選択します。設計を Simulink でモデル化するか MATLAB 関数としてモデル化したら、設計の展開先にするターゲット プラットフォームを決定します。以下を検討します。

ターゲットにするデバイスのタイプ: スタンドアロン FPGA、SoC デバイス、または個別の FPGA やプロセッサをもつプラットフォーム

デバイス タイプ 推奨ワークフロー スタンドアロン FPGA FPGA にのみ展開する場合は、ハードウェア ソフトウェア協調設計ワークフローの最初の部分 (FPGA 用の HDL アルゴリズムのプロトタイプ作成と展開) のみを使用します。 SoC デバイス モデルを SoC デバイスに展開するには、FPGA 用のハードウェア部分とプロセッサ用の組み込みソフトウェア部分を含むように設計を分割する必要があります。これは、ハードウェア ソフトウェア モデルと呼ばれます。FPGA には物理接続を変更するためのビットストリーム (モデルのハードウェア部分) が必要であり、プロセッサには実行可能ファイル形式の一連の新しい命令 (モデルのソフトウェア部分) が必要です。 Simulink Real-Time™ FPGA I/O モジュール このタイプのプラットフォームは、プロセッサとして動作する Speedgoat® ターゲット マシンと FPGA IO モジュールを参照します。FPGA および SoC ハードウェアをターゲットにする手順を使用して、FPGA とプロセッサの両方をプログラムできます。詳細については、Speedgoat Simulink プログラム可能 I/O モジュール向けの IP コアの生成ワークフローを参照してください。 現在の開発段階: ラピッド プロトタイピングまたは量産

ラピッド プロトタイピングでは、HDL Coder™ でサポートされる既存のターゲット デバイスを選択して開発時間を短縮します。その後すぐに、ハードウェア ソフトウェア協調設計ワークフローの使用を開始できます。HDL Coder でサポートされているハードウェアを参照してください。

量産、またはサポートされていないデバイスでのラピッド プロトタイピングでは、まずカスタム ハードウェア プラットフォームを作成してから、ハードウェア ソフトウェア協調設計ワークフローに従います。カスタム ハードウェア プラットフォームの作成を参照してください。

ハードウェア ソフトウェア協調設計

ハードウェア ソフトウェア協調設計ワークフローは次の 2 つの段階に分けられます。

FPGA 用の HDL アルゴリズムのプロトタイプ作成と展開

ターゲット ハードウェアへの展開用にモデルを準備します。HDL Coder は、デバイスの FPGA に展開する設計から生成された HDL コードを含む IP コアおよびビットストリームを生成します。その後、IP コアを実行し、ターゲット ハードウェア上で機能することを検証できます。この段階は、スタンドアロン FPGA デバイス、SoC デバイス、または個別の FPGA やプロセッサをもつプラットフォームをターゲットにするために使用できます。

プロセッサ用の C アルゴリズムの展開

プロセッサ用の C コードを生成して FPGA とプロセッサ間の接続を構成することで、ハードウェア ソフトウェア インターフェイスを構成します。

FPGA と組み込みプロセッサを含むプラットフォーム (SoC デバイスなど) で実行するためにハードウェア コンポーネントと組み込みソフトウェア コンポーネントに分割した設計を展開します。この設計は、HDL コードを含む IP コアおよびビットストリームを生成する DUT アルゴリズムと、プロセッサで実行する組み込みコードを生成するソフトウェア コンポーネントで構成されます。生成されたソフトウェア インターフェイス モデルと、AXI インターフェイスなどのハードウェア インターフェイスのコンポーネントを含む IP コアを使用して、ハードウェア コンポーネントとソフトウェア コンポーネントの間のインターフェイスとします。

FPGA 用の HDL アルゴリズムのプロトタイプ作成と展開

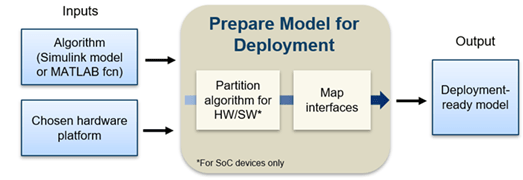

展開用モデルの準備

ターゲット デバイスに展開可能なアルゴリズムのモデルと設計に関するタスクの概要は次のとおりです。

プロセッサと FPGA を含むプラットフォーム (SoC デバイスなど) を使用する場合は、設計をターゲット ハードウェアのハードウェア コンポーネントとソフトウェア コンポーネントに分割します。設計を分割して、FPGA を対象とするハードウェア、および組み込みプロセッサで実行するソフトウェアを生成できます。

モデルの入力と出力を AXI4 インターフェイス、プッシュ ボタン、LED などのハードウェア インターフェイスにマッピングします。生成された設計は、展開するとハードウェア システムの残りの部分と通信できます。詳細については、ターゲット プラットフォーム インターフェイスを参照してください。

モデルを展開用に準備する例については、Simulink モデルからの IP コアの生成入門を参照してください。

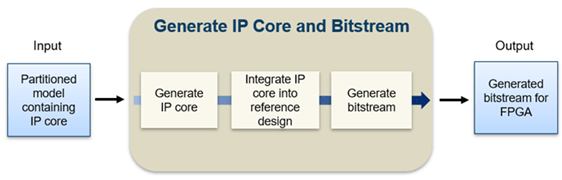

IP コアおよびビットストリームの生成

設計を展開用に準備したら、HDL ワークフロー アドバイザーを使用して次のことができます。

ボードに依存しない、汎用 Xilinx® または Intel® HDL IP コアを生成します。IP コアは、特定の関数 (通常はアルゴリズム) を実装する共有可能で再利用可能な HDL コンポーネントです。IP コアは、IP コア定義ファイル、アルゴリズムについて生成された HDL コード、レジスタ アドレス マップを含む C ヘッダー ファイル、および IP コア レポートで構成されます。例については、ボードに依存しない HDL IP コアの Simulink モデルからの生成を参照してください。

Xilinx Vivado® IP インテグレーターまたは Intel Qsys を使用して、スタンドアロン FPGA ボードまたは SoC プラットフォームをターゲットにするために、IP コアをリファレンス設計に統合します。リファレンス設計には、ハードウェア ソフトウェア モデルから生成するカスタム IP コアと組み込みソフトウェアを除く、Intel または Xilinx ソフトウェアで設計を SoC プラットフォームに展開するために必要な要素が含まれます。リファレンス設計はアルゴリズムのビルド先のプラットフォームとして機能し、これによってハードウェア プラットフォームが抽象化されるため、アルゴリズムの開発に専念できます。アルゴリズムの開発が完了したら、HDL Coder を使用してアルゴリズムを IP コアとしてパッケージ化し、リファレンス設計に収めることができます。

ターゲット FPGA に展開するために IP コアを含むビットストリームを生成します。

IP コアおよびビットストリームの生成の例については、MATLAB 関数からの IP コアの生成入門を参照してください。

ターゲット ハードウェアでの IP コアの実行と検証

IP コア設計から生成されたビットストリームをターゲット ハードウェア上で実行、検証します。

ターゲット ハードウェアをホスト マシンに接続して準備します。FPGA とプロセッサを含むプラットフォーム (SoC デバイスなど) を使用する場合は、プロセッサ用の Linux® イメージをダウンロードします。詳細については、Xilinx Zynq® プラットフォームの場合はGuided Hardware Setup for AMD Boards、Intel SoC デバイスの場合はGuided Hardware Setup for Intel Boardsを参照してください。

ホスト マシンからターゲット ハードウェアへの JTAG またはイーサネット接続を確立します。

ターゲット デバイスをプログラムします。

次のいずれかのプロトタイピング方法を使用して、ターゲット ハードウェア上で設計のプロトタイプ作成、デバッグ、検証を行います。

FPGA I/O。HDL ワークフロー アドバイザーによって生成されたホスト インターフェイス モデルまたはホスト インターフェイス スクリプトを使用して、MATLAB および Simulink を実行するホスト PC と FPGA に展開されている生成された IP コアとの間で通信できます。

AXI Manager

FPGA データの取得

FPGA インザループ (FIL)

ソフトウェア インターフェイス モデルの生成 (ソフトウェア インターフェイス用の IP コアの構成を参照)。

例については、Prototype Generated IP Core on Hardware using FPGA I/Oを参照してください。

プロセッサ用の C アルゴリズムの展開

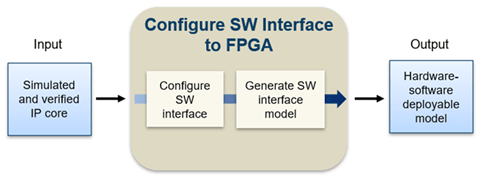

FPGA へのソフトウェア インターフェイスの構成

完全なハードウェア ソフトウェア システムをターゲットにするために、HDL ワークフロー アドバイザーは、元の Simulink モデルからソフトウェア インターフェイス モデルを生成します。ソフトウェア インターフェイス モデルは、ターゲット プラットフォームのオンボード プロセッサに展開するために使用できます。このモデルには、SoC デバイスまたはターゲット プラットフォームに搭載されているプロセッサ用に適切に構成されているデバイス ドライバーが含まれます。SoC デバイスをターゲットにしている場合、このモデルは、ハードウェア ソフトウェア設計に必要な 2 番目のモデルです。最初のモデルは、オンボード FPGA をターゲットにするための HDL アルゴリズムをもつ元のモデルです。このソフトウェア インターフェイス モデルはプロセッサをターゲットにして、プロセッサに展開されているソフトウェアと FPGA に展開されている生成された IP コアの間の通信を行います。

詳細については、HDL IP コアを調査して迅速にプロトタイプを作成するためのソフトウェア インターフェイス モデルの生成を参照してください。

ハードウェア ソフトウェア展開

ソフトウェア インターフェイス モデルから C コード (Embedded Coder® が必要) を生成し、エクスターナル モードまたはプロセッサインザループ (PIL) モードを使用して、ハードウェア ソフトウェア モデルをターゲット ハードウェア上に展開し、実行します。SoC デバイスの展開可能な設計は次で構成されます。

HDL IP コアを含む元のモデルから生成されたビットストリーム。

プロセッサと FPGA 間の通信および組み込みプロセッサの C コード生成が可能となるように構成されたデバイス ドライバーを含むソフトウェア インターフェイス モデル。

ソフトウェア インターフェイス モデルからプロセッサ用に生成された C コードと、IP コアを含む元のモデルからオンボード FPGA 用に生成されたビットストリームに分割された完成した設計を展開すると、SoC または FPGA I/O ボードをもつ Simulink Real-Time ターゲット マシンに搭載されたアルゴリズムを実行できます。

例については、Debug IP Core Using Hardware-Software Deploymentを参照してください。

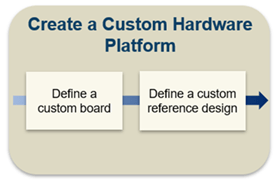

カスタム ハードウェア プラットフォームの作成

ハードウェアで利用できるプラットフォームがまだない場合は、ハードウェア ソフトウェア協調設計ワークフローで使用するカスタム ハードウェア プラットフォームを定義できます。カスタム ハードウェア プラットフォームでは、ハードウェア システムを柔軟に定義して設計を展開できます。たとえば、製品ハードウェアへの展開時にカスタム プラットフォームを定義できます。ハードウェア プラットフォームの作成では、ハードウェアについて記述する新しいボード定義を作成し、ボード用に 1 つ以上の新しいリファレンス設計を作成します。また、既存のボード用に新しいリファレンス設計を作成することもできます。

リファレンス設計により、アルゴリズムの IP コアとハードウェア ボードの間である程度の抽象化が実現するため、ハードウェアに展開するアルゴリズムの設計が容易かつ効率的になります。リファレンス設計はアルゴリズムとハードウェア プラットフォームの間のレイヤーとして機能し、これを使用すると、設計内の特定のハードウェア リソースをモデル化せずにハードウェア内のそのリソースを活用できます。ハードウェアの詳細を実装することなくアルゴリズム設計に専念できます。また、アルゴリズムのターゲットを別のハードウェアに再指定することもできます。たとえば、プロトタイピングに使用する評価ボードから製品ハードウェアに移行する際にアルゴリズム設計のターゲットを再指定できます。

詳細については、ボードおよびリファレンス設計の登録システムを参照してください。