ベンダー固有の FPGA 浮動小数点ターゲット ライブラリの HDL コードの生成

浮動小数点ライブラリにマッピングすることで、浮動小数点を固定小数点に変換せずに浮動小数点設計を合成できます。変換手順をなくすことで、データ精度の損失が低減し、より広いダイナミック レンジのモデル化が可能となります。

FPGA 浮動小数点ライブラリは、特定のターゲット ハードウェアで合成するために最適化される一連の浮動小数点 IP ブロックです。これらのライブラリは、ベンダー固有のハードウェアをターゲットにするため、"ベンダー固有の浮動小数点ライブラリ" とも呼ばれます。Altera® Megafunctions、Xilinx® LogiCORE、AMD® Floating-Point Operators は、これらのライブラリの例です。設計を作成し、HDL Coder™ のネイティブ浮動小数点 (NFP) とベンダー固有の FPGA 小数点 IP で構成されるコードを生成することで、強化された DSP 浮動小数点の加算器や乗算器のプリミティブ型など、FPGA のリソースがより効率的に使用されるようになり、より大きな設計を FPGA ファブリックに当てはめることができます。この混合型の設計は、大規模で複雑なモデルに効果的です。さらに、ベンダー固有のライブラリでサポートされていないブロックを NFP にマッピングし、それ以外のブロックをベンダー ライブラリを使用してベンダー固有の浮動小数点リソースにマッピングすることができます。

モデルは次のいずれかにマッピングできます。

ネイティブ浮動小数点ライブラリ。このオプションが既定のマッピングです。

ネイティブ浮動小数点ライブラリとベンダー固有の浮動小数点ライブラリ。これは "混合モード" のマッピングとも呼ばれます。

ネイティブ浮動小数点ライブラリとベンダー固有の浮動小数点ライブラリの両方にマッピングすると、HDL Coder では可能な限りベンダー ライブラリ IP にマッピングします。その後、ベンダー ライブラリにマッピングできないブロックは、代わりにネイティブ浮動小数点ライブラリ IP にマッピングされます。

FPGA 浮動小数点ライブラリ マッピングをサポートする HDL Coder ブロックのリストを確認するには、FPGA 浮動小数点ライブラリのマッピングに対する HDL Coder のサポートを参照してください。

混合モードのマッピング用の設計の設定

浮動小数点の設計をネイティブ浮動小数点ライブラリと Altera または Xilinx FPGA 浮動小数点ライブラリにマッピングするには、次を行います。

hdlsetuptoolpathを使用して合成ツールの実行可能ファイルへのパスを設定します。たとえば、Altera Quartus II合成ツールへのパスを設定するには、次のように入力します。hdlsetuptoolpath('ToolName','Altera Quartus II','ToolPath',... 'C:\altera\14.0\quartus\bin\quartus.exe');

合成ツールのパスの設定を参照してください。

hdlset_paramを使用して Altera または Xilinx FPGA 合成ツールのターゲット デバイス オプションを設定します。たとえば、合成ツールをAltera Quartus IIとして設定し、チップ ファミリをArria10として設定するには、次のように入力します。hdlset_param(model,'SynthesisToolChipFamily','Arria10', ... 'SynthesisToolDeviceName','10AS066H2F34E1SG', ... 'SynthesisToolPackageName','', ... 'SynthesisToolSpeedValue','')

Altera または Xilinx FPGA 浮動小数点シミュレーション ライブラリを設定します。FPGA シミュレーション ライブラリの設定を参照してください。

ネイティブ浮動小数点ライブラリと FPGA 浮動小数点ライブラリへのマッピング

[コンフィギュレーション パラメーター] ダイアログ ボックスまたはコマンド ラインから Simulink® モデルを浮動小数点ターゲット ライブラリにマップできます。

[コンフィギュレーション パラメーター] ダイアログ ボックスからの浮動小数点ターゲット ライブラリへのマッピング

ネイティブ浮動小数点ライブラリと FPGA 浮動小数点ライブラリにマッピングするには、次を行います。

[アプリ] タブで、[HDL Coder] を選択します。[HDL コード] タブで、[設定] をクリックします。

[HDL コード生成] 、 [浮動小数点] ペインで、[浮動小数点の使用] を選択します。

[ベンダー固有の浮動小数点ライブラリ] パラメーターに、設計用に選択した合成ツールに基づいてオプションが表示されます。Xilinx LogiCORE® IP を使用するには、[ベンダー固有の浮動小数点ライブラリ] を

[XILINXLOGICORE]に設定します。Altera Megafunction IP の場合は、[ベンダー固有の浮動小数点ライブラリ] を[ALTFP]または[ALTERAFPFUNCTIONS]に設定できます。AMD 浮動小数点ライブラリの場合は、[ベンダー固有の浮動小数点ライブラリ] を[AMDFloatingPointOperators]に設定します。メモ

ALTERA FP FUNCTIONS にマッピングする場合、ターゲット言語は VHDL でなければなりません。

hdlcoder.FloatingPointTargetConfigとhdlcoder.FloatingPointTargetConfig.IPConfigオブジェクトを使用して、ベンダー固有の浮動小数点ターゲット ライブラリの IP 設定をカスタマイズできます。詳細については、浮動小数点 IP 構成のカスタマイズを参照してください。浮動小数点 IP リソースを共有するには、[HDL コード生成] 、 [最適化] ペインの [リソース共有] タブで [浮動小数点 IP] を選択します。共有される浮動小数点 IP ブロックの数は、サブシステムで指定する [SharingFactor] によって異なります。

[OK] をクリックします。[HDL コード] タブで、[HDL コードを生成] をクリックします。

コマンド ラインからの浮動小数点ターゲット ライブラリへのマッピング

コマンド ラインから HDL コードを生成するために関数 hdlcoder.createFloatingPointTargetConfig を使用して浮動小数点 IP 構成を作成できます。

関数

hdlcoder.createFloatingPointTargetConfigを使用して、ネイティブ浮動小数点ライブラリとベンダー固有の浮動小数点ライブラリのhdlcoder.FloatingPointTargetConfigオブジェクトを作成します。次に、hdlset_paramを使用して、モデルで構成を保存します。たとえば、ネイティブ浮動小数点ライブラリと

ALTERA FP FUNCTIONSライブラリの浮動小数点ターゲット構成を既定の設定で作成し、その構成をsfir_singleモデルに対して設定するには、次のコマンドを使用します。fpconfig = hdlcoder.createFloatingPointTargetConfig("NativeFloatingPoint",... VendorFloatingPointLibrary="ALTERAFPFUNCTIONS"); hdlset_param('sfir_single', 'FloatingPointTargetConfiguration', fpconfig);

指定する浮動小数点ライブラリに基づいて IP 設定をカスタマイズできます。詳細については、浮動小数点 IP 構成のカスタマイズを参照してください。

関数

makehdlを使用して、DUT サブシステムから HDL コードを生成します。

浮動小数点ライブラリ マッピングのコード生成レポートの表示

浮動小数点ライブラリ マッピングに関する情報をコード生成レポートで確認するには、コード生成を開始する前にリソース利用レポートと最適化レポートを有効にします。これらのレポートの生成方法の詳細は、コード生成レポートの作成と使用を参照してください。

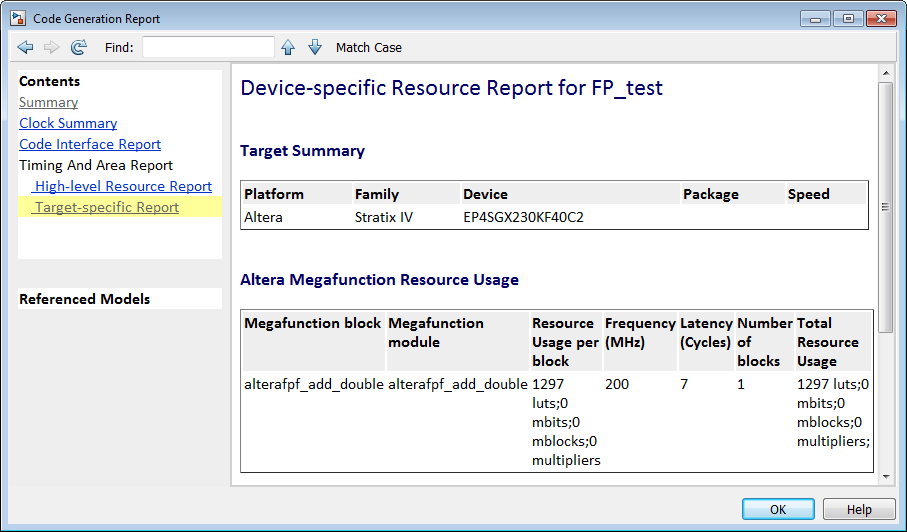

浮動小数点リソース レポート

設計がマッピングされるターゲット浮動小数点ブロック、レイテンシ、およびターゲット固有ハードウェア リソースの数を表示するには、コード生成レポートで [浮動小数点リソース レポート] を選択します。

浮動小数点ライブラリのマッピング結果の解析

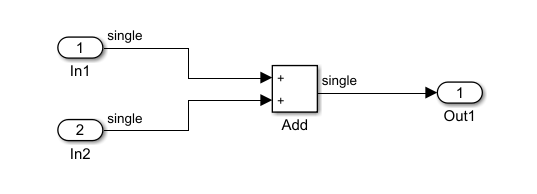

浮動小数点ターゲット IP のレイテンシ情報は、HDL コード生成後に生成されたモデルから取得できます。たとえば、single データ型の入力をもつ次の Simulink の Add ブロックについて考えます。

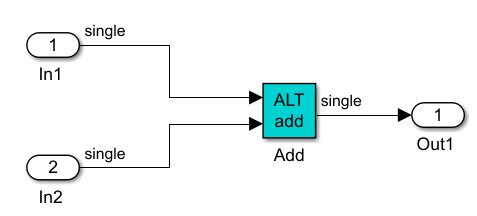

HDL コード生成後、生成されたモデルへのリンクが最適化レポートに表示されます。Simulink ブロックがマッピングされる浮動小数点ターゲット ライブラリを確認するには、生成されたモデルを開き、DUT サブシステムをダブルクリックします。ネイティブ浮動小数点 IP にマッピングされるブロックは薄い青になり、ブロック マスクに

NFPが含まれます。ベンダー固有の浮動小数点 IP にマッピングされるブロックはシアンになり、ベンダー ライブラリに関連付けられた頭文字がブロック マスクに含まれます。この例では、ALTERA FP FUNCTIONSライブラリにマッピングされるブロックの頭文字にALTという頭文字が表示されています。

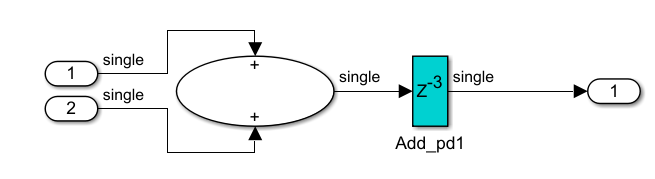

Add ブロックをダブルクリックします。Delay ブロックの長さは、浮動小数点ターゲット IP のレイテンシです。

生成されたモデルの詳細については、生成されたモデルと検証モデルを参照してください。

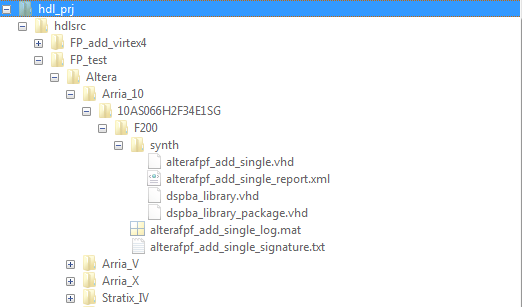

FPGA 浮動小数点ライブラリ マッピングの結果を確認する場合は、HDL コード生成後に生成された IP コア ファイルを表示できます。

HDL Coder は生成された既存の IP コア ファイルをチェックして再利用することで、同じ浮動小数点ターゲット IP のコードを後で生成するときの時間を短縮します。

参考

hdlcoder.FloatingPointTargetConfig | createFloatingPointTargetConfig | hdlcoder.FloatingPointTargetConfig.IPConfig | customize