FPGA 浮動小数点ライブラリ

Altera® および Xilinx® FPGA 浮動小数点ライブラリへのマッピング

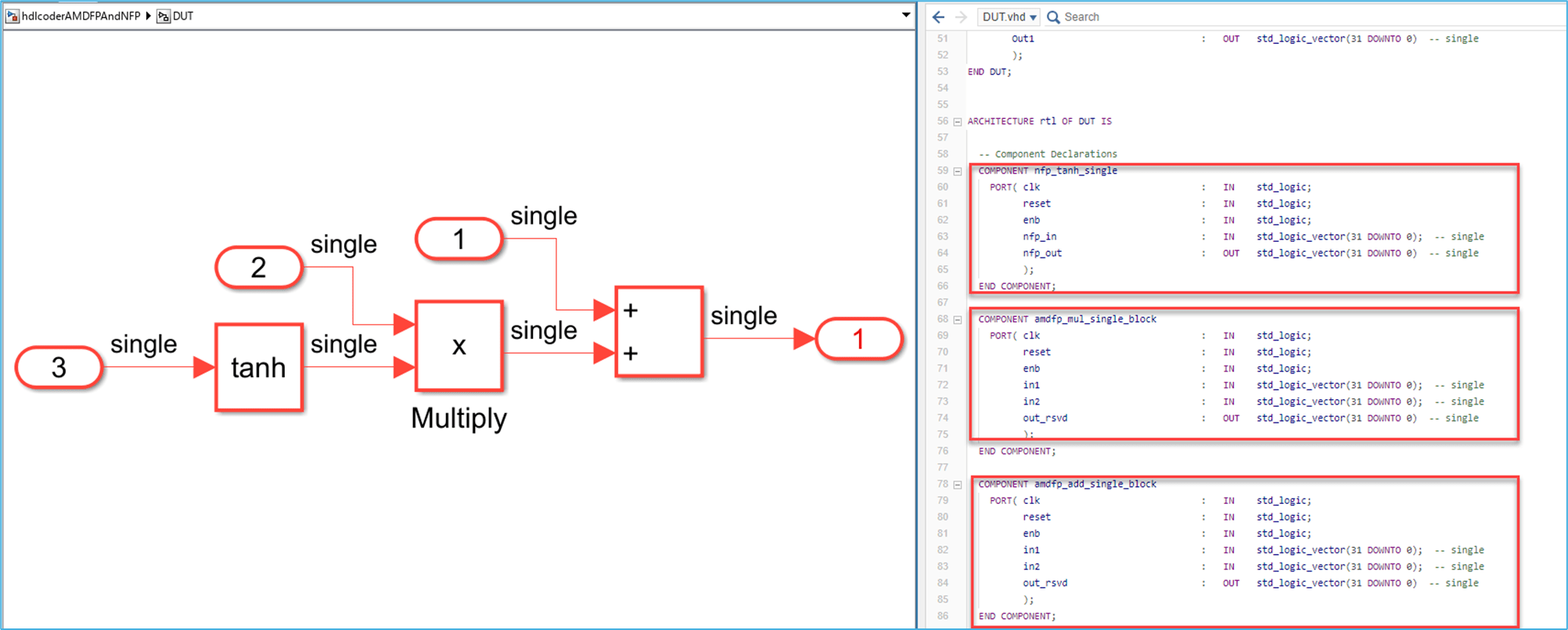

浮動小数点ライブラリにマッピングすることで、浮動小数点を固定小数点設計に変換せずに浮動小数点設計を合成できます。この変換手順をなくすことで、データ精度の損失が低減し、より広いダイナミック レンジのモデル化が可能となります。

モデル設計で Single データ型または Double データ型を使用する場合は、FPGA 浮動小数点ターゲット ライブラリを使用して Simulink® モデルのコードを生成します。HDL Coder™ では、設計をネイティブの浮動小数点ライブラリとベンダー固有の FPGA 小数点ライブラリ (Altera や Xilinx の FPGA 浮動小数点ライブラリなど) にマッピングできます。ネイティブの浮動小数点とベンダー固有の IP を一緒に使用することで、強化された DSP 浮動小数点の加算器や乗算器のプリミティブ型など、FPGA のリソースがより効率的に使用されるようになり、より大きな設計を FPGA ファブリックに当てはめることができます。この混合型の設計は、大規模で複雑なモデルに効果的です。

クラス

hdlcoder.FloatingPointTargetConfig | 浮動小数点ライブラリの浮動小数点ターゲット構成 |

hdlcoder.FloatingPointTargetConfig.IPConfig | IP settings for selected floating-point configuration |

トピック

- ベンダー固有の FPGA 浮動小数点ターゲット ライブラリの HDL コードの生成

HDL コードの Altera および AMD 浮動小数点ターゲット ライブラリ用のセットアップおよび生成方法。

- 浮動小数点 IP 構成のカスタマイズ

浮動小数点 IP ライブラリのレイテンシまたはターゲット周波数のカスタマイズ方法を学習します。

- FPGA 浮動小数点ライブラリのマッピングに対する HDL Coder のサポート

浮動小数点ターゲット ライブラリへのマッピングにおいて Simulink でサポートされるブロックを説明します。